生成式人工智能已经在各个行业掀起波澜,其潜力不断扩大。

所以我们今天再为大家介绍一个实例。比如在其众多应用中,一个特别有趣的领域是生成式AI 解释数字设计波形并在调试过程中充当硬件工程师辅助的能力。

在本文中,我们将探讨这项技术带来的令人着迷的可能性及其对芯片开发领域的影响。

实验 2:解释设计波形

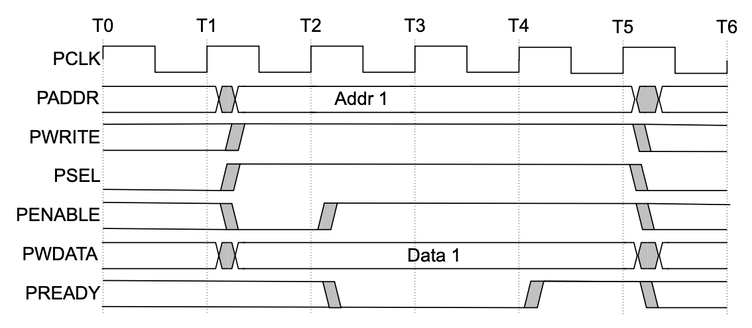

这个实验展示了生成式人工智能识别数据模式和趋势的能力,并彻底改变了我们理解波形和与波形交互的方式。在本实验中,Google 的生成式 AI 模型 – BARD 用于通过查看示例波形来生成符合 AMBA APB 协议的系统中写入传输的解释 。

具有等待状态的写传输

生成的解释(进行调整以使其语言具有包容性):

图中的波形显示以下信号:

TCLK:APB3 时钟信号。

PADDR:APB3 地址总线。

PWRITE:APB3 写信号。

PSEL:APB3片选信号。

PENABLE:APB3 使能信号。

PWDATA:APB3 写数据总线。

PREADY:APB3 就绪信号。

数据 1:正在写入 APB3 完成器器件的数据。

波形显示以下行为:

在时间 T1,PWRITE 信号变高,PADDR 总线由要写入的 APB3 完成器器件的地址驱动。

在时间 T2,PSEL 信号变高。这表明 APB3 发起方已准备好将数据传输到完成方设备。

在时间 T3,PENABLE 信号变高。这表明 APB3 启动器已准备好驱动 PWDATA 总线。

在时间 T4,PREADY 信号变高。这表明 APB3 完成器器件已准备好接收 PWDATA 总线上的数据。

在时间 T5,PWRITE 信号变低。这表明 APB3 发起方已完成向完成方设备传输数据。

PSEL 和 PENABLE 信号保持高电平,直到 APB3 完成器器件完成数据处理。

未来会是什么样子 – GenAI 支持的调试器 Copilot

生成式人工智能最令人兴奋的应用之一是它有可能在调试过程中成为开发人员的强力助手。波形是硬件设计中复杂系统的命脉。

由生成式 AI 提供支持的调试器可以剖析波形、识别异常并关联模式,这使其成为寻求理解复杂设计行为的工程师的宝贵工具。

开发调试器 Copilot 的挑战

虽然由生成式人工智能驱动的调试器副驾驶的前景很诱人,但仍有一些挑战需要解决。人工智能解释的准确性和可靠性至关重要。我们必须确保人工智能的见解是值得信赖的,而不仅仅是算法生成的响应。

此外,隐私和数据安全问题也很重要。在调试过程中处理敏感信息需要一个强大的框架来保护数据完整性。

-

人工智能

+关注

关注

1813文章

49733浏览量

261390 -

AMBA

+关注

关注

0文章

70浏览量

15911 -

调试器

+关注

关注

1文章

325浏览量

24919 -

AI芯片

+关注

关注

17文章

2062浏览量

36558 -

生成式AI

+关注

关注

0文章

536浏览量

1013

发布评论请先 登录

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片到AGI芯片

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI的科学应用

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片的需求和挑战

【「AI芯片:科技探索与AGI愿景」阅读体验】+可期之变:从AI硬件到AI湿件

智能体化AI和生成式AI的区别

生成式 AI 重塑自动驾驶仿真:4D 场景生成技术的突破与实践

聚云科技获亚马逊云科技生成式AI能力认证

聚云科技荣获亚马逊云科技生成式AI能力认证

聚云科技荣获亚马逊云科技生成式AI能力认证 助力企业加速生成式AI应用落地

国内生成式AI备案数量突破300款

安霸发布N1-655前端生成式AI芯片

Google两款先进生成式AI模型登陆Vertex AI平台

Imagination 系列研讨会 |中国生成式 AI 的发展

用生成式AI设计芯片—解读时序图

用生成式AI设计芯片—解读时序图

评论