前言

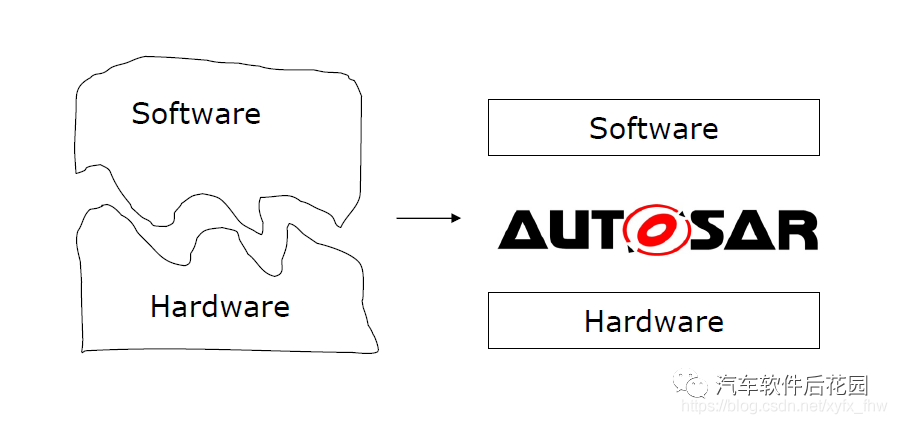

随着汽车ECU迅速的往域控制器方向发展,ECU要处理的任务越来越多,单核CPU的负载越来越大,多核ECU势在必行。AUTOSAR架构下OS支持多核处理,本系列文章将详细介绍AUTOSAR架构下的多核机制。本文介绍AUTOSAR架构下的多核通信。

问题 1: 什么是共享内存(Shared Memory),共享内存需要在链接文件中特别指定吗?

问题 2:如果要指定共享内存,该怎么指定?

问题3: 用于多核通信的共享内存一定需要使用SpinLock进行一致性保护吗?

问题4: 如何确保单核中的数据一致性?

参考文档:

AUTOSAR架构下多核启动

AUTOSAR架构下多核Shutdown

TC3xx芯片MPU介绍

MPU功能详解-以RH850U2A为例

缩略词

| 简写 | 全称 |

| IOC | Inter-OS-Application Communicator |

注:本文章引用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

1.多核通信介绍

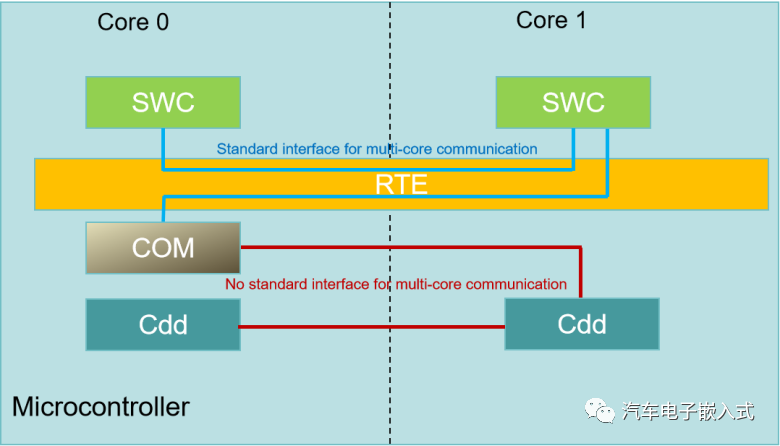

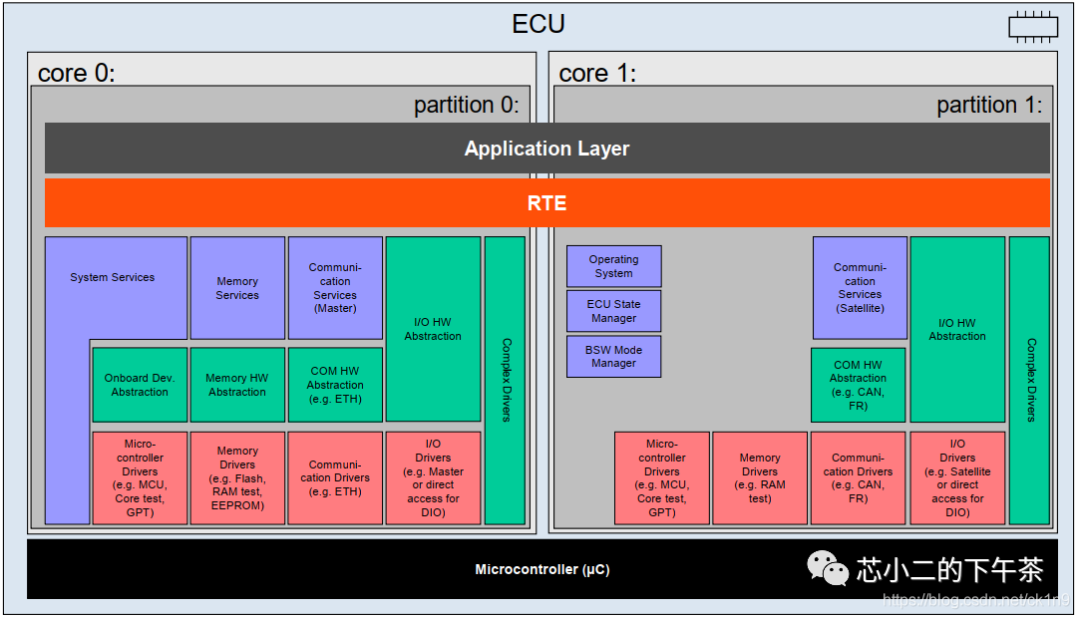

使用多核的ECU避免不了需要考虑跨核通信,如下图所示,跨核通信时使用RTE进行跨核通信时,AUTOSAR定义了标准的IOC通信,用户只需要配置SWC的端口接口进行Mapping,IOC的具体实现由RTE/OS自动实现,不用用户再做其他的操作。如果不使用RTE进行多核通信,没有标准的接口可以使用,需要用户自定义跨核通信,着重需要考虑跨核通信的共享内存及数据一致性保护。

Figure 1: 多核通信

2.多核间标准通信

多核间通信一定是跨OS-Application的通信(OS-Application不能跨核,所以两个不同核上的SWC一定隶属于不同的OS-Application),而“IOC”负责操作OS-Application之间的通信,特别是跨越核或内存保护边界的通信。

2.1 什么是IOC

IOC全称为Inter-OS-Application Communication,专门用于跨OS-Application的通信方式,特别的,跨越核或内存保护边界的通信一般都使用IOC通信。

2.2 IOC的适用范围

IOC的具体实现由RTE和OS实现,所以,IOC只适用于通过RTE交互的SWC间的跨OS-Application的通信,或通过RTE交互的SWC和BSW跨OS-Application通信,或者通过RTE交互的CDD和SWC或者CDD和CDD间的跨OS-Application通信。总之,不经过RTE的通信不适用IOC通信。

2.3 IOC的通信种类

IOC不支持Client-Server的通信,只支持Sender-Receiver的通信方式,SWC间的Client-Server通信在RTE/OS的具体实现中转变为 Sender-Receiver的通信方式。也就是说对于SWC的开发者来说,不用做任何的更改,C-S的接口依然可以继续使用。

从IOC的Senders和Receivers个数来分:IOC支持1:1, N:1, N:M的通信方式。

从是否带Notification的角度来分:IOC分为带Notification和不带Notification的通信方式。

IOC通信支持队列缓存(queue buffer),1:1和N:1通信方式支持队列,N:M通信方式不支持队列,1:1的通信方式一般不使用队列,N:1通信方式一般使用队列。

2.3 IOC通信配置

两个SWC如果使用IOC通信的话,接口配置和不使用IOC通信完全一样。

配置Data Type

配置Interface

配置P-port和R-Port

进行P-port和R-port连接(Mapping)

不过,两个SWC如果要使用IOC跨核(跨OS-Application)通信,这两个SWC的Runnable所在的Task一定时归属于两个核上的不同OS-Application,这样进行Port连接后,RTE和OS会自动为两个SWC生产IOC通信接口和具体实现。

2.4 IOC通信的共享内存和数据保护

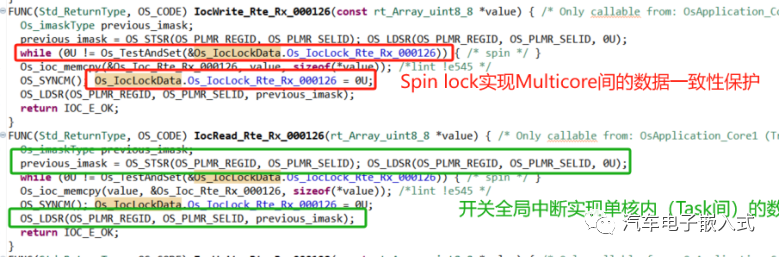

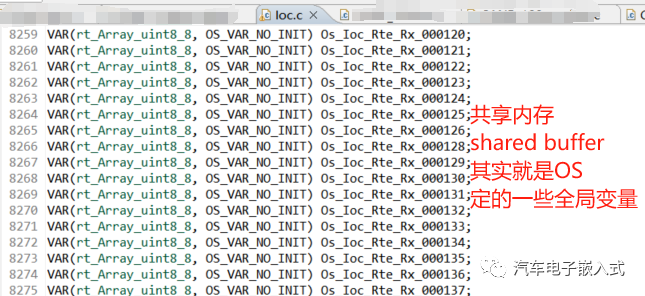

IOC通信的具体实现由共享内存的方式实现,共享内存的跨核间数据一致性保护由Spin lock保证,共享内存的核内Task间的数据一致性保护由开/关全局中断的方式保证。共享内存和数据一致性保护都由OS来自动生成和保证。

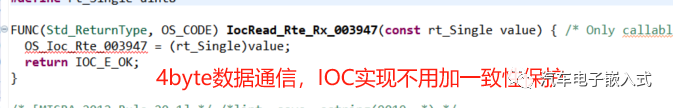

Note: 如果IOC通信间的数据长度小于等于4 Bytes,那么RTE/OS不会为其生成Spin lock和开关中断的配置代码,因为32bit的MCU的一次机器周期操作能完成4字节数据的操作,保证了数据的原子操作。

2.5 IOC通信需要注意的其他点

单核内如果存在多个OS-Application,且OS-Application间由内存保护的边界(boundaries

),这种单核场景也适用IOC通信。

在只有一个Core的系统中,如果只有一个OS-Application,或者如果没有OS-Application使用内存保护机制,那么IOC可以被完全省略。

带Notification的IOC适用二类中断ISR来通知Receivers数据已经到达shared buffer,能保证Receiver及时的取得数据。

2.6 IOC通信的示例

2.6.1 SWC间通过S-R方式1:1通信且没有Notification

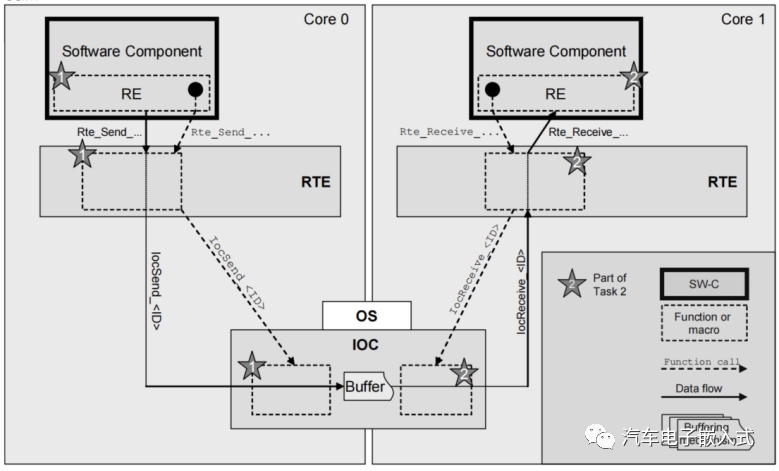

如图2所示,Core 0上的SWC通过RTE接口给Core 1上的SWC发送数据。接收端的可运行实体被定期调用(调度表或者Alarm机制实现),并通过RTE接收数据。

由于通信跨越了核心边界,RTE调用IOC将数据从Core0传输到Core1。

数据发送方调用

Rte_Send_

Rte_Write_SWC_PortName(VAR(rt_Array_uint8_8, AUTOMATIC) data) /* 2 */

{

VAR(Std_ReturnType, AUTOMATIC) rtn;

rtn = ((VAR(Std_ReturnType, AUTOMATIC))RTE_E_OK);

(void)IocWrite_Rte_Rx_000139(data);

return rtn;

}

RTE将其mapped 到

IocSend_

FUNC(Std_ReturnType, OS_CODE) IocWrite_Rte_Rx_000139(const rt_Array_uint8_8 *value)

{

Os_imaskType previous_imask;

previous_imask = OS_STSR(OS_PLMR_REGID, OS_PLMR_SELID); OS_LDSR(OS_PLMR_REGID, OS_PLMR_SELID, 0U);

while (0U != Os_TestAndSet(&Os_IocLockData.Os_IocLock_Rte_Rx_000139)) { /* spin */ }

Os_ioc_memcpy(&Os_Ioc_Rte_Rx_000139, value, sizeof(*value)); /*lint !e545 */

OS_SYNCM(); Os_IocLockData.Os_IocLock_Rte_Rx_000139 = 0U;

OS_LDSR(OS_PLMR_REGID, OS_PLMR_SELID, previous_imask);

return IOC_E_OK;

}

Figure 2: IOC without notification

在本例中,IocSend服务将数据写入一个缓冲区,该缓冲区位于一个共享内存区中,接收方可以通过IOC读取该数据。在接收端,接收可运行程序被定期调用。

Rte_Receive_

Rte_Read_SWC_PortName(CONSTP2VAR(rt_Array_uint8_8, AUTOMATIC, RTE_APPL_DATA) data) { VAR(Std_ReturnType, AUTOMATIC) rtn; (void)IocRead_Rte_Rx_000139(((P2VAR(rt_Array_uint8_8, AUTOMATIC, RTE_APPL_DATA))data)); rtn = Rte_Rx_000139_status; return rtn; }

RTE将其mapped 到

IocReceive_

调用以从IOC内部队列中读取数据。1:1通信不需要RTE中的附加队列。

FUNC(Std_ReturnType, OS_CODE) IocRead_Rte_Rx_000138(rt_Array_uint8_8 *value) {

Os_imaskType previous_imask;

previous_imask = OS_STSR(OS_PLMR_REGID, OS_PLMR_SELID); OS_LDSR(OS_PLMR_REGID, OS_PLMR_SELID, 0U);

while (0U != Os_TestAndSet(&Os_IocLockData.Os_IocLock_Rte_Rx_000139)) { /* spin */ }

Os_ioc_memcpy(value, &Os_Ioc_Rte_Rx_000138, sizeof(*value)); /*lint !e545 */

OS_SYNCM(); Os_IocLockData.Os_IocLock_Rte_Rx_000139 = 0U;

OS_LDSR(OS_PLMR_REGID, OS_PLMR_SELID, previous_imask);

return IOC_E_OK;

}

这种无通知的端口对端口通信适用于:

Sender/Receiver通信

队列或者非队列通信

1:1通信方式

2.6.2 SWC间通过C-S方式通信有Notification

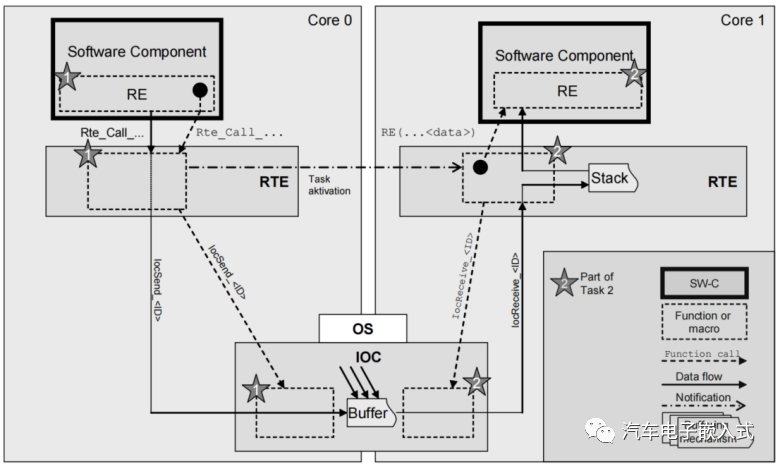

当数据写入IOC内部数据缓存后,Rte函数调用OS的服务来激活接收任务。这种通信方式适用于:

带Notification的SWC间的Sender/receiver通信;

Client/server通信。

队列或非队列通信;

非polling模式的1:1通信;

N:1通信。

Figure2: IOC with notification by RTE

用长度为100的队列方式实现。

Std_ReturnType IocReceive_Rte_Rx_000022(uint8* value)

{

*value = Os_Ioc_Rte_ Rx_000022[read_index];

read_index = (read_index == 100)? 0 : (read_index + 1U);

return E_OK;

}

Std_ReturnType IocSend_Rte_Rx_000022(uint8 value)

{

If ((read_index == 0 && write_index == 100)|| (read_index-write_index==1)) {

return IOC_E_FULL;

} else {

Os_Ioc_Rte_ Rx_000022[write_index] = val;

write_index = (write_index == 100)? 0 : (write_index + 1U);

Os_SetEvent(EventID);

}

}

3.多核间非标准通信

从第2章节得知:

IOC通信的的共享内存也就是OS定义的全局变量

对共享内存的数据一致性保护也就是通过Spin Lock和开关中断来实现,

共享内存小于等于4 bytes,可以不使用Spin Lock和中断保护

如果没有开启内存保护(MPU),共享内存可以分配在.default段(不用特别的去修改链接文件定义特殊的段),也就是任意可访问RAM地址

只不过这些都由RTE和OS自动实现,对于用户只要做好Port连接即可。

那么对于不经过RTE的多核通信,我们是否可以自己实现多核通信了?-- 肯定是可以的,下面我就列出一些多核通信的场景及应该考虑的地方。

| 序号 | 两个跨核SWC所在OS-Application情况 | 通信数据长度 | 共享内存 | 数据一致性保护 |

| 1 | Core0-SWC和Core1-SWC所在OS-Application都无内存保护机制 | 小于等于4 Bytes(32-bit MCU) | 不用在链接文件特殊定义共享内存段,直接使用.default Data段 |

不用spin lock保护; 不用开关全局中断保护 |

| 2 | Core0-SWC和Core1-SWC所在OS-Application都无内存保护机制 | 大于4 Bytes(32-bit MCU) | 不用在链接文件特殊定义共享内存段,直接使用.default Data段 |

需要spin lock保护; 如果该Shared buffer同一个核中不同Task间读写情况,就需要开关全局中断保护。 |

| 3 | Core0-SWC和Core1-SWC所在OS-Application有内存保护机制 | 小于等于4 Bytes(32-bit MCU) | 需要在链接文件定义两个OS-Application都能访问的共享内存段 |

不用spin lock保护; 不用开关全局中断保护 |

| 4 | Core0-SWC和Core1-SWC所在OS-Application有内存保护机制 | 大于4 Bytes(32-bit MCU) | 需要在链接文件定义两个OS-Application都能访问的共享内存段 |

需要spin lock保护; 如果该Shared buffer同一个核中不同Task间读写情况,就需要开关全局中断保护。 |

关于MPU请参考:

TC3xx芯片MPU介绍

4.总结

问题 1: 什么是共享内存(Shared Memory),共享内存需要在链接文件中特别指定吗?

答:两个或多个OS-Application都能访问的内存区域即为共享内存区域。如果没有使能MPU内存保护机制,任意定义的全局变量即为共享内存变量。如果使能了MPU内存保护机制,就需要在链接文件中定义共享内存段,同时需要配置MPU保护段并分配给OS-Application。

问题 2:如果要指定共享内存,该怎么指定?

答:在链接文件中指定一块内存区域,然后配置MPU设置其读写访问属性,需要多核通信的OS-Application应该包括该MPU配置即拥有对该共享内存的读写访问权限。

问题3: 用于多核通信的共享内存一定需要使用Spin Lock进行一致性保护吗?

答:不一定。当多核通信的数据小于等于4 Bytes(32-bit MCU)时CPU一个机器周期就能完成数据的读写,已经是原子操作,不用使用Spin lock进行数据一致性保护。

问题4: 如何确保单核中的数据一致性?

答:使用开关/挂起全局核内全局中断。

-

负载

+关注

关注

2文章

675浏览量

36720 -

通信

+关注

关注

18文章

6450浏览量

140270 -

AUTOSAR

+关注

关注

11文章

407浏览量

23754 -

ecu

+关注

关注

14文章

993浏览量

57489

原文标题:AUTOSAR架构下多核通信

文章出处:【微信号:汽车电子嵌入式,微信公众号:汽车电子嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AUTOSAR架构深度解析 精选资料分享

AUTOSAR架构下的WdgDriver WdgIf WdgM模块

AutoSAR构架以及在多核汽车MCU的运行

基于Tricore芯片的AUTOSAR架构下的多核启动

AUTOSAR架构下,持续集成CI的最佳实践

AUTOSAR架构下的多核通信介绍

AUTOSAR架构下的多核通信介绍

评论