运放中容性负载该怎么处理?

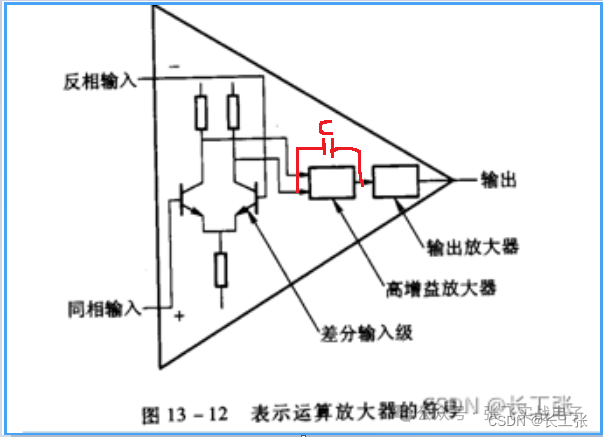

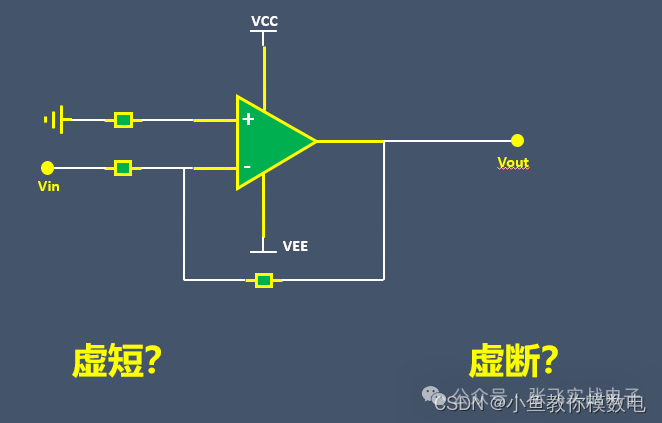

运放(放大器)是电子电路中常用的一种器件,用于放大电压、电流或功率信号。在运放的输出端接入负载时,可能会导致容性负载的问题。容性负载指的是输出端接入具有一定容量的电容。本文将详细介绍如何处理运放中的容性负载问题。

首先,容纳性负载对运放的性能产生了一定的影响。在运放中,电容负载会导致许多问题,如幅频响应下降、阶跃响应不稳定、相位延迟、共模电压偏移等。因此,我们需要一些策略来解决这些问题。

要解决容性负载问题,首先需要选择合适的运放。不同的运放具有不同的负载能力和适用范围。通常,高带宽运放对容性负载具有更好的稳定性。因此,在设计电路时,应选择具有足够带宽的运放来应对容性负载。

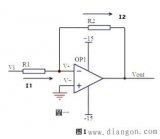

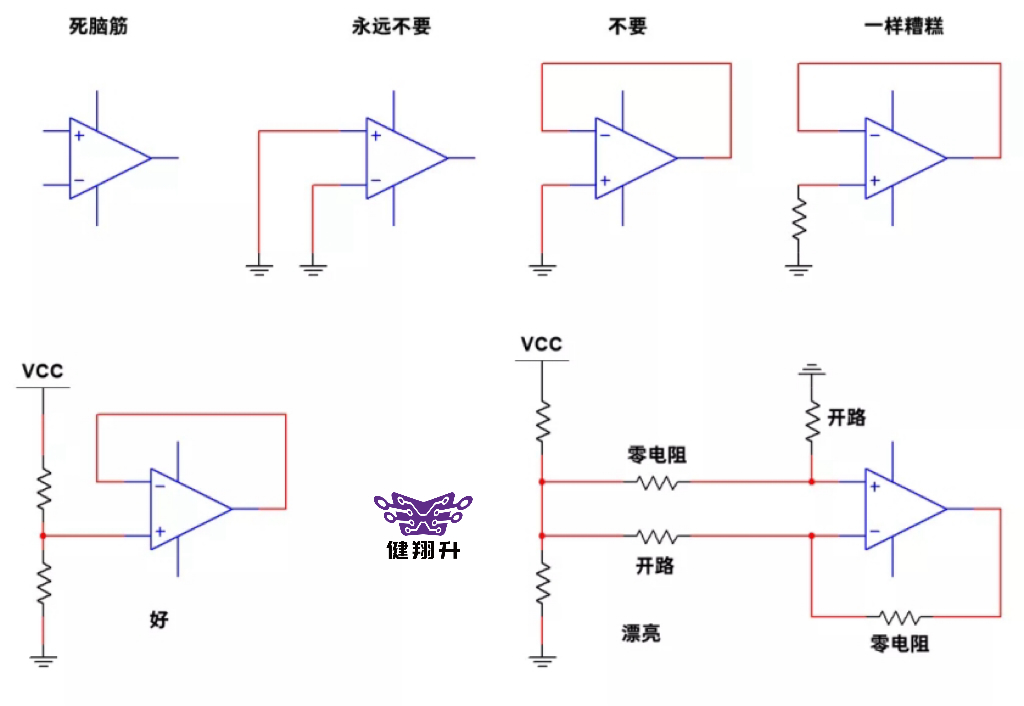

其次,我们可以使用补偿电路来解决容性负载问题。补偿电路是一种用于改善运放性能的辅助电路。在容性负载情况下,补偿电路可以提供额外的稳定性和线性性能。其中一种常见的补偿技术是添加补偿电容。补偿电容与负载电容并联,通过改变电路的频率响应来抵消容性负载的影响。通过合理选择补偿电容的数值,可以达到使运放在容性负载下仍保持稳定输出的效果。

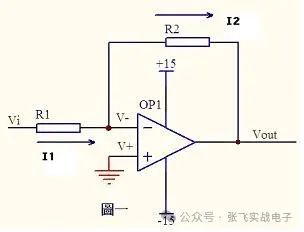

另外,使用外部电路来改善运放的容性负载能力也是一种解决方案。常见的方法是使用电流放大器来驱动负载。电流放大器可提供更大的输出电流能力,从而改善运放在容性负载下的性能。此外,还可以通过并联电阻方式来改善运放输出阻抗,从而提高对容性负载的驱动能力。

此外,当容性负载变化范围较大时,我们还可以尝试使用自适应补偿技术。自适应补偿技术可以根据负载的变化自动调整补偿电容和其他参数,以确保稳定的运放性能。这种技术一般需要使用微处理器或其他控制电路来实现,对于设计复杂的系统可能比较适用。

在实际应用中,如果电路允许,我们还可以通过增加供电电压来提高运放的驱动能力。然而,此方法可能会引入其他问题,如功耗增加、热量产生等,需要综合考虑。

总之,处理运放中的容性负载问题需要综合考虑多方面的因素。在设计中选择合适的运放、使用补偿电路、增加输出电流能力以及应用自适应补偿技术等,都是解决容性负载问题的常用方法。然而,需要根据具体的应用场景和需求来选择最合适的解决方案。

希望以上内容可以帮助您对运放中容性负载问题有更全面的了解。如有任何问题,请随时向我提问。

-

补偿电路

+关注

关注

2文章

81浏览量

28469 -

运放放大器

+关注

关注

0文章

8浏览量

4222

发布评论请先 登录

运放中接电阻的作用

opa2604在应用于dac7541时,驱动功率不够,容性负载影响严重怎么解决?

轨到轨运放与一般运放的区别

运放中接电容有什么作用

运放中容性负载该怎么处理?

运放中容性负载该怎么处理?

评论