对于高速TIA的PCB来说,最大的挑战就是如何减小杂散电容Cstray了 。这是为什么呢?假如带宽很高,增益很高,那么Cf可能需要设置在如0.5pF,而普通贴片电阻的杂散电容就有0.1pF。

如果未经任何处理,那么跨阻自身的电容就会吃掉20%的带宽!我们这里只讨论跨阻的Cstray,其实还有求和节点的Cstray,它可能也会吃掉带宽和增加噪声等。

最近刚好做TIA的PCB,在LTC6268 和LTC6268-10的数据手册中,学到了一种非常有效地减小RF的杂散电容的方法,至少从他们的实验数据看是这样的。本文就是针对这种方法的介绍。

一、通过实验数据直观感受该方法的有效性

我把LTC6268 和LTC6268-10数据手册中的实验数据,用图表重新做了整理,可以更直观展示该方法在减小Cstray上面的效果。

1.1 LTC6268数据手册中的数据展示

表1 LTC6268是否实施了该方法的杂散电容对比

简单说下他们的测试方法。LTC6268数据手册的数据是这样测试出的,测试电路参见图1,跨阻为499K,没有加Cf。在这个电路中,GBW没有限制带宽,所以该电路的带宽可以认为完全是由跨阻自身的杂散电容导致的,它减小了高频增益。在激发PD的激光器驱动器上施加不同频率的正弦波,测试TIA输出的频率响应,可以间接得到跨阻的杂散电容,频响参见图2和图3。

图1 LTC6268测试减小Cstray方法有效的测试电路

图2 无特殊处理图1电路的频响,f-3dB=2.5Mhz,通过TIA信号带宽公式1/(2piRC)可以得到此时的Cstray=0.13pF

图3 特殊处理了图1电路的频响,f-3dB=11.2Mhz,通过TIA信号带宽公式1/(2piRC)可以得到此时的Cstray=0.0271pF

1.2 LTC6268-10数据手册中的数据展示

表2 LTC6268-10是否实施了该方法的杂散电容对比

这里简单说下表3数据的测试方法。测试电路参见图4,跨阻为499K(0805封装),没有加Cf。在这个电路中,GBW没有限制带宽,所以该电路的带宽完全是由跨阻自身的杂散电容导致的,它减小了高频增益。

他们是如何测试出跨阻的Cstray呢?通过测试该电路的阶跃响应即可,施加给激光器一个脉冲信号,它的Tr非常小,比如1ns,小于输出的Tr才行。测试TIA输出的脉冲信号Tr,利用BW=0.35/Tr间接得到带宽,就可以间接得到Cstray。

通过阶跃响应(包括LTC6268的频域响应)也可以间接看到,放大器自身的GBW并没有限制TIA的带宽,带宽主要是由于跨阻的Cstray限制的。如果放大器自身的GBW不够,阶跃响应或者频率响应是可以看到震荡迹象的,因为PD有结电容( 这个结电容是分析TIA电路的关键 )。

图4 LTC6268-10测试减小Cstray方法有效的测试电路

图5 无特殊处理图4电路的阶跃响应,Tr=87ns,BW=4Mhz(BW=0.35/Tr),通过TIA信号带宽公式1/(2*pi*RC)可以得到此时的Cstray=0.1pF

图6 特殊处理了图4电路的阶跃响应,Tr=10.3ns,BW=34Mhz(BW=0.35/Tr),通过TIA信号带宽公式1/(2*pi*RC)可以得到此时的Cstray=11.6fF

二、电阻杂散电容的计算与影响因素

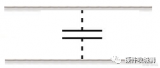

在介绍该layout方法之前,我们再简单了解下跨阻自身的杂散电容,通过图6即可看到如何计算,以及哪些因素会影响它的大小。

图7 跨阻自身寄生电容的由来

这里有个疑惑。通过表3可以看到,0805电阻的杂散电容跟0603的差不多,甚至还小了0.03pF,这跟图6的公式不符合啊?因为0805的焊盘比0603更宽,也就是公式中的l更大,那么为啥它会更小呢?我暂时也不太理解,可能是测试电路的缘故吧,因为TIA的信号带宽不能完全归咎于跨阻的Cstray,这是不公平的。

表3 两种封装跨阻的Cstray

三、减小高速TIA跨阻Cstray的方法

那么,他们是用了什么魔法,这么有效地减小了跨阻的Cstay呢?其实操作也很简单,参见图7,上面也有原理介绍,就是中间的地线屏蔽了电场。具体的PCB操作参见图8。需要注意的是,跨过电阻中间的这条地线尽量靠近Vout节点,这样也是为了减小求和节点的电容。

图8 一种减小高速TIA跨阻Cstray的方法

图9 具体PCB操作(减小跨阻杂散电容的方法不是覆铜,而是在跨阻两个焊盘之间走地线)

四、减小高速TIA跨阻Cstray的另一种方法

减小跨阻的杂散电容的方法还有另外一种,参见图6,即一个跨阻拆分成两个等值的电阻串联。无论如何,这种方法都能够减小1/2的Cstray,因为串联两个等值的电容,总电容等于它的一半。图8中,他们用了前面介绍的方法,减小了还不到一半。但是这种方法也有弊端,会增加TIA布板面积,PD距离求和节点也会距离变远等。

图10 减小跨阻杂散电容的另一种方法,串联跨阻

总结一下,本文介绍了高速TIA电路布板的重点在于减小杂散电容,以及原因。数据展示了LTC6268 和LTC6268-10手册介绍的减小Cstray方法的有效性,以及如何实践。还介绍了另一种减小Cstray的方法。

-

驱动器

+关注

关注

54文章

9012浏览量

153325 -

正弦波

+关注

关注

11文章

657浏览量

58321 -

杂散电容

+关注

关注

0文章

18浏览量

1550 -

LTC6268

+关注

关注

0文章

4浏览量

3057 -

PCB

+关注

关注

1文章

2264浏览量

13204

发布评论请先 登录

PCB杂散电容大小计算方法 PCB杂散电容怎么消除

高速TIA如何减小杂散电容Cstrayne ?

高速TIA如何减小杂散电容Cstrayne ?

评论