两种方法: 时域和频域测试,如下:

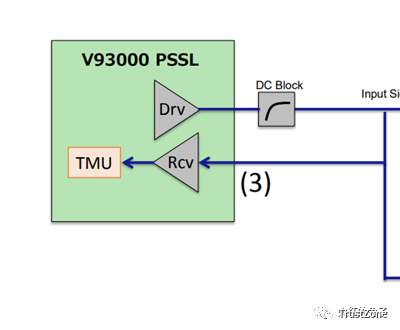

•方法1. ATE time measurement unit ( TMU)测试。(时域,需要额外的TMU license,因此常不采用。)

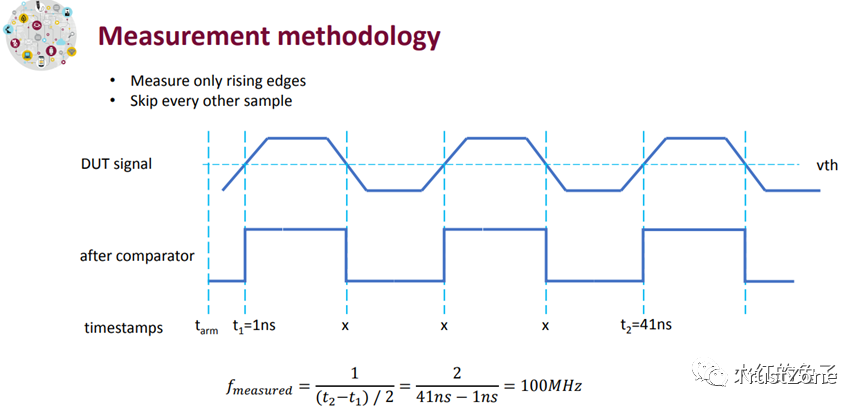

实施步骤:ATE 构造TMU TASK。TMU可以非常高精度地根据task设置trigger到上升沿的时刻,因此可以通过两个上升沿的差值计算出频率,支持多次采样,如下图所示:

•方法2. 构造采样向量,离散傅里叶公式计算频谱,频谱的最大和第2大频率转换即为待测信号频率。(频域)

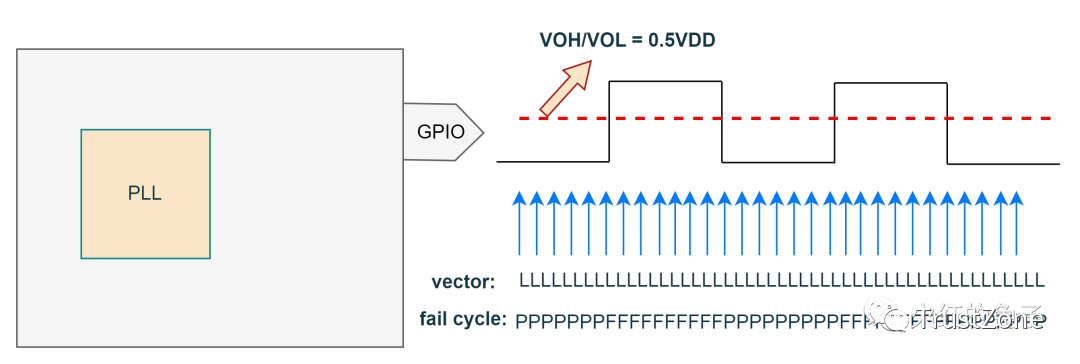

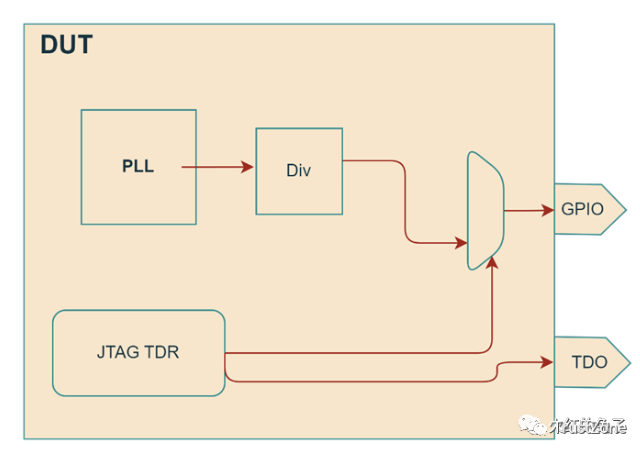

•a)预先构造一条全L的向量,假设叫做PLL_sample.

•b) 运行DFT PLL向量的测试项。运行后, 不复位的情况下DUT此时稳定输出时钟信号。

•c) 运行预先构造好的向量PLL_sample,收集fail cycle,也就是ATE的error

map。获得一串0/1组成的一维序列,如下图(点击可放大):

•d)。对获得一维序列进行汉明窗口卷积后,使用快速离散傅立叶变换获得频谱。通过频谱可以相当高精度的获得输出的频率,通过spec进行分bin。

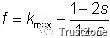

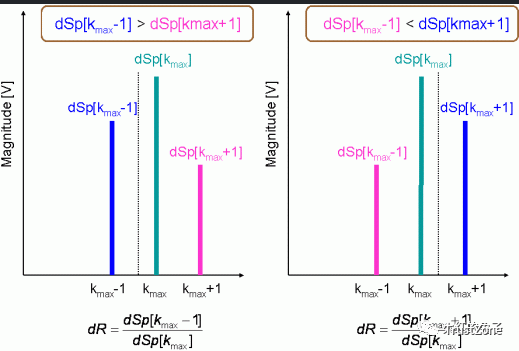

实际步骤:首先应用DSP_FFT与汉明窗口。然后搜索频谱第一大主频kmax 和第二大频,(kmax-1 或者kmax+1)。如图所示,第1大和第2大频率成为关键参数。

核心为两个公式:

-

测试

+关注

关注

8文章

6027浏览量

130708 -

IC

+关注

关注

36文章

6258浏览量

184211 -

pll

+关注

关注

6文章

976浏览量

137580 -

ATE

+关注

关注

6文章

168浏览量

27763

发布评论请先 登录

AMD(苏州)招聘ATE测试工程师和懂ATE测试的产品工程师。

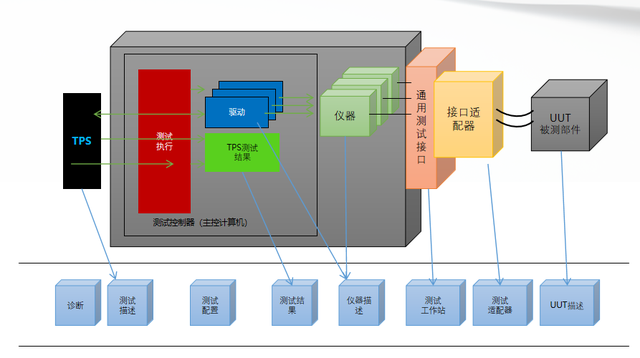

ATE自动化测试系统是什么_ATE自动化测试系统介绍

在ATE测试中,需要注意哪些事项呢?

芯片的出厂测试与ATE测试的实施方法

ATE如何测试PLL

ATE如何测试PLL

评论