对于波形和电平不标准的时钟信号一般应进行怎样的处理?

时钟信号是数字系统中非常重要的信号之一,它用于同步各种数字电路的操作,以确保正确的数据传输和处理。然而,在现实应用中,时钟信号的波形和电平往往不够标准,这可能导致系统性能下降或故障。因此,我们需要对这种情况进行适当的处理。

对于波形和电平不标准的时钟信号,一般应进行以下处理:

1. 时钟信号滤波

波形和电平不标准的时钟信号往往会出现抖动或噪声,这会对数字系统的稳定性和可靠性产生负面影响。因此,我们可以通过滤波的方式对时钟信号进行处理,减少其噪声和抖动。滤波的选择和参数需要根据具体的情况进行确定,常见的滤波方法包括低通滤波、中通滤波和高通滤波等。

2. 时钟信号重整

在一些情况下,时钟信号可能会出现频率偏差或相位偏移,导致信号的时序不准确。这种情况下,我们可以使用时钟信号重整技术,对时钟信号进行重新定时,使其满足系统要求的时序特性。常见的时钟信号重整技术包括锁相环(PLL)和延迟锁定环(DLL)等。

3. 恢复时钟信号

在某些情况下,时钟信号可能会被丢失或干扰,这会导致数据传输中断或出错。因此,我们需要使用恢复时钟信号的技术,对时钟信号进行重构,以确保正常的数据传输。常见的恢复时钟信号技术包括自适应等化器和时钟恢复电路等。

4. 时钟信号干扰分析与解决

在实际应用中,时钟信号可能会受到其他信号的干扰,例如电源噪声、信号泄漏等。这种干扰会导致时钟信号的波形和电平不规范,进而影响系统的性能。因此,我们需要通过干扰分析和解决技术,对干扰因素进行识别和消除,以确保时钟信号的正常运行。干扰分析和解决技术包括电磁兼容性设计、屏蔽技术、地线设计等。

5. 时钟信号优化设计

在数字系统设计过程中,时钟信号的选择、布线和优化设计对系统性能至关重要。因此,我们需要进行适当的时钟信号优化设计,以确保时钟信号的正确性、稳定性和可靠性。常见的优化设计技术包括时钟路线设计、时钟延时优化、时钟功耗优化等。

综上所述,对于波形和电平不标准的时钟信号,我们需要进行多方面的处理和优化设计,以确保系统的稳定性和可靠性。这需要我们掌握一定的电子信号处理和数字系统设计知识,有针对性地进行解决和优化,从而为数字系统应用提供更加优化的时钟信号。

-

低通滤波器

+关注

关注

15文章

528浏览量

48829 -

电源噪声

+关注

关注

3文章

169浏览量

18057 -

时钟信号

+关注

关注

4文章

495浏览量

29696

发布评论请先 登录

电能质量在线监测装置的暂态波形存储时长一般是多久?

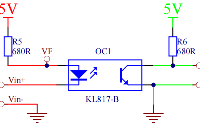

一般光耦的开关电路设计

对于波形和电平不标准的时钟信号一般应进行怎样的处理?

对于波形和电平不标准的时钟信号一般应进行怎样的处理?

评论