今天平头哥来和大家伙聊聊FPGA开发语言的事。对于FPGA入门者来说,选择用哪种开发语言或许也是一个让人苦恼的问题,目前开发FPGA的手段越来越多,这个后面再聊,先来说说对于RTL开发来说最古老的开发语言也就是VHDL和verilog了。VHDL和Verilog历史

VHDL的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware DescriptionLanguage,诞生于 1982 年。1987 年底,VHDL 被 IEEE 和美国国防部确认为标准硬件描述语言。自 IEEE 公布了 VHDL 的标准版本 IEEE-1076(简称 87 版)之后,各 EDA 公司相继推出了自己的 VHDL 设计环境,或宣布自己的设计工具可以提供 VHDL 接口。此后 VHDL 在电子设计领域逐步取代了原有的各种非标准硬件描述语言。1993 年,IEEE 对 VHDL 进行了修订,从更高的抽象层次和系统描述能力上扩展 VHDL 的内容,并公布了新版本的 VHDL,即 IEEE 标准的 1076-1993版本(简称 93 版)。现在,VHDL 和 Verilog HDL 作为 IEEE 的工业标准硬件描述语言,在电子工程领域已成为事实上的通用硬件描述语言。

VHDL 在语言形式、描述风格和句法上与一般的计算机高级语言十分相似。VHDL 的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件、一个电路模块或一个系统)分成外部和内部两部分。 外部也可称为可视部分,它描述了此模块的端口,而内部可称为不可视部分,它涉及到实体的功能实现和算法完成。在对一个设计实体定义了外部端口后,一旦其内部开发完成,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL 系统设计的基本点。一般的 VHDL 程序可以由实体(Entity)、结构体(Architecture)、配置(Configuration)、程序包和程序包体(Package)以及库(Library)5 个部分组成,它们是 VHDL 程序的设计单元。

其中实体、配置和程序包属于初级设计单元,主要的功能是进行端口、行为、函数等的定义。结构体和程序包体是次级设计单元,包含了所有行为以及函数的实现代码。其中,程序包和程序包体又属于公用设计单元,即它们是被其他程序模块调用的。库则是一批程序包的集合。

Verilog是由Gateway设计自动化公司的工程师于1983年末创立的。当时Gateway设计自动化公司还叫做自动集成设计系统(Automated Integrated Design Systems),1985年公司将名字改成了前者。该公司的菲尔·莫比(Phil Moorby)完成了Verilog的主要设计工作。1990年,Gateway设计自动化被Cadence公司收购。

1990年代初,开放Verilog国际(Open Verilog International, OVI)组织(即现在的Accellera)成立,Verilog面向公有领域开放。1992年,该组织寻求将Verilog纳入电气电子工程师学会标准 。最终,Verilog成为了电气电子工程师学会1364-1995标准,即通常所说的Verilog-95。

设计人员在使用这个版本的Verilog的过程中发现了一些可改进之处。为了解决用户在使用此版本Verilog过程中反映的问题,Verilog进行了修正和扩展,这部分内容后来再次被提交给电气电子工程师学会。这个扩展后的版本后来成为了电气电子工程师学会1364-2001标准,即通常所说的Verilog-2001。Verilog-2001是对Verilog-95的一个重大改进版本,它具备一些新的实用功能,例如敏感列表、多维数组、生成语句块、命名端口连接等。目前,Verilog-2001是Verilog的最主流版本,被大多数商业电子设计自动化软件包支持。

1995年,IEEE 制定了 Verilog HDL 的第一个国际标准,即 IEEE Std 1364-1995,也称之为 Verilog 1.0。

2001 年,IEEE 发布 Verilog 第二个标准(Verilog 2.0),即 IEEE Std 1364-2001, 简称为 Verilog-2001 标准。

VHDL和Verilog的区别

原文链接:例说Verilog和VHDL的区别,助你选择适合自己的硬件描述语言

HDL 建模能力:Verilog与VHDL

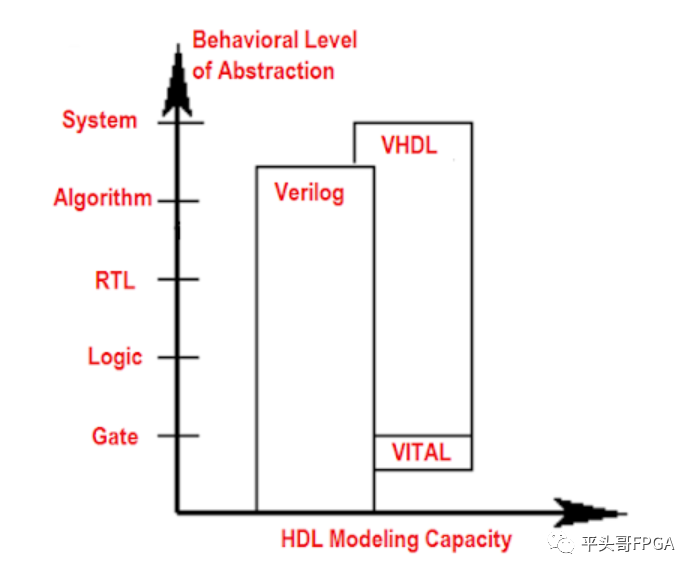

首先,让我们讨论一下 Verilog 和 VHDL 的硬件建模能力,因为它们都是用于建模硬件的硬件描述语言。下图显示了 Verilog 和 VHDL 在硬件抽象行为级别方面的 HDL 建模能力。

图形来源:Douglas J. Smith,“VHDL 和 Verilog 比较和对比加上 用 VHDL、Verilog 和 C 编写的建模示例”

低级建模

如上图所示,Verilog 和 VHDL 都能够对硬件进行建模。但是,在底层硬件建模方面,Verilog优于VHDL。这是合理的,因为 Verilog 最初是为建模和模拟逻辑门而创建的。事实上,Verilog 具有内置原语或低级逻辑门,因此设计人员可以在 Verilog 代码中实例化原语,而 VHDL 则没有。Verilog 的门基元:and、nand、or、nor、xor、xnor、buf、not、bufif0、notif0、bufif1、notif1、pullup、pulldown。 Verilog 的开关原语:pmos、nmos、rpmos、rnmos、cmos、rcmos、tran、rtran、tranif0、rtranif0、tranif1、rtranif1。

更重要的是,Verilog 支持用户定义基元 (UDP),因此设计人员可以定义自己的单元基元。此功能对于 ASIC 设计人员来说尤其必要。以下是有关如何在 Verilog 代码中实例化门基元的 Verilog 示例:

or #5 u1(x,y,z);

and #10 u2(i1,i2,i3);

ADC_CIRCUIT u3(in1,out1,out2,clock);

// ADC_CIRCUIT is an User-Defined Primitive for

// Analog to Digital Converter for example.

Verilog 中一些低级内置门基元的 VHDL 等效项可以通过使用逻辑运算符如 NOT、AND、NAND、OR、NOR、XOR、XNOR 来实现。下面是 Verilog 门基元的 VHDL 等效代码示例:

or u1(x,y,z); in Verilog <=> x <= y OR z; in VHDL

and u2(i1,i2,i3); (Verilog) <=> i3 <= i2 AND i3; in VHDL

为了支持 Verilog 中的 UDP 功能,VITAL(VHDL Initiative Towards ASIC Libraries-VHDL 面向 ASIC 库的倡议)问世,使 ASIC 设计人员能够在符合 VITAL 的 VHDL 中创建自己的单元基元或 ASIC 库,如上图所示。尽管如此,VHDL 仍然可能无法实现 Verilog 对低级硬件建模的支持。因此,如果我是 ASIC 设计师,我会更喜欢 Verilog 而不是 VHDL。

高级建模

另一方面,如上述图表所示,VHDL 在高级硬件建模方面优于 Verilog。与 Verilog 相比,VHDL 为高级硬件建模提供了更多功能和构造。以下是在比较 VHDL 和 Verilog 时支持高级硬件建模的主要不同功能:-

VHDL 中的用户定义数据类型

type int_8bit is range 0 to 255 -- define 8-bit unsigned numbers

signal i : int_8bit;

type state_FSM is (Idle, start, calculate , finish, delay)

-- define symbolic states to represent FSM states.

signal current_state, next_state: state_FSM;

VHDL 中的设计重用包

VHDL 中的包通常用于数据类型和子程序的声明。VHDL 包中声明的子程序或数据类型可用于许多不同的实体或体系结构。例如:

package fsm_type is

type FSM_states is (IDLE, TRANSMIT, RECEIVE, STOP);

end package

-- to use the FSM_states type in an entity or architecture

-- use the following statement on top of the entity

use work.fsm_type.all

entity example is

Verilog 中没有包定义。与 VHDL 包最接近的 Verilog 等效项是`includeVerilog 编译器指令。函数或定义可以单独保存在另一个文件中,然后通过使用`include指令在模块中使用它。下面是一个 Verilog 示例代码:

// Below is the content of "VerilogVsVHDL.h" file

`define INPUT_VERILOG "./test_VerilogvsVHDL.hex" // Input file name

`define OUTPUT_VHDL "VHDL.bmp" // Output file name

`define VERILOG_VHDL_DIFFERENCE

// Then call it in every single module that you want to use the definition above

`include "VerilogVsVHDL.h"

-

VHDL 中的配置语句

entity BUF is

generic (DELAY : TIME := 10 ns);

port ( BUF_IN : in BIT; BUF_OUT : out BIT);

end BUF;

-- The first design architecture for BUF

architecture STRUCT_BUF1 of BUF is

signal temp: bit;

begin

BUF_OUT <= not temp after DELAY;

temp <= not BUF_IN after DELAY;

end STRUCT_BUF1;

-- The second design architecture for BUF

architecture STRUCT_BUF2 of BUF is

begin

BUF_OUT <= BUF_IN after 2*DELAY;;

end STRUCT_BUF2;

-- Testbench to simulate BUF entity

entity BUF_TESTBENCH is

end BUF_TESTBENCH;

architecture STRUCT_BUF_TEST of BUF_TESTBENCH is

signal TEST1, TEST2 : BIT := '1';

-- BUF_COMP component declaration:

component BUF_COMP is

generic (TIME_DELAY : TIME);

port ( IN1 : in BIT; OUT1 : out BIT );

end component;

begin

-- instantiation of BUF_COMP component:

DUT:BUF_COMP generic map (10 ns) port map (TEST1,TEST2);

end STRUCT_BUF_TEST;

-- Configuration specify the design entity and architecture

-- for the DUT component instance in the testbench above

configuration CONFIG_BUF of TEST_BUF is

-- Associate BUF_COMP component instance to BUF design entity

-- and STRUCT_BUF1 design architecture for simulation

for STRUCT_BUF_TEST

for DUT : BUF_COMP

use entity WORK.BUF (STRUCT_BUF1)

generic map (DELAY => TIME_DELAY)

port map (BUF_IN => IN1, BUF_OUT => OUT1);

end for;

end for ;

end CONFIG_BUF;

Verilog-2001 中还添加了配置块。

-

VHDL 中的库管理

-- library management in VHDL

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.all;

use work.clock_div.all;

简而言之,VHDL 在高级硬件建模方面比 Verilog 更好。由于 FPGA 设计流程不需要低级硬件建模,如果我是 FPGA 设计师,我更喜欢 VHDL 而不是 Verilog。 值得一提的是,SystemVerilog 的创建是为了通过将 VHDL 中的高级功能和结构添加到 Verilog 中进行验证来增强 Verilog 语言在高级建模中的弱点。SystemVerilog 现在广泛用于 IC 验证。

冗长(Verboseness:):Verilog 与 VHDL

-

VHDL 是强类型的vs Verilog 是松散类型的

signal test_reg1: std_logic_vector(3 downto 0);

signal test_reg2: std_logic_vector(7 downto 0);

test_reg2 <= test_reg1;

-- You cannot assign a 4-bit signal to an 8-bit signal

-- in VHDL, it will introduce a syntax error below:

-- Width mismatch. Expected width 8, Actual width is 4

-- for dimension 1 of test_reg1.

编译上面的VHDL代码时,会出现语法错误“ Width mismatch. Expected width 8, Actual width is 4 ”。如果将VHDL代码改为“test_reg2 <= "0000"&test_reg1; "匹配位宽,则不会出现语法错误。

如果在 Verilog 中将 4 位信号分配给 8 位信号会怎样?

wire [3:0] test1;

wire [7:0] test2;

// In Verilog, you can assign 4-bit signal to 8-bit signal.

assign test2 = test1;

// there will be no syntax error during synthesis

当您将 4 位信号分配给 8 位信号时,Verilog 编译器不会引入语法错误。在 Verilog 中,不同位宽的信号可以相互分配。Verilog 编译器将使源信号的宽度适应目标信号的宽度。未使用的位将在综合期间进行优化。

下面是在分配信号时混合数据类型的另一个 VHDL 示例:

signal test1: std_logic_vector(7 downto 0);

signal test2: integer;

test2 <= test1;

-- Syntax Error: type of test2 is incompatile with type of test1

上面的 VHDL 代码会引入一个语法错误“ (type of test2 is incompatible with type of test1)test2 的类型与 test1 的类型不兼容”。你必须转换test1的分配之前整数数据类型TEST1到TEST2如下:

library IEEE;

USE ieee.numeric_std.ALL;

signal test1: std_logic_vector(3 downto 0);

signal test2: integer;

-- Use IEEE.NUMBERIC_STD.ALL Library for this conversion

test2 <= to_integer(unsigned(test1));

-- No syntax errors this time

另一方面,Verilog 在分配时混合数据类型时没有问题。以下是一个 Verilog 示例:

reg [3:0] test1;

integer test2;

always @(test1) begin

test2 = test1;

end

// NO syntax errors when compiling

当您将具有reg数据类型的信号分配给具有不同数据类型(如integer )的另一个信号时, Verilog 编译器不会像在 VHDL 中那样引入语法错误。

-

VHDL 复杂数据类型与 Verilog 简单数据类型

-- VHDL code for ALU

process(SEL,ABUS,BBUS,tmp1,tmp2)

begin

case(SEL) is

when "0000" => ALUOUT <= tmp1; -- ADD

when "0001" => ALUOUT <= tmp2;-- SUB

when "0010" => ALUOUT <= BBUS; -- AND

when others => ALUOUT <= ABUS;

end case;

end process;

// Verilog equivalent to VHDL ALU

assign ALUOUT=(SEL==0)?tmp1:((SEL==1)?tmp2:((SEL==2)?BBUS:ABUS));

VHDL 中的 if else、when/else、with/select 语句可以在 Verilog 中使用条件运算符 (?) 表达得更简洁,如上例所示。

Verilog 和 VHDL 之间的其他区别:

-

Verilog 类似于C 编程语言,而 VHDL 类似于Ada或 Pascal 编程语言

-

Verilog 区分大小写,而 VHDL 不区分大小写。这意味着DAta1和Data1在Verilog中是两个不同的信号,但在VHDL中是相同的信号。在 Verilog 中,要在模块中使用组件实例,您只需在模块中使用正确的端口映射对其进行实例化。在VHDL中,在实例化实例之前,如果您使用旧的实例化语句作为以下示例,则通常需要将组件声明为架构或包中。在 VHDL-93 中,您可以像这样直接实例化实体:“Label_name: entity work.component_name port map (port list);”。

例如,要在 VHDL 中实例化实体 clk_div,将在体系结构代码中添加一个组件声明,如下所示:

architecture Behavioral of digital_clock is

-- component declaration before instantiation below

component clk_div

port (

clk_50: in std_logic;

clk_1s : out std_logic

);

end component;

signal clk, clk_1s: std_logic;

begin

-- component instantiation

create_1s_clock: clk_div port map (clk_50 => clk, clk_1s => clk_1s);

end

或者在包中声明组件以供重用:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

package clock_div_pack is

component clk_div is

port (

clk_50: in std_logic;

clk_1s : out std_logic

);

end component clk_div;

end package;

-- Declare the component in a separate package and

-- reuse by using the following statement:

use work.clock_div_pack.all;

entity clock is

end clock;

architecture Behavioral of clock is

signal clk, clk_1s: std_logic;

begin

create_1s_clock: clk_div port map (clk_50 => clk, clk_1s => clk_1s);

end

在 VHDL-93 中直接实例化实体的示例代码:

create_1s_clock: entity work.clk_div port map (clk_50 => clk, clk_1s => clk_1s);

-

Verilog 具有编译器指令,例如`timescale(声明时间单位和延迟精度)、`define(将文本字符串声明为宏名称)、`ifdef、ifndef `else `elseif `endif(条件编译)、`include(包括一个可以包含函数或其他声明的文件)等。VHDL 没有编译器指令。

-

VHDL 支持枚举和记录数据类型,允许用户为一种数据类型定义多个信号。Verilog 不支持枚举和记录类型。下面是枚举和记录类型的 VHDL 代码:

type FSM is (IDLE, TEST, VERILOGvsVHDL, STOP, FPGA4student);

-- enumerated type

type int_4 is range 0 to 15;

-- record tye in VHDL

type record_example is record

data1: integer;

data2: int_4;

data3: FSM;

end record;

等等。

尽管 Verilog 和 VHDL 之间存在差异,但它们是两种最流行的硬件描述语言。如果可以,最好同时学习它们。重要的是要记住,在编码时始终考虑逻辑门或硬件以开发硬件编码思维,而在使用 Verilog 和 VHDL 编码时忘记软件编程思维,这一点非常重要。详细对比 表格:

表格转自:Verilog HDL和VHDL的区别

作者:比特波特

VHDL 与 VerilogHDL 的不同点

| 序号 | 区别之处 | VHDL | Verilog |

| 1 | 文件的扩展名不一样 | .vhd | .v |

| 2 | 结构不一样 |

包含库、实体、结构体。 ENTITY 实体名 IS PORT(端口说明) END 实体名 ;ARCHITECTURE 结构体名 OF 实体名 IS 说明部分BEGIN 赋值语句/ 元件语句/ 进程语句 END 结构体名 ; |

模块结构 (module… endmodule) module 模块名 (端口列表) ; 输入/输出端口说明; 变量类型说明;assign 语句 (连续赋值语句) ;元件例化语句;always@(敏感列表)begin …end endmodule其中assign语句、元件例化语句、always语句的顺序可以更换 |

| 3 | 对库文件的要求不一样 | 须有相应的库或程序包支持,实体间调用子程序,需要将子程序打成程序包 | 没有专门的库文件 (只有基本门的库),模块可以通过例化直接调用,不需要打成程序包 |

| 4 | 端口定义的地方不一样 | 实体中定义 | module的模块名后面先列出端口列表,再在模块中用input,output等定义 |

| 5 | 端口定义方式不一样 |

端口名(端口名,端口名) : 方向 数据类型名(Default Value) ; 例如:Q1 : IN Std_Logic_Vector(31 DOWNTO 0) ; |

端口类型 端口1,端口2,端口3,…; 例如:inout [31:0]Q; |

| 6 | 端口定义类型不一样 | 有IN, OUT, INOUT, BTFFER 四种 | 有input ,output, inout 三种 |

| 7 | 内部信号(SIGNAL)声明不一样 | 在结构体中声明,有些局部变量还可在进程中声明 | 在端口定义后进行声明内部变量 |

| 8 | 标识符规则不一样 | 不区分大小写 | 区分大小写 |

| 9 | 关键词要求不一样 |

允许大小写混写 例如:EnTity |

关键词必须小写 |

| 10 | 常量定义的关键词和格式表示不一样 | CONSTANT 常量名:数据类型 :=数值; | parameter 常量名1 = 数值1, 常量名2 = 数值2,…,常量名n = 数值n; |

| 11 | 常量表示不一样 |

用双引号. 例如:B"011100" |

<位宽>’<进制符号><数字> 例如:8’b10110011 |

| 12 | 数组定义方式不一样 |

定义4位数组A: A(3 DOWNTO 0 ) 或者A(0 TO 3) |

定义4位数组A: A[3:0] 或者A[0:3] |

| 13 | 下标名表示不一样 |

用小括号表示, 例如:a(0) |

用中括号表示, 例如:a[0] |

| 14 | 数据对象不一样,且二者变量的含义不一样 |

常量,变量,信号. 变量是一个局部量,只能在进程和子程序中使用。变量的赋值是一种理想化的数据传输,是立即发生,不存在任何延时的行为。信号是描述硬件系统的基本数据对象,它类似于连接线。信号可以作为设计实体中并行语句模块间的信息交流通道。数据对象没有默认 |

常量,变量 变量是在程序运行时其值可以改变的量。变量默认为wire型 |

| 15 | 数据默认值 | 默认值为本类型的最小非负值(某个类型的范围是以0为对称的) | wire类型默认值为 z, reg类型默认值为x ; |

| 16 | 变量定义的格式不一样 |

VARIABLE 变量名:数据类型 :=初始值 例如:VARIABLE k:Integer RANGE 0 TO 7; |

数据类型 [位宽] 变量1,变量2,…,变量n; |

| 17 | 数据类型不一样 |

布尔(BOOLEAN)、位(BIT)、位矢量(BIT_VECTOR)、标准逻辑位(STD_LOGIC)、标准逻辑矢量(STD_LOGIC_VECTOR)。 VHDL的数据类型比较复杂。 |

wire,tri,reg,interger,real,time型,主要是wire和reg型,比较简单。 |

| 18 | 赋值不一样 | 按数据对象赋值分,变量赋值使用“:=”,信号赋值使用"<=" | 按语句的执行情况分,assign语句和阻塞语句用“=”赋值,非阻塞语句用“<=” |

| 19 | 赋值要求不一样 |

强类型语言,赋值两边的赋值目标和表达式的数据类型必须一样。不同类型和宽度的数据之间不能运算和赋值,需要调用包来完成转换; 例如:A:IN STD_LOGIC_VECTOR(2 DOWNTO 0)B:IN STD_LOGIC_VECTOR(2 DOWNTO 0)C:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) 则C<=A OR B;会出错 |

不是强类型语言,可以自动完成不同类型数据的运算和赋值; 例如:input [2:0]a;input [2:0]b;output [3:0]c; assign c=a&b;不会出错 |

| 20 | 操作符不一样 | 逻辑操作符(Logica Operator)、关系操作符(Relationa Operator)、算术操作符(Arithmetic Operator)、符号操作符(Sign Operator),没有缩减操作符,没有三目的条件操作符 | 操作符比较丰富,有算数操作符,逻辑操作符,位运算、关系操作符,等式操作符,缩减操作符,转移操作符,条件操作符,位并接操作符 |

| 21 | 条件中,等于判断符号不一样 | 等于= ; 不等于 /= |

等于(= =)或全等(= = =) 不等于(!=)或不全等(!= =) |

| 22 | 逻辑操作符不一样 |

AND, NAND, NOT, OR, NOR, XNOR, XOR等 该逻辑操作符运算结果跟Verilog HDL的位运算一样 |

&&(逻辑与), || (逻辑或), !(逻辑非), ~ (按位取反), &(按位与), |(按位或), ^(按位异或), ^~ 或~ ^(按位同或) |

| 23 | 移位操作符不一样 | 除了逻辑左移SLL、逻辑右移SRL之外,还有算数左移SLA、算数右移SRA、循环左移ROL、循环右移ROR。其中逻辑左移SLL、逻辑右移SRL与Verilog HDL的左移<<, 右移>>一致 | 只有逻辑左移<< 和逻辑右移>>,没有算数左移、算数右移、循环左移、循环右移。 |

| 24 | 并置操作符不一样 |

用&并置, 例如:a&b |

用{ }并置, 例如:{a, b} |

| 25 | 并行赋值语句不一样 | 信号赋值语句 (直接赋值、条件赋值、选择赋值) | assign语句 (连续赋值) 只对wire型 |

| 26 | 顺序语句不一样 |

信号赋值 变量赋值(变量赋值只能在进程和子进程中进行) |

阻塞语句 非阻塞语句 |

| 27 | 并行语句中的进程语句不一样 |

PROCESS(敏感列表) BEGIN顺序语句;END PROCESS; |

always@ (敏感列表) begin顺序语句;end |

| 28 | 条件判断语句if的格式不一样 |

IF 条件1 THEN 顺序描述语句;ELSIF 条件2 THEN顺序描述语句;…ELSE 顺序描述语句;END IF; |

if (条件1) 顺序描述语句; else if (条件2) 顺序描述语句;…else 顺序描述语句; |

| 29 | 条件控制语句case的格式不一样 |

CASE 表达式 IS WHEN 条件表达式1 => 顺序描述语句; WHEN 条件表达式2 => 顺序描述语句; WHEN 条件表达式3 => 顺序描述语句; … WHEN 条件表达式n => 顺序描述语句;END CASE如果没有列举出CASE和IS之间的表达式的全部取值,则WHEN OTHERS =>必不可少 |

case (表达式) 选择值1:语句1; 选择值2:语句2; 选择值3:语句3; … 选择值n:语句n; default:语句n+1;endcasedefault没有,不会出现语法错误,但逻辑有可能产生错误 |

| 30 | case语句的应用范围也不一样 | 在CASE语句中,条件表达式是没有优先级的,如优先级编码器可以用IF语句进行描述,但不可以使用CASE语句描述 | 除了case以外,还有相关的casex和casez语句,如用casex可以实现优先编码器 |

| 31 | 循环控制语句不一样 | 循环控制语句有:FOR_LOOP循环语句、WHILE_LOOP循环语句、NEXT语句、EXIT语句 | for语句、repeat语句、while语句、和forever语句 |

| 32 | for循环控制语句格式不一样 |

[标号:] FOR 循环变量 IN 循环次数范围 LOOP 顺序语句 END LOOP [标号]; |

for(循环指针=初值; 循环指针<终值; 循环指针=循环指针+步长值) begin 顺序语句; … end |

| 33 | for循环中的循环变量存在区别 | 循环变量不需要定义 | 循环指针需要定义 |

| 34 | while语句格式不一样 |

[标号:] WHILE 条件 LOOP 顺序描述语句; END LOOP [标号];在循环体内,必须包含条件式中判别变量的赋值语句。 |

while(循环执行条件表达式) begin 重复执行语句; 修改循环条件语句; end |

| 35 | 元件例化不一样 |

COMPONENT 元件名 IS GENERIC 说明;PORT 说明;END COMPONENT 元件名; |

设计模块名 <例化电路名> (端口列表) ; |

| 36 | 时钟定义不一样 |

时钟列在PROCESS的敏感列表中,如若上升沿有效,则 PROCESS(clk)BEGINIF (clk’EVENT AND clk=‘1’) THEN…END PROCESS; |

在always结构中,上升沿直接体现在always的敏感列表中。如 always@ (posedge clk)begin…end |

| 37 | 时钟边沿定义方式不一样 |

上升沿(clk’EVENT AND clk=‘1’) 下降沿(clk’EVENT AND clk=‘0’) |

上升沿posedge clk 下降沿negedge clk |

| 38 | 生成重复结构的能力不同 |

有生成语句(GENERATE)生成由大量相同单元构成的模块,格式为: [标号:] FOR 循环变量 IN 取值范围GENERATE[说明部分]BEGIN[并行语句]; - -元件例化语句,以重复产生并行元件。END GENERATE [标号];或者IF 条件 GENERATE[说明部分]BEGIN[并行语句]END GENERATE [标号]; |

没有对应的生成语句,有相近的实例数组,格式为: <模块名字> <实例名字> <范围> (<端口>); |

| 39 | 子程序不一样 | procedure和function | task 和 function |

| 40 | 注释方法不一样 | 用- -引导注释信息 | 用//或/*…*/注释 |

-

FPGA

+关注

关注

1655文章

22287浏览量

630311 -

vhdl

+关注

关注

30文章

820浏览量

131347 -

电路模块

+关注

关注

7文章

37浏览量

15674

原文标题:FPGA开发语言的选择

文章出处:【微信号:ZYNQ,微信公众号:ZYNQ】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

采用高级语言开发FPGA的探索

VHDL语言在FPGA/CPLD开发中的应用?

Verilog HDL语言在FPGA/CPLD开发中的应用

FPGA开发语言的选择

FPGA开发语言的选择

评论