RISC-V特权架构

ARM有7种工作模式,而RISC-V也有不同的模式,这些模式在RISC-V中也被称为特权架构。

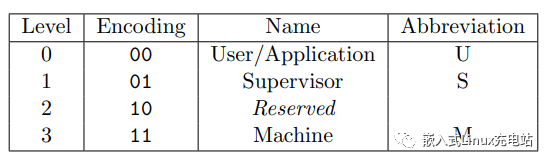

RISC-V总共有四种模式,分别是U、S、H和M模式:

U模式被编码为00,S模式编码为01,H模式编码为10,M模式编码为11。Level越高,等级越高。等级越高,拥有的访问权限也更高。按照特权等级,由高到低依次为M、H、S、U。

上图中编码为10的模式是保留的,这个模式实际上就是H模式,H模式是用作虚拟化,但是目前RISC-V对虚拟化还不太完善,基本不支持。因此上图并没有将H模式标出来,而是作为保留。也正是因此,有人经常将RISC-V的模式说成三种U、S和M。

- U模式:User,用户模式

- S模式:Supervisor,监管者模式

- M模式:Machine,机器模式

以RISC-V Linux为例,Linux应用程序处于U模式,Linux内核/uboot处于S模式,M模式则是OpenSBI。M模式拥有最高访问权限,Linux内核如果要访问CSR寄存器,则必须由S模式切换到M模式,由OpenSBI读取CSR寄存器,然后将数据返回给内核。

M模式是必须要选择的,RISC-V的裸机代码都运行在M模式下。

RISC-V通用寄存器

| 寄存器 | ABI名称 | 说明 |

|---|---|---|

| x0 | zero | 0值寄存器,硬编码为0,写入数据忽略,读取数据为0 |

| x1 | ra | 用于返回地址(return address) |

| x2 | sp | 用于栈指针(stack pointer) |

| x3 | gp | 用于通用指针(global pointer) |

| x4 | tp | 用于线程指针 |

| x5 | t0 | 用于存放临时数据或者备用链接寄存器 |

| x6~x7 | t1~t2 | 用于存放临时数据寄存器 |

| x8 | s0/fp | 需要保存的寄存器或者帧指针寄存器 |

| x9 | s1 | 需要保存寄存器 |

| x10~x11 | a0~a1 | 函数参数或者返回值寄存器 |

| x12~x17 | a2-a7 | 函数传递参数寄存器 |

| x18~x27 | s2-s11 | 需要保存的寄存器 |

| x28~x31 | t3~t6 | 用于存放临时数据寄存器 |

RISC-V有x0 x31共32个通用寄存器,每个通用寄存器都有各自的用途,例如x2是作为sp栈指针、a0~a1用来保存函数参数或返回值。x0寄存器被硬编码为了0,就是个0值寄存器。

ABI名称相当于这些通用寄存器的别名,在RISC-V汇编当中,都使用ABI名称来代表这些寄存器。

-

寄存器

+关注

关注

31文章

5618浏览量

130389 -

内核

+关注

关注

4文章

1474浏览量

43089 -

Linux

+关注

关注

88文章

11810浏览量

219513 -

RISC

+关注

关注

6文章

485浏览量

86826 -

架构

+关注

关注

1文章

537浏览量

26643

发布评论请先 登录

RISC-V特权架构和通用寄存器

RISC-V特权架构和通用寄存器

评论