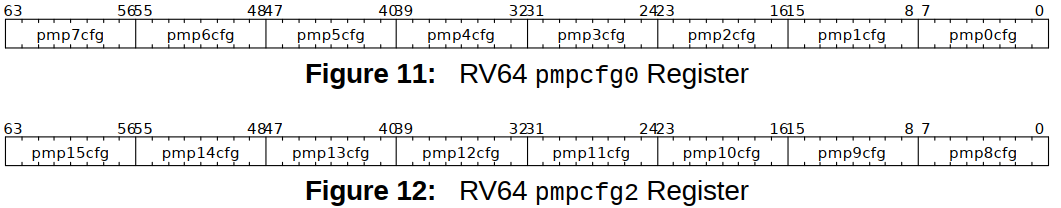

每个 PMP 区域都由一个 8 位 pmpXcfg 字段描述,与一个 64 位 pmpaddrX寄存器结合使用,该寄存器保存受保护区域的基地址。每个区域的范围取决于下一节中描述的寻址 (A) 模式。pmpXcfg 字段位于 64 位 pmpcfgY CSR中。

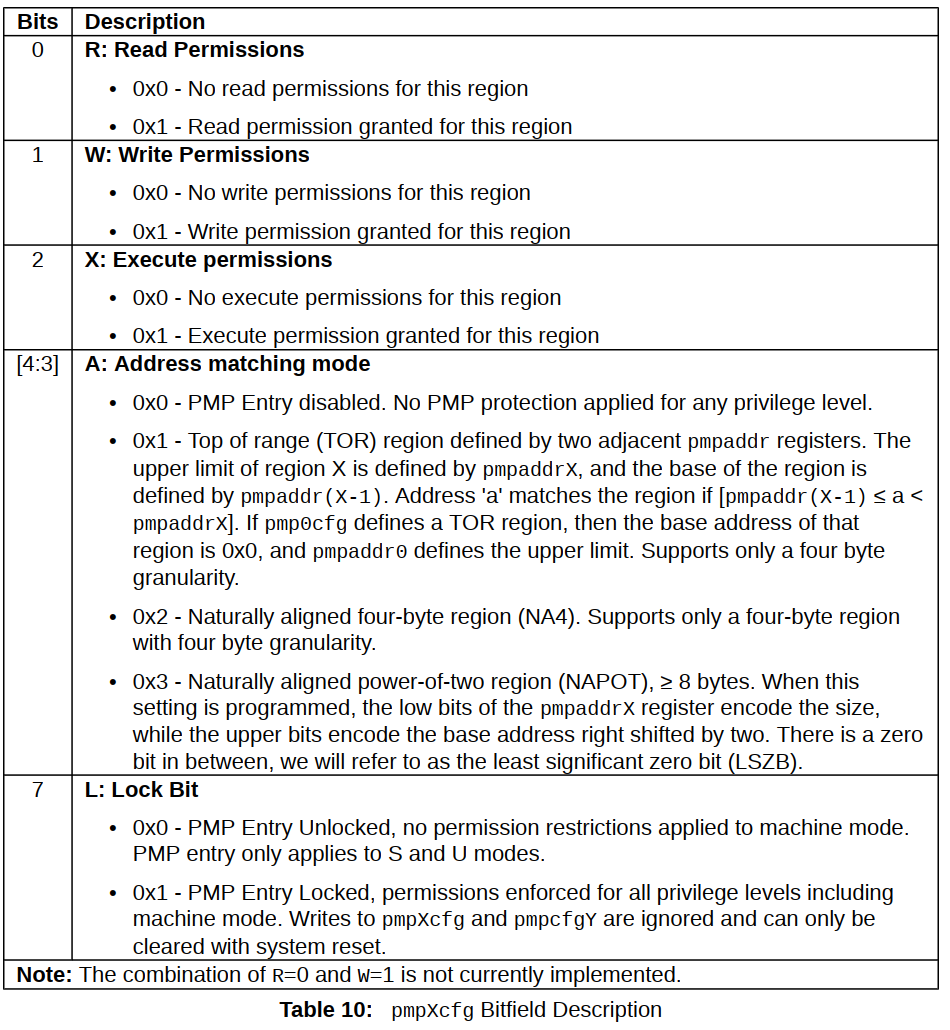

每个 8 位 pmpXcfg 字段包括一个读、写和执行位,外加一个两位地址匹配字段 A 和一个锁定位 L。允许重叠区域,其中编号最小的 PMP条目胜出该区域。

PMP 配置寄存器

对于 RV64 架构,未实现 pmpcfg1 和 pmpcfg3。这减少了占用空间,因为 pmpcfg2 已经包含 RV32 和 pmp11cfg的配置字段 pmp8cfg 和 RV64。

pmpcfgY 和 pmpaddrX 寄存器只能通过 CSR 特定指令访问,例如用于读取的 csrr 和用于写入的 csrw。

复位后,PMP 寄存器字段 A 和 L 设置为 0。RISC‑V 指令集手册第 II 卷:特权架构版本 1.10 未指定所有其他 hart状态。

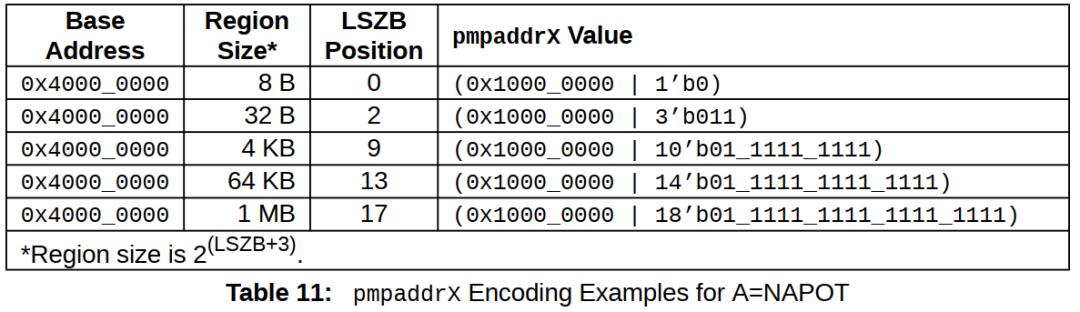

下面是一些使用 NAPOT 地址模式的例子。

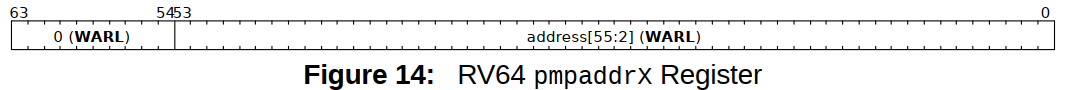

PMP 地址寄存器

PMP 有 8 个地址寄存器。每个地址寄存器 pmpaddrX 都与相应的 pmpXcfg字段相关联。每个地址寄存器都包含右移两位的受保护区域的基地址,以实现最小 4 字节对齐。

根据 RISC‑V 指令集手册,第二卷:特权架构,版本 1.10,最大编码地址位为 [55:2]

-

寄存器

+关注

关注

31文章

5589浏览量

129074 -

内核

+关注

关注

4文章

1436浏览量

42493 -

PMP

+关注

关注

0文章

45浏览量

18638 -

RISC

+关注

关注

6文章

485浏览量

86103 -

架构

+关注

关注

1文章

533浏览量

26506 -

sifive

+关注

关注

0文章

37浏览量

9733

发布评论请先 登录

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

RISC-V 基础学习:RISC-V 基础介绍

RISC-V工作模式及寄存器基本知识

RISC-V基础指令详解

RISC-V M扩展介绍

RISC-V B扩展介绍及实现

玄铁VirtualZone:基于RISC-V架构的安全扩展

初探RISC-V—《RISC-V体系结构编程与实践》

RISC-V 发展

RISC-V MCU gp全局指针说明

RISC-V特权架构和通用寄存器

RISC-V PMP寄存器介绍

RISC-V PMP寄存器介绍

评论