碲镉汞材料具有截止波长在红外波段内可调节、光学吸收系数高、量子效率高等特点,是重要的红外探测器应用材料之一。近年来分子束外延生长碲镉汞技术的快速发展,使用分子束外延制备高性能、多色红外焦平面列阵探测器引起了人们的广泛关注。为了满足高性能、双多色红外焦平面器件制备的要求,需要对碲镉汞p型掺杂与激活进行专项研究。使用分子束外延方法直接在碲镉汞工艺中进行掺杂,As很难占据Te位,一般作为间隙原子或者占据金属位,因此原生的碲镉汞常表现为n型导电。只有经过高温激活,将As原子激活至非金属位(Te原子位置),才能起到受主的作用,使碲镉汞材料表现为p型导电。

据麦姆斯咨询报道,近期,华北光电技术研究所和重庆嘉陵华光光电科技有限公司的科研团队在《激光与红外》期刊上发表了以“分子束外延HgTe/CdTe超晶格工艺研究”为主题的文章。该文章第一作者为高达。

本文报道了分子束外延生长HgTe/CdTe超晶格结构相关技术。采用HgTe/CdTe超晶格结构进行As掺杂是降低As掺杂元素激活温度的技术路径之一。

实验方案

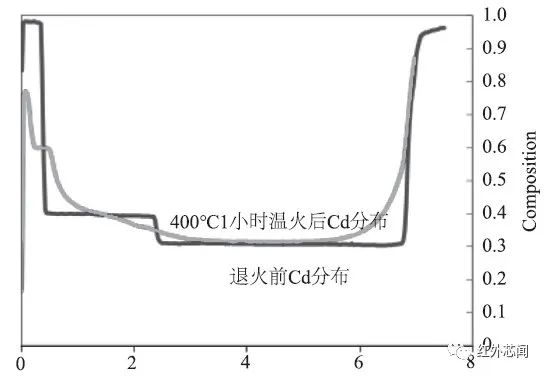

传统的As掺杂激活方式为采用350℃以上的高温、在汞饱和条件下对碲镉汞材料进行退火,易引起碲镉汞表面状态恶化,从而影响后续器件性能;其次,高温退火会引起材料内原子剧烈的互扩散,使具有复杂结构设计的多层异质外延碲镉汞材料失效。如图1所示,原位掺杂的异质结结构p-on-n材料在经过400℃ 1小时激活退火后,异质结结构发生明显的互扩散,异质结结构对碲镉汞探测器性能提升的作用势必降低。在双色的nPn结构中,这种高温激活引起的互扩散将导致串音等问题。因此如何在更低温度下激活AS掺杂的碲镉汞材料是碲镉汞材料技术领域研究的热点之一。

图1 SIMS表征退火前后碲镉汞组分分布

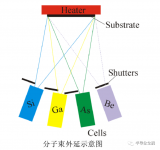

使用HgTe/CdTe超晶格结构进行As掺杂是降低As掺杂元素激活温度的技术路径之一。传统的使用分子束外延方式直接在碲镉汞工艺中进行As掺杂,As占据Hg位从而使材料呈n型,需要对材料进行高温(350℃以上)热处理将As激活至Te位从而使碲镉汞材料呈p型,本文采用的HgTe/CdTe超晶格结构材料在CdTe层间开启As束流与Hg束流进行掺杂,保证As直接与Hg结合占据Te位,使材料呈p型。降低As掺杂激活需要的温度。但是由于HgTe、CdTe两种材料生长条件有较大的差异,本文将开发合适的生长工艺参数完成HgTe/CdTe超晶格材料生长,并实现As掺杂材料在低温下的激活。

结构设计

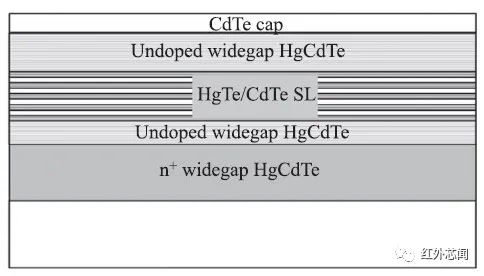

具有HgTe/CdTe超晶格结构As掺杂碲镉汞材料的结构如图2所示,在衬底上首先生长原位In掺杂的n型碲镉汞材料作为吸收层,再生长同组分的非掺杂阻挡层尽可能抑制掺杂元素互扩散,再生长超晶格结构,同时进行原位As掺杂,最后依次生长非掺杂碲镉汞层和碲化镉钝化层。

图2 原位掺杂HgTe/CdTe超晶格结构

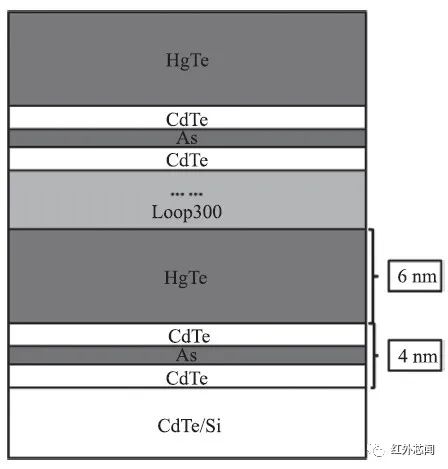

为了表征HgTe/CdTe超晶格结构生长参数控制精度、HgTe/CdTe超晶格结构原位掺杂及低温激活效果,本文研究了在硅基复合衬底上直接进行HgTe/CdTe超晶格的材料工艺。设计硅基HgTe/CdTe超晶格材料的结构如图3所示,在硅基复合衬底上直接生长HgTe/CdTe超晶格材料。其中CdTe层4 nm,HgTe层6nm,在CdTe层生长中间掺杂一原子单层的As元素。总共生长300个周期。

图3 硅基HgTe/CdTe超晶格结构

温度控制

温度控制是硅基复合衬底上分子束外延碲镉汞超晶格材料的难点之一:1.随着碲镉汞材料生长,材料吸热系数增加,需要实时调整设定温度保证碲镉汞外延温度稳定;2.碲镉汞材料对温度较为敏感,±2℃以上的温度偏差即对材料质量造成影响。因此,我们主要用红外测温仪(测温范围为100~300℃)实时监控衬底温度,利用铟(熔点156℃)校准红外测温仪,保证超晶格材料生长温度控制的稳定性。

HgTe/CdTe超晶格工艺参数设计

分子束外延HgTe/CdTe超晶格材料工艺中,HgTe、CdTe超晶格两种材料最优的生长温度相差100℃之上,且每一层材料生长时间只有几十秒,材料生长温度无法快速调整。因此需要生长参数平衡点来保证HgTe、CdTe两种材料均能获得较高的晶体质量。我们采用的工艺方案是生长温度采用适合HgTe材料生长的温度,用降低生长速率的方式提高低温下CdTe材料的生长质量。

实验结果及分析

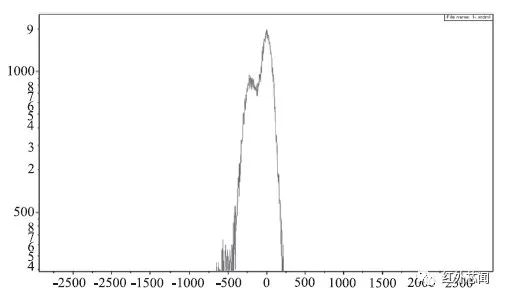

采用X射线双晶摇摆曲线表征HgTe/CdTe超晶格材料晶体质量。衍射图像显示有两个峰,位于-227″处的峰值强度较低,为CdTe复合衬底材料衍射曲线。另一个峰位于-2″,为HgTe/CdTe超晶格材料衍射曲线,双晶衍射半峰宽为155″。这表明超晶格质量良好,与在硅基复合衬底上外延的同厚度的碲镉汞材料双晶衍射半峰宽相当。

图4 HgTe/CdTe超晶格结构XRD衍射图像

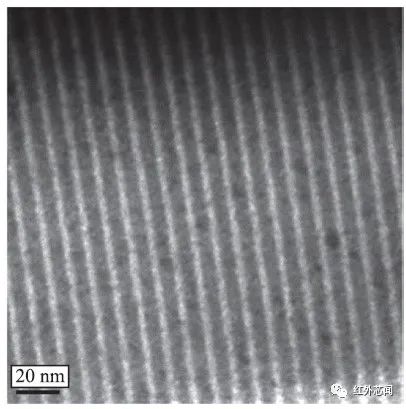

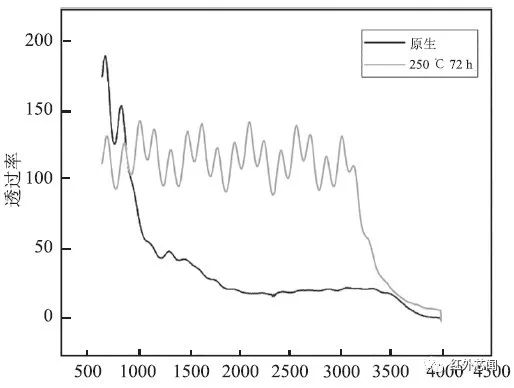

采用透射电镜表征HgTe/CdTe超晶格材料结构。如图5所示,4 nm CdTe/6 nm HgTe超晶格结构在透射电镜下清晰可见,材料参数控制精确。使用FTIR表征碲镉汞红外透过曲线,原生片表现为在长波波段出现吸收,这是因为HgTe、CdTe界面不陡峭,有少量互扩散产生。250℃ 72h汞饱和退火后,超晶格结构充分扩散,得到的碲镉汞材料组分为0.3834,厚度为2.9μm。与超晶格材料参数设计值相当,表明材料参数控制良好。

图5 HgTe/CdTe样品TEM图像

图6 HgTe/CdTe样品红外透过曲线图像

使用Hall测试250℃ 72h汞饱和退火后的超晶格结构材料,测试结果显示77 K下材料呈p型,p型浓度2.67×10¹⁶cm⁻³,迁移率73.3 cm²/Vs。退火过程中采用汞饱和的退火条件,排除汞空位引起的p型,说明As掺杂超晶格结构的p型由As元素引起。表明掺杂的As元素在250℃即被激活,HgTe/CdTe超晶格材料As掺杂工艺达到设计目的。

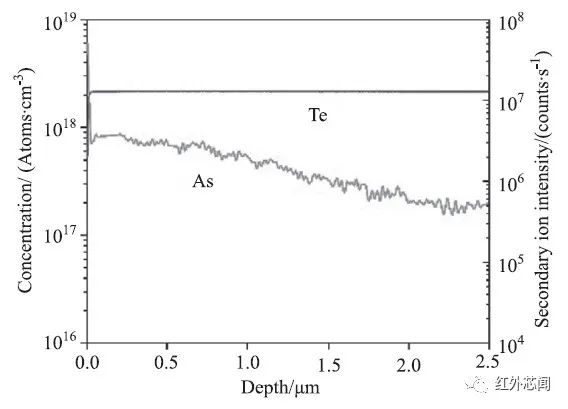

图7使用SIMS表征了HgTe/CdTe超晶格材料As掺杂浓度,掺杂浓度约为3×10¹⁷ cm⁻³,比Hall测试得到的p型浓度高出一个量级,导致这个问题原因可能是:部分As元素仍然处在间隙位、汞饱和退火后材料中施主对材料Hall测试结果产生影响。

图7 SIMS表征HgTe/CdTe超晶格结构As浓度

结论

本文报道了在硅基复合衬底上分子束外延HgTe/CdTe超晶格结构材料工艺研究。成功开发了在硅基复合衬底上外延HgTe/CdTe超晶格结构材料的工艺,材料质量良好,材料参数达到预期水平。使用Hall测试250℃ 72 h汞饱和退火后的超晶格结构材料,测试结果显示77 K下材料呈p型,p型浓度2.67×10¹⁶cm⁻³,迁移率73.3 cm²/Vs。掺杂的As元素在250℃即被激活,HgTe/CdTe超晶格材料As掺杂工艺达到设计目的。

审核编辑:彭菁

-

探测器

+关注

关注

15文章

2743浏览量

75491 -

测温仪

+关注

关注

5文章

403浏览量

29124 -

晶格

+关注

关注

0文章

96浏览量

9597

原文标题:分子束外延HgTe/CdTe超晶格工艺研究

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

简述LED衬底技术

应力对LaAlO3/BaTiO3超晶格结构及性能的影响

石墨烯增强铜基复合材料制备工艺及性能的研究进展

硅基复合衬底上分子束外延HgTe/CdTe超晶格结构材料工艺研究

硅基复合衬底上分子束外延HgTe/CdTe超晶格结构材料工艺研究

评论