概述

BAP(BIST Access Port),即内建自测试访问接口,主要用于In System Test,它要求芯片在已经部署到产品中,甚至芯片正在运行中,可对芯片的memory进行在线、实时地进行测试和诊断。

通常情况下,配置MBIST控制器,需要通过TAP接口启动TAP控制器,通过IjtagNetwork来对相关TDR进行配置,随后TDR使能相关信号对MBIST控制器进行配置,并启动MBIST逻辑进行测试。

而BAP内建自测试访问接口提供了不同于IjtagNetwork的串行访问方式,可不经过IjtagNetwork,用BAP接口直接对MBIST控制器进行配置,由于不再使用IjtagNetwork的串行配置方式,没有了shift cycle,大大缩短了测试时间,代价是需要在BAP接口和BAP控制器之间引入额外的连接。

BAP Architecture

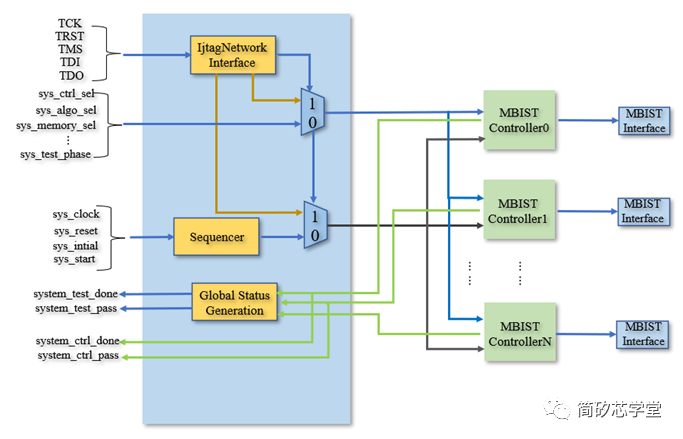

BAP 存储器访问架构由两部分组成:IjtagNetwork访问接口以及BAP的直接访问接口。BAP的连接是由用户配置的,直接连接到Function 逻辑。

图1 BAP存储器访问架构

BAP的组成和功能

BAP的直接访问接口由两部分组成:Sequencer和Global Status Generation。

(1) Sequencer的功能是为MBIST Controller提供时钟、复位、初始化、配置和start启动信号,BAP内的sequencer能够以低延迟的协议启动和定制存储器测试;在这种实现方式中,使用单个sequencer可以最小化BAP的门面积;sequencer的时钟,sys_clock的频率,应该和ijtag_tck相当,频率较低,确保生成的控制信号能够以正确的顺序到达MBIST Controller;

(2) Global Status Generation的功能是采集来自于MBIST Controller的输出信号,这些信号显示了对存储器的测试是否完成、是否通过或者测试失败。

BAP的控制方式

BAP提供了2种对MBIST Controller的控制方式:

(1) 通过TAP接口、TAP Controller以及IjtagNetwork对挂载在IjtagNetwork下的TDRs进行配置,TDRs的输出信号连接到MBIST Controller,从而实现对MBIST Controller的初始化、配置和启动,完成对Memory进行测试;

(2) 通过BAP的直接访问接口(Direct Access Interface)来直接控制MBIST Controller,完成对MBIST Controller的初始化、配置和启动,完成对Memory的测试,而BAP的直接访问接口(Direct Access Interface)的信号来自Function的系统信号。

BAP的其他特性

BAP直接访问接口提供了配置存储器测试的基础选项,可以改变测试算法和操作,用户可以选择使用哪个控制器,决定在哪个step和去对哪个Memory进行测试。例如,如果分配的测试时间有限,可以利用这种灵活性,通过选择具有很少指令的短算法,或者仅在一个控制器上执行MBIST测试。

BAP 直接访问接口支持低延迟的协议配置MBIST控制器,执行GO/NoGo测试,监控测试通过的状态。

Repair的分析也可以通过BAP的直接访问接口进行,分析结果通过访问BISR控制器可以用来进行软件、硬件的增量修复。

BAP的配置方法

BAP的pin的创建和插入是由DFT spec配置的,通过指定 DFT spec中的属性:direct_access 为 on,创建 出BAP的直接访问接口(Direct Access interface)。

MemoryBist{

BistAccessPort {

DirectAccessOptions{

direct_access: on;

}

}

}

对于高级的In-System-Test的用法,使用DFT spec中的ExecutionSelection 字段,根据需求配置系统端的端口。

BAP的时钟连接结构

BAP为每个Functional 时钟创建一个Sequencer,这样可以进一步减少开启停止控制器的时间需求,可以更精确地在同一时钟域中约束Sequencer到MBIST 控制器的关键路径。

BAP 直接访问接口支持两种不同的时钟方案,如何选择依赖于in-system-test是如何执行的,每种方案对sys_clock的连接和信号都有不同的影响。时钟源可以通过 DFT spec中的 direct access clock source字段进行配置,而时钟连接则使用Connection下DirectAccess/CLockDomain字段进行配置。

(1) 当direct access clock source 被指定为 common时,将在BAP中创建一个Test Sequencer,管理与控制器相连接的Memory Test。对于此设置,必须指定Sequencer与系统时钟的连接;

图2 创建一个总的Sequencer

(2) 当direct access clock source 指定为 per bist clock domain时,将在BAP内部为每个MBIST时钟域创建一个单独的Sequencer,每个Sequencer的sys_clock会自动连接到 对应时钟域的MBIST的时钟。

图3 每个时钟域创建一个单独的Sequencer

(图2、图3参考来源:Tessent MemoryBIST User’s Manual)

sys_test_done和sys_test_pass信号的采样

对于单个和多个sequencer的实现方式,采样sys_test_done/sys_test_pass的信号输出有略微不同。

对于单个sequencer的情况,全局的sys_test_done,sys_test_pass状态信号,以及每个controller的sys_ctrl_pass和sys_ctrl_done状态信号是不会寄存在BAP接口中的。这些信号直接来自于各个MBIST Controller的DONE和GO信号,可能来自不同的时钟域。

针对这种情况,需要考虑怎样在Function逻辑中捕获这些信号去避免潜在的跨时钟域的问题。可使用由sys_test_clock或者其他合适的Function时钟驱动的同步单元对sys_test_done和sys_test_pass输出做同步。

针对多个sequencer的情况,不用考虑PASS、DONE的同步问题。

总结

本文主要介绍了BAP直接访问接口的概念、架构、控制方式、配置方法、时钟连接结构和sys_test_done/sys_test_pass信号的采样。BAP提供了相比IjtagNetwork更加便捷、非串行的对MBIST的配置方式。该方式大大缩短了测试时间,提高了DFT的效率。

-

控制器

+关注

关注

114文章

17860浏览量

195018 -

存储器

+关注

关注

39文章

7753浏览量

172158 -

时钟源

+关注

关注

0文章

111浏览量

16813 -

时钟驱动器

+关注

关注

0文章

124浏览量

14407 -

DFT设计

+关注

关注

0文章

11浏览量

9093

发布评论请先 登录

MBIST测试期间的总线错误怎么解决?

如何将时钟频率和周期值传递PWM配置结构

L220 MBIST控制器技术参考手册

CoreLink 2级MBIST控制器L2C-310技术参考手册

ARM L210 MBIST控制器技术参考手册

Cortex-A9 MBIST ControllerTechnical Reference

STM32入坑(七)使用HSI配置系统时钟

78M6610+LMU/BAP - (Maxim Integrated) - PMIC - 能量计量

MBIST BAP的配置方法与时钟连接结构

MBIST BAP的配置方法与时钟连接结构

评论