同构(homogeneous)多核:单片机中,多个Core的结构相同,各个Core用的指令集相同。 异构(heterogeneous)多核:单片机中,多个Core的结构不同,不同的Core架构,使用不同的指令集。

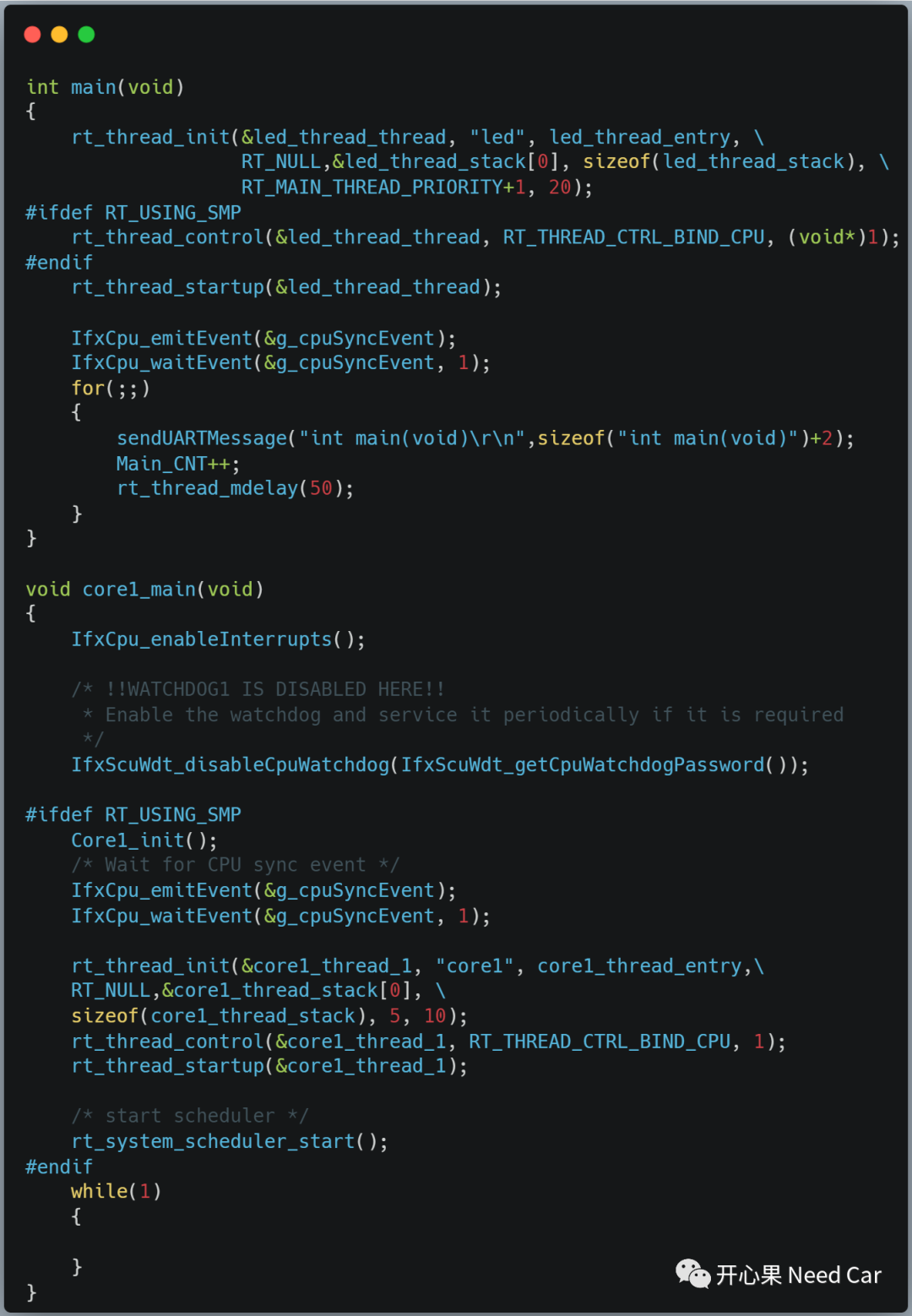

本文基于TC397+Tasking实现SMP(Symmetric Multi-Processing,对称多处理),这里的多核属于同构多核。相对于SMP,AMP(Asymmetric Multi-Processing,非对称多处理)主要用于异构多核处理。

本文,主要记录RTThread多核实现过程中的"雷区"。

1、RTThread多核实现细节

(一)各Core实现硬件初始化

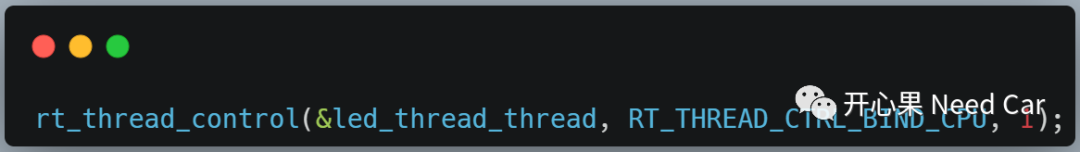

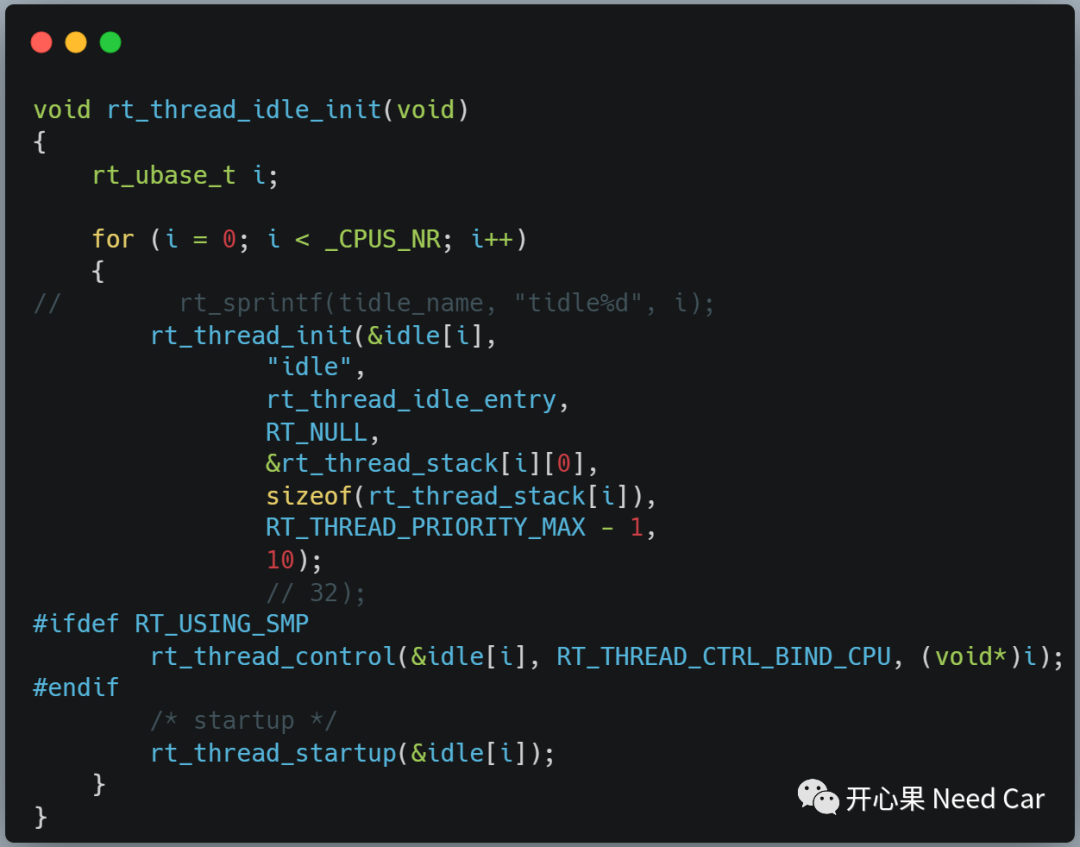

(二)任务初始化

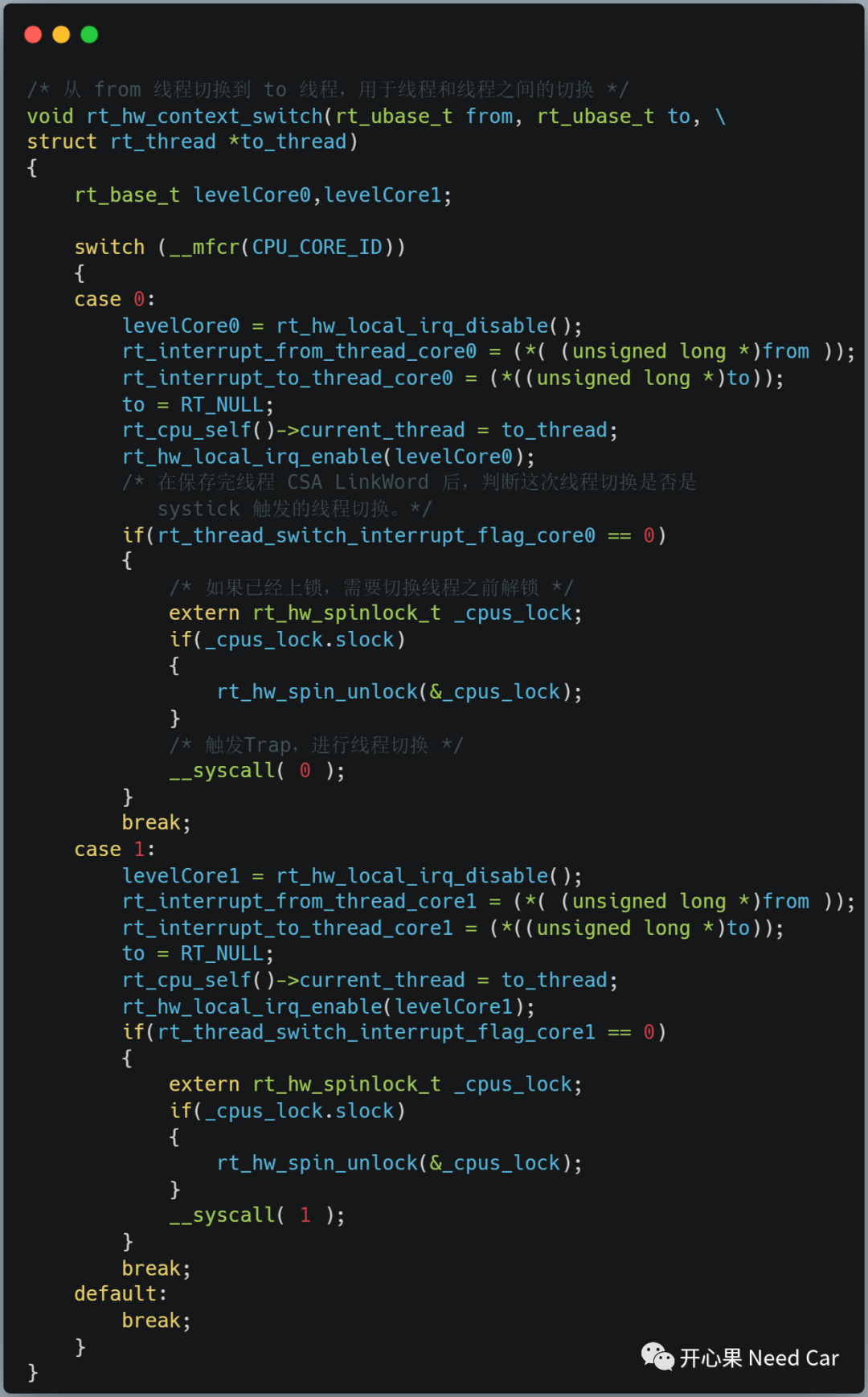

(三)线程间任务切换

如果不是systick触发的线程切换,即:由于线程状态挂起触发的线程切换时,需要判断线程是否上锁,如果已经解锁,则需要解锁之后在进行线程切换,避免死锁。多核rt_hw_context_switch()的接口实现如下所示:

(四)中断切换标志置位时机

每次程序进入系统心跳中断服务例程时,需要先置位中断切换标志Flag,完成系统心跳的累加后复位。注意:不同于单核处理,多核处理中,此处还需要对中断切换进行处理,即:判断程序是否超时,如果超时,则对应的pcpu->irq_switch_flag置位,需要进行中断线程切换处理。代码实现如下所示:

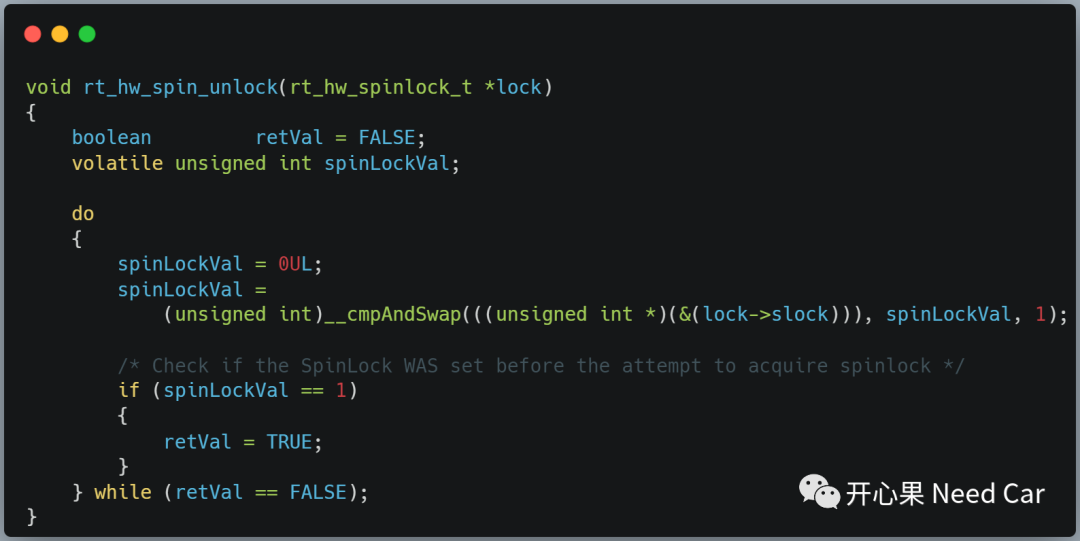

(五)线程上锁/解锁操作

上锁处理,对应代码实现如下所示:

解释:__cmpswapw((address), ((unsigned long)value), (condition) ),上锁处理时,如果address处的值==condition,则将value值赋写到address位置。在Tricore架构中,__cmpswapw操作是原子操作,可以避免多核的并行访问。

解锁处理,对应的代码实现如下所示:

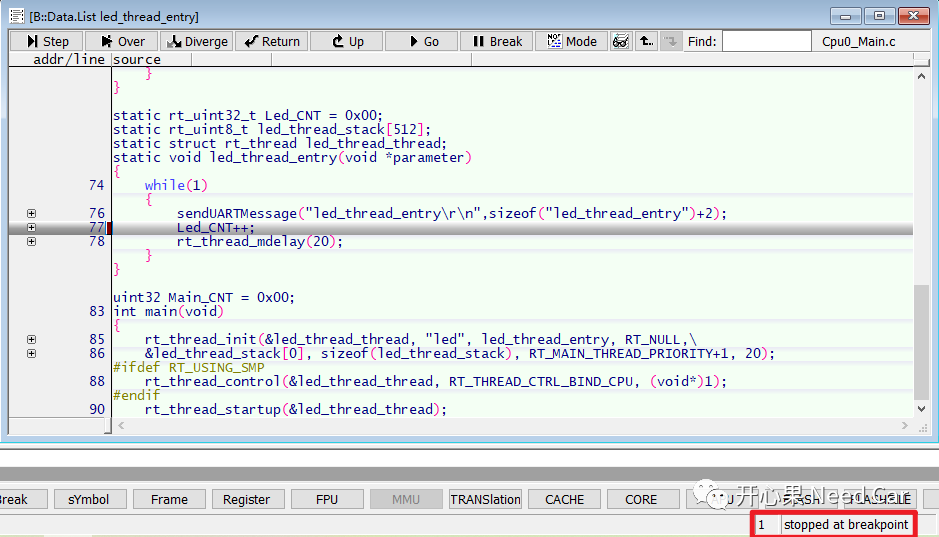

(八)确认线程是否在目标Core运行

如果想确认线程是否在目标Core运行,在目标线程设置一个断点(Breakpoint)即可,如下所示:

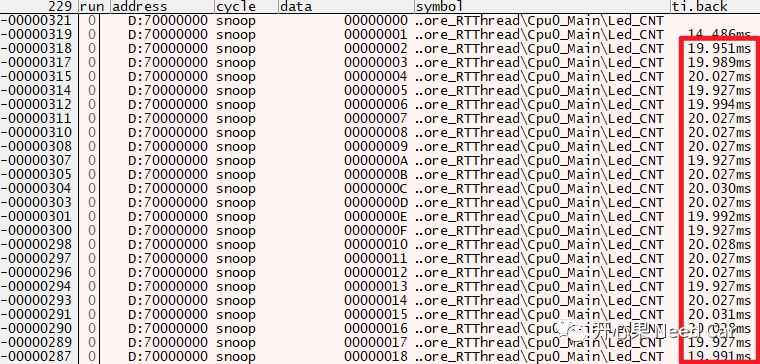

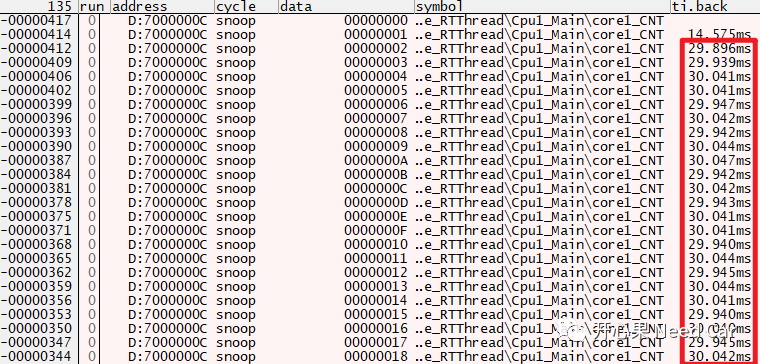

2、RTThread任务调度

(三)core1_thread_1运行周期

2、源码链接

多核与单核的切换,在rtconfig.h文件中,使能或者关闭宏RT_USING_SMP即可打开/禁用SMP。

本文的RTThread中,启用了2个Core(主核Core0,一个从核Core1),如果需要启用更多的从核,可以在本文的基础上打开其余从核,其余从核的处理与Core1类似。

受限于时间和我的水平,本文在零零碎碎的时间里整理完,实现未必最优。而且,我并未严格的按照RTThread的架构处理,写的稍微有些随心所欲。大家可以基于我的工程进行调试和二次开发,以便于达到理解OS内核、任务切换等相关知识。

源码链接地址如下:

https://github.com/Kaixinguo2021/Tasking_TC397_MultiCore_RTThread.git

往期精彩回顾

Autosar往期精彩文章汇总:151~200

Autosar往期精彩文章汇总:201~251

NVM基础:解读"切页"的头部信息

诊断基础:Event内存管理

Autosar通信模块COM:Update-Bits详解

Lin总线基础:为什么Master节点需要外接上拉电阻

———————End———————

-

RT-Thread

+关注

关注

32文章

1540浏览量

44257

原文标题:基于Tricore架构的RTThread多核实现

文章出处:【微信号:RTThread,微信公众号:RTThread物联网操作系统】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何通过交替式几何处理实现更优的多核 GPU 扩展

RTThread支持内存保护功能吗?

CherryUSB和RTThread自带的USB如何合理使用?

请问在移植rtthread nano版时官网里面系统时钟函数在哪里实现的?

Art-Pi2的BootLoader用rtthread有什么特殊的作用吗?

rtthread 5.20 安装 systemview 2.52a 出错的原因?

移植rtthread_NANO之后SPI通讯不了怎么解决?

TC3XX /TC1.6.2OCDS如何通过软件启用核心调试控制器?

Art-Pi2的BootLoader用rtthread有什么特殊的作用吗?

【迅为电子】10路UART、1TOPS的NPU、2路网口、异构多核架构、超高性价比!RK3562核心板强烈推荐

基于Tricore架构的RTThread多核实现

基于Tricore架构的RTThread多核实现

评论