后台有很多工程师朋友留言咨询,其中很大一部分问题都与PCB生产相关,不外乎是一些没有提前考虑到的生产隐患,从而导致废板或返工等,确实比较浪费时间和成本。

所以本期内容,小编将PCB常见设计缺陷问题都进行了汇总,希望大家能够提前规避生产风险,助力PCB一板成功!

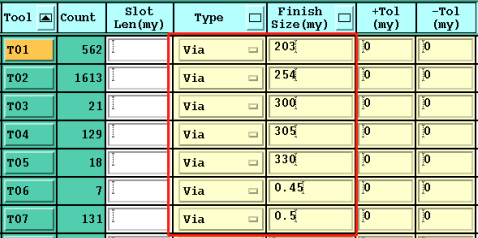

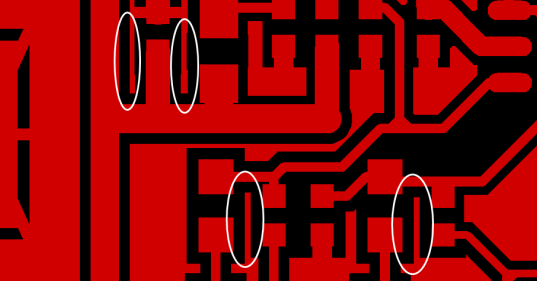

钻孔类问题

【问题描述】

此类文件设计异常,无论孔属性是有铜还是无铜,都会给工程带来困扰

【品质风险】

此类设计容易孔属性制作错误

【可制造性建议】

有铜孔线路设计孔环,无铜孔线路不要设计走线和孔环

【问题描述】

无导线相连的孔, 原稿文件或者分孔图定义有铜孔

【品质风险】

给工厂造成困扰,容易造成孔属性错误

【可制造性建议】

孔属性定义正确

【问题描述】

有焊盘的情况下,原稿文件定义为无铜孔(常规应该是有铜孔)

【品质风险】

给工厂造成困扰,容易造成孔属性错误

【可制造性建议】

孔属性定义正确

【问题描述】

槽孔和圆孔叠在一起无法判定是按槽孔做,还是按圆孔做,或是都做出

【品质风险】

容易造成漏做圆孔

【可制造性建议】

如果都需要钻出来,就都设计在钻孔层,如果圆孔无需钻出,就取消圆孔设计

【问题描述】

槽孔设计在分孔图层

【品质风险】

容易造成槽孔丢失

【可制造性建议】

槽孔设计在钻孔层

【问题描述】

钻孔层设计了圆孔, 分孔图设计了槽孔。容易造成槽孔漏失

【品质风险】

容易造成槽孔丢失

【可制造性建议】

槽孔设计在钻孔层

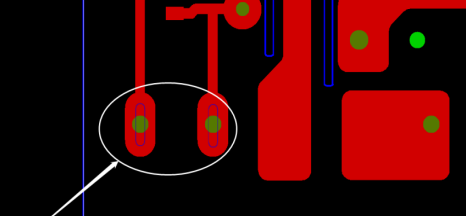

【问题描述】

插件孔设计过近,为保证阻焊桥, 导致焊盘严重削变形

【品质风险】

容易造成焊盘变形,焊接面积变小,虚焊等影响

【可制造性建议】

成品孔径做小,或者孔间距做大一点

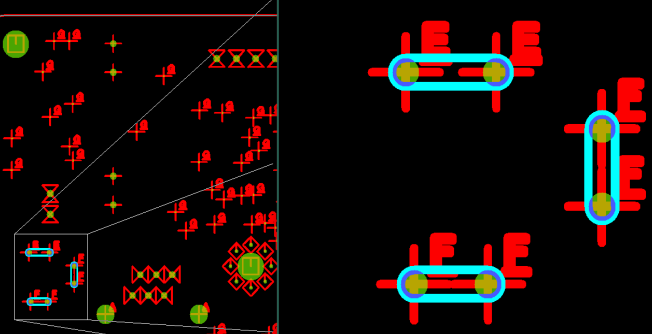

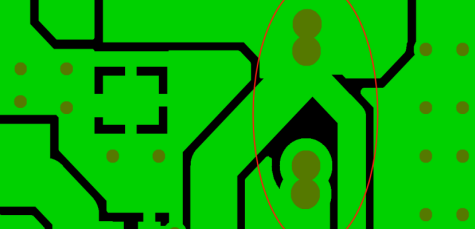

【问题描述】

8字孔设计, 会导致孔铜毛刺严重

【品质风险】

容易造成孔避毛刺,卷铜严重

【可制造性建议】

8字孔拉开间距,或者设计成槽孔

【问题描述】

阻焊塞孔过孔极差不要超过0.2mm

【品质风险】

容易塞孔刀数过多,影响塞孔效果

【可制造性建议】

建议过孔不要设计多种孔径, 孔极差不要超过0.2mm

【问题描述】

过孔距离板边设计过近

【品质风险】

容易板边过孔漏铜

【可制造性建议】

过孔距离板边大于10MIL以上

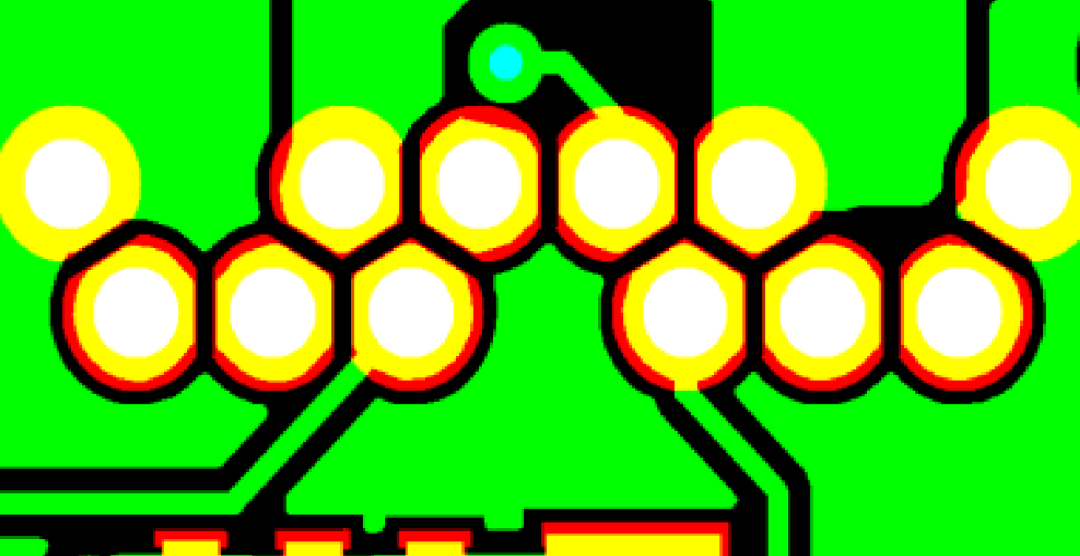

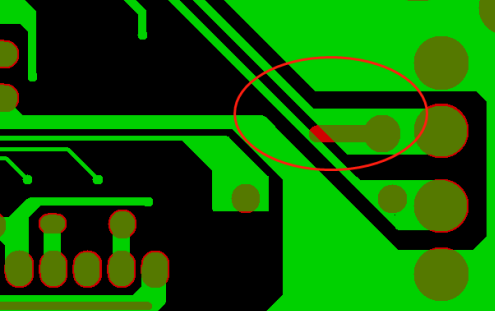

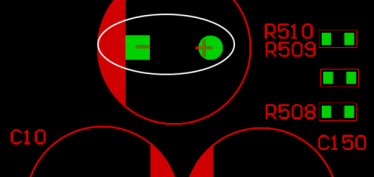

【问题描述】

钻孔钻在IC和小焊盘上

【品质风险】

造成焊接面积变小。焊盘断裂,引起虚焊等可能

【可制造性建议】

建议过孔尽量避开小焊盘

滑动查看更多

线路类问题

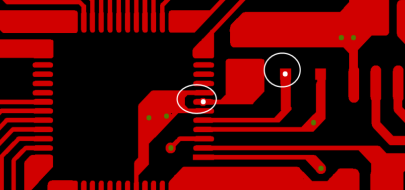

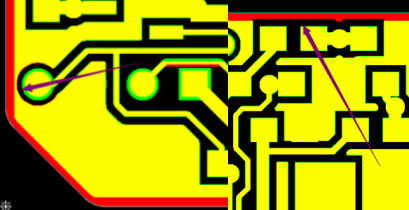

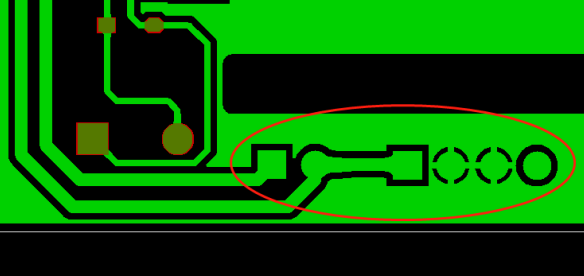

【问题描述】

此类断头线,极容易造成生产短路

【品质风险】

极容易造成生产短路

【可制造性建议】

设计时尽量避免设计此类断头线

【问题描述】

设计板边裸铜带,不能每层都设计,容易让后端跟铣带搞混

【品质风险】

容易判定成铣带,导致板边裸铜带丢失

【可制造性建议】

裸铜带只设计在阻焊层

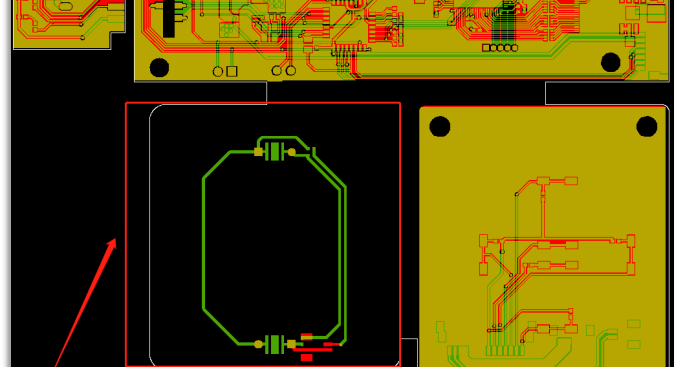

【问题描述】

残铜率相差太大的板子,不要组合在一起制作

【品质风险】

导致残铜率极低面铜不均

【可制造性建议】

不要组合在一起制作

【问题描述】

布线铜皮叠线不建议or各种线(如阻抗线)大小做区分

【品质风险】

增加工程制作时间和成本

【可制造性建议】

铜皮和走线大小做区分

【问题描述】

布线铜皮叠线不建议or各种线(如阻抗线)大小做区分

【品质风险】

增加工程制作时间和成本

【可制造性建议】

铜皮和走线大小做区分

【问题描述】

不要设计此类断头线

【品质风险】

工厂无法判定此类断头线是否正常,增加了沟通成本

【可制造性建议】

设计要保证资料常规性。

【问题描述】

板边铺铜注意避开铣刀位

【品质风险】

工厂默认为此类铜宽为无作用铜宽,可能对资料产生影响

【可制造性建议】

铺铜注意避开铣刀位

滑动查看更多

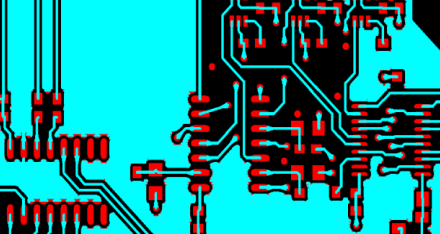

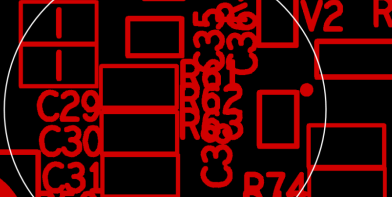

阻焊类问题

【问题描述】

系统下单过孔盖油的Gerber资料设计过孔开窗

【品质风险】

容易造成过孔方式错误

【可制造性建议】

资料过孔开窗和系统过孔方式 需保持一致

【问题描述】

线路有焊盘,阻焊未设计开窗

【品质风险】

容易造成焊盘盖油

【可制造性建议】

线路有焊盘, 阻焊需要设计开窗

【问题描述】

阻焊设计锡线过长

【品质风险】

锡线过长,漏铜

【可制造性建议】

注意锡的长度

滑动查看更多

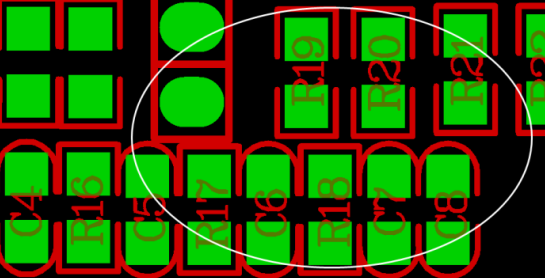

丝印类问题

【问题描述】

文字不要设计在字符框内

【品质风险】

工程常规是直接套除,容易造成字符丢失

【可制造性建议】

需要做出来的字符,不要设计在焊盘上

【问题描述】

字符的字宽字高不要设计过小

【品质风险】

字符宽度高度过小,容易造成字符模糊

【可制造性建议】

字宽字高设计需要大于30MIL以上,字宽需要大于5MIL以上

【问题描述】

字符不要设计重叠

【品质风险】

叠字,造成字符模糊

【可制造性建议】

设计过程中,不要设计叠字

【问题描述】

不要把极性符号,隐藏起来

【品质风险】

造成极性符号丢失

【可制造性建议】

重要的字符一定和焊盘保留安全间距

滑动查看更多

板边类问题

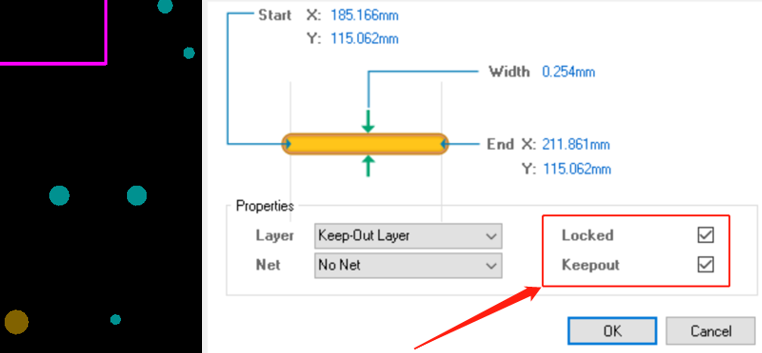

【问题描述】

外形不要被锁起来

【品质风险】

容易造成内槽丢失

【可制造性建议】

不要把内槽锁起来

【问题描述】

内槽宽度设计不足0.8MM

【品质风险】

行业内最小锣刀0.8MM

【可制造性建议】

内槽设计大于0.8MM

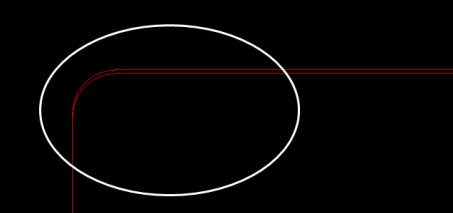

【问题描述】

外形不要设计重线

【品质风险】

容易造成外形公差错误

【可制造性建议】

保证外形的唯一性

滑动查看更多

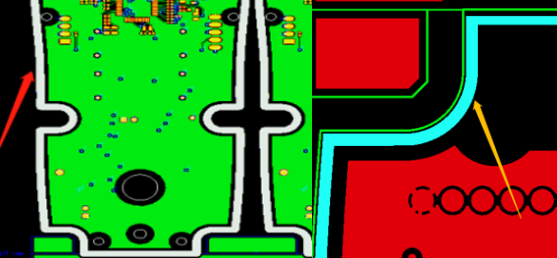

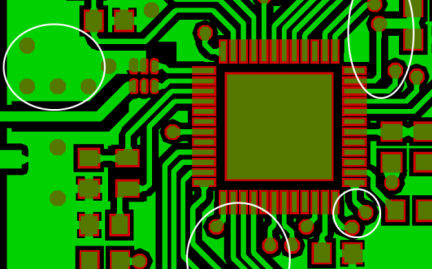

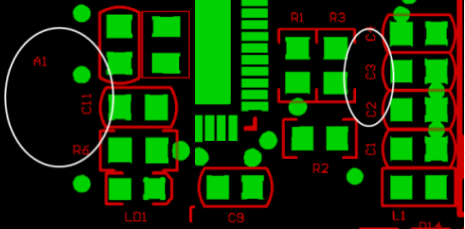

拼版类问题

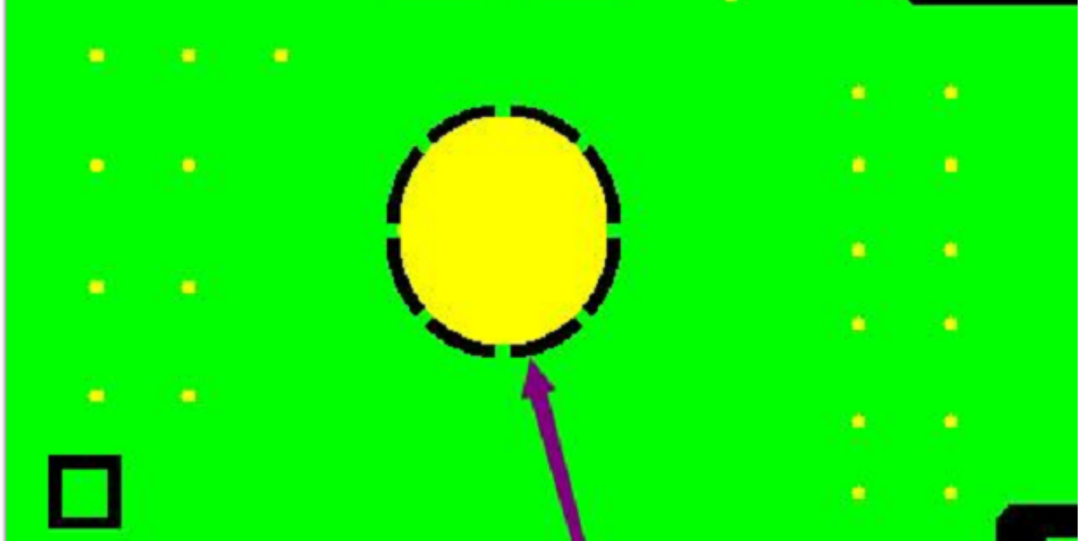

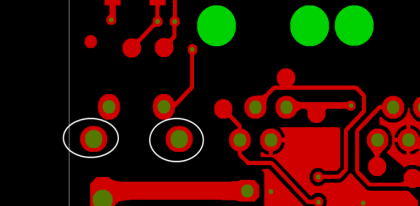

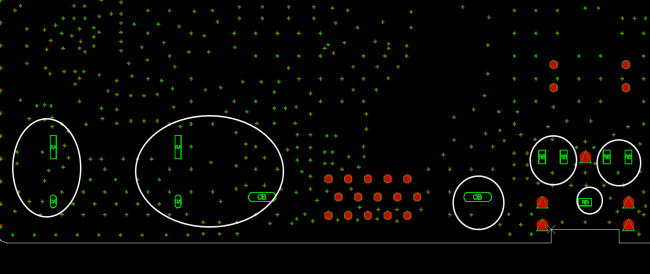

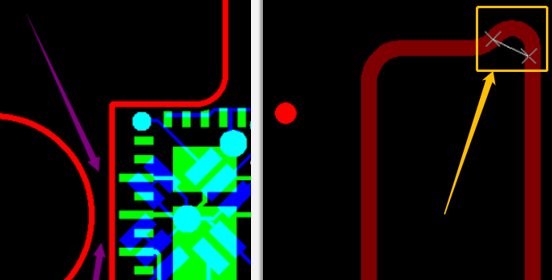

【问题描述】

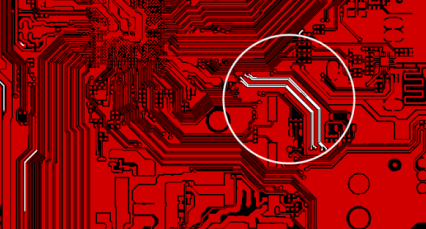

设计拼版, 一定要考虑到怎么分板, 左图V割困难

【品质风险】

容易V割报废

【可制造性建议】

圆圈位置拉开间距

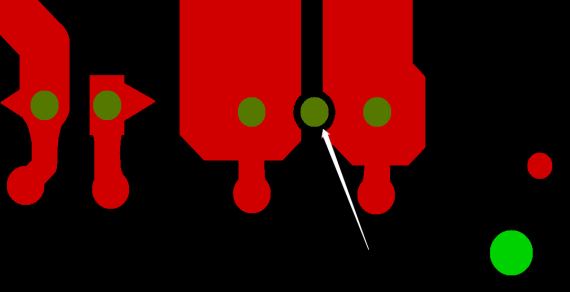

【问题描述】

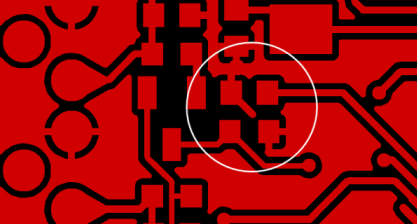

V割线不在一个水平线上

【品质风险】

V割漏铜,尺寸偏差

【可制造性建议】

V割的外形,一定设计在一个水平线上

【问题描述】

此类工艺边设计,悬空位置较大,容易断边

【品质风险】

容易断边,V割弹板

【可制造性建议】

可以增加副板,邮票连接

【问题描述】

此类设计也需要添加副板邮票孔连接

【品质风险】

V割容易偏位,断板等

【可制造性建议】

可以增加副板,邮票连接

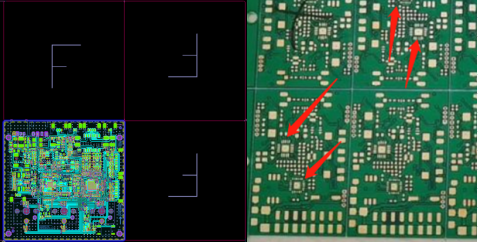

【问题描述】

矩形或者圆形的板, 注意拼版方向的表达

【品质风险】

容易造成拼版方式错误

【可制造性建议】

用F来表示拼版方向, 或者板内物件来表示拼版方向

滑动查看更多

设计完PCB后,一定要做分析检查,才能让生产更顺利,这里推荐一款可以一键智能检测PCB布线布局最优方案的工具:华秋DFM软件,只需上传PCB/Gerber文件后,点击一键DFM分析,即可根据生产的工艺参数对设计的PCB板进行可制造性分析。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

华秋DFM软件下载地址(复制到电脑浏览器打开):

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

专属福利

上方链接下载还可享多层板首单立减50元

每月1次4层板免费打样

并领取多张无门槛“元器件+打板+贴片”优惠券

审核编辑 黄宇

-

PCB设计

+关注

关注

396文章

4907浏览量

94078

发布评论请先 登录

PCB设计的常见问题

PCB设计的常见问题

评论