误码仪的使用方法

误码仪(Error Code Monitor)是一种用于检测和识别数据传输中发生的错误的测试设备。下面是一般误码仪的使用方法:

1. 连接设备:将误码仪与需要进行测试的数据传输设备(例如路由器、交换机等)进行连接。确保连接正确并稳定。

2. 配置测试参数:根据需要的测试目的和要求,配置误码仪的测试参数。例如,可以设置特定的传输速率、数据包大小和传输模式等。

3. 启动测试:启动误码仪的测试功能,开始发送测试数据包到被测设备。根据配置的参数,误码仪会模拟发送各种数据传输情况,包括正常传输和出现错误的情况。

4. 监测和记录结果:误码仪会监测传输过程中的错误情况,并记录错误码和其他相关的统计信息。可以在误码仪上查看实时结果,也可以将结果保存到外部设备或计算机上进行分析和后续处理。

5. 分析和解释结果:根据误码仪记录的结果,可以进行错误分析和解释。例如,可以确定出现错误的具体原因和位置,评估传输的质量和可靠性。

6. 调整和改进:根据测试结果,可以对数据传输设备进行调整和改进。例如,优化网络设置、更换故障组件等,以提高数据传输的性能和可靠性。

基于FPGA的误码仪设计案例

本文设计的误码仪由两部分组成:发信机和接收机。

1 发信机

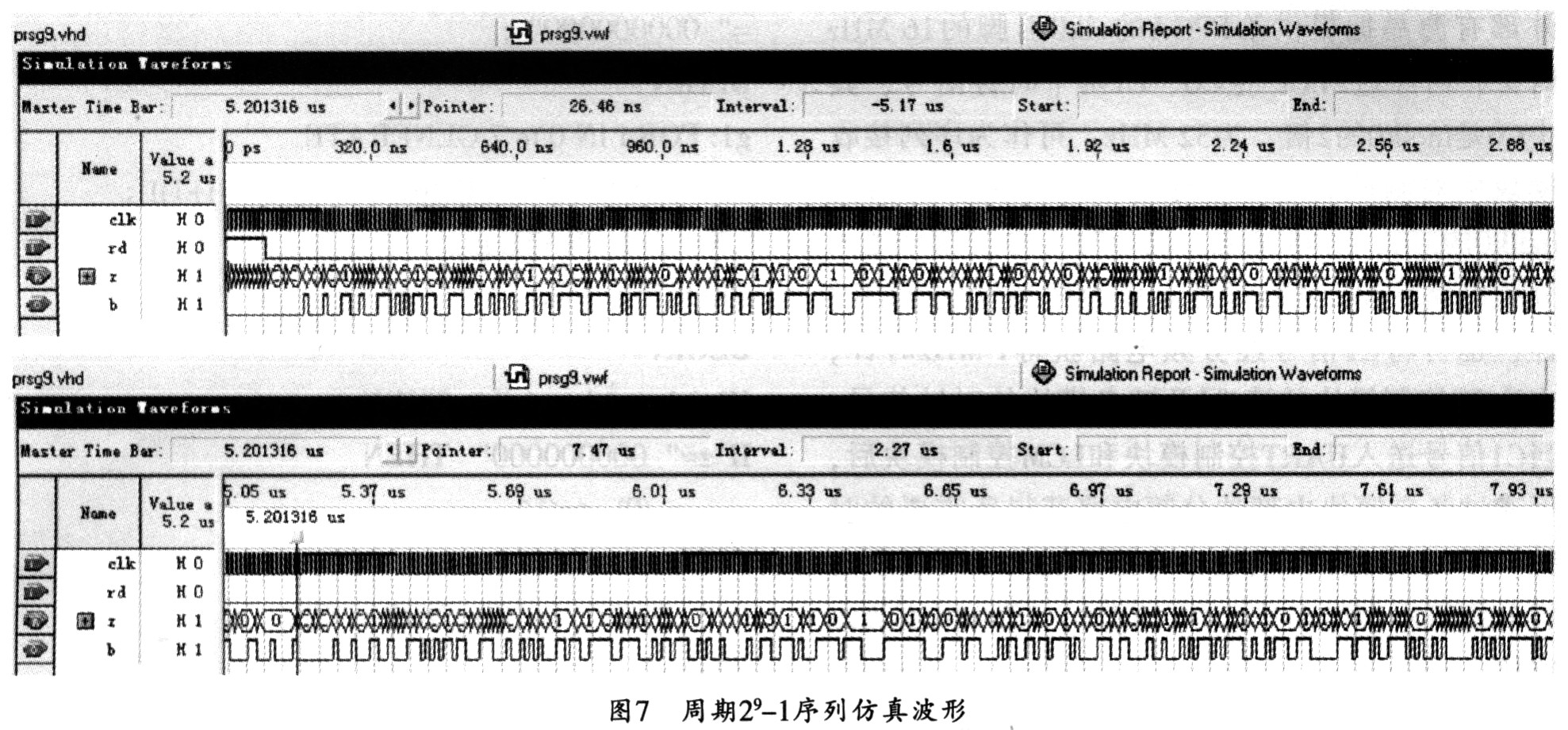

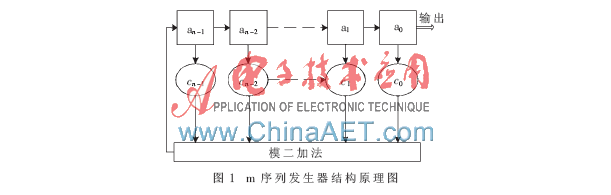

发信机的主要功能是产生具有随机特性的伪随机m 序列,通过FPGA 由VHDL 编程实现。伪随机序列产生原理如下:

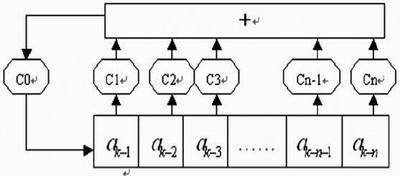

图1 伪随机序列产生原理图

其中,ak-i是各移位寄存器的状态,Ci对应各寄存器的反馈系数,为1表示参与反馈,为0不参与反馈。反馈函数为:

当级数n 和反馈系数一旦确定,则反馈移位寄存器的输出序列确定了,m序列的一个重要的性质是:任一m序列的循环移位仍是一个m序列,序列长度为m = 2n-1 。

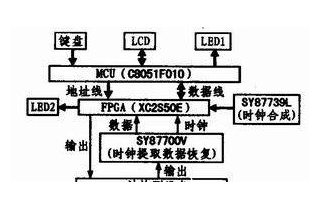

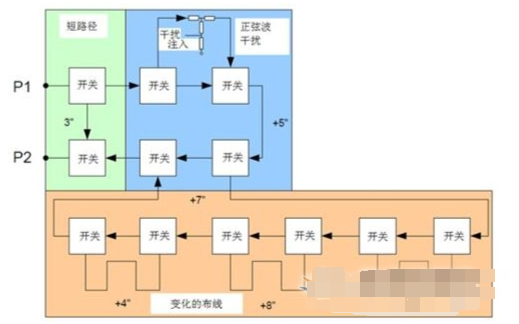

2 接收机

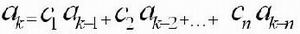

接收机主要由时钟同步模块、状态同步模块组成,其功能框图如图2 所示。

图2 误码器接收机功能框图

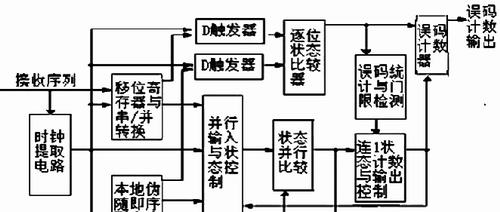

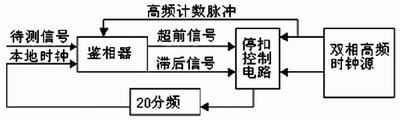

2.1 时钟提取模块

本单元所采用的时钟提取方法是采用新的积分鉴相来实现的,通过在一个时钟周期内对码元进行积分,判断超前滞后,从而极大

的降低了因干扰信号的出现导致误调的可能性。

时钟提取的原理图如下:

图3 时钟提取原理图

误码仪的测试原理

误码仪通过模拟发送和接收数据来进行测试,其测试原理如下:

1. 数据生成:误码仪根据配置的参数生成用于测试的数据信号。这些数据通常是经过编码和调制处理的数字信号,模拟真实的数据传输。

2. 误码注入:误码仪将生成的数据信号注入到被测设备的输入端口。这样,误码仪就可以模拟真实环境中的数据传输。

3. 错误模拟:误码仪会在注入的数据信号中引入各种错误,以模拟传输过程中可能发生的错误情况。这些错误可以是比特错误、帧错误、丢包、延迟等。

4. 错误检测:被测设备接收到误码仪注入的数据信号后,会根据接收到的数据进行错误检测。被测设备会对接收到的数据进行解码和校验,以确定是否存在错误。

5. 错误统计:误码仪会统计和记录被测设备接收到的错误情况,包括错误码、错误类型、错误发生的位置等。这些统计信息可以用于分析和评估数据传输质量。

6. 分析和解释:根据收集到的错误统计信息,可以对数据传输进行分析和解释。可以确定错误的原因和位置,进而优化网络设置或其他相关参数,提高数据传输的可靠性和性能。

误码仪的测试原理是通过模拟和引入错误情况,检测和评估设备在真实环境中的数据传输质量和可靠性。不同的误码仪可能具有不同的测试原理和实现方式。

编辑:黄飞

-

FPGA

+关注

关注

1655文章

22287浏览量

630311 -

寄存器

+关注

关注

31文章

5589浏览量

129068 -

数据传输

+关注

关注

9文章

2076浏览量

67173 -

误码仪

+关注

关注

0文章

12浏览量

10779

发布评论请先 登录

求一种基于FPGA的误码率测试仪的方案

基于FPGA的误码率测试仪的设计与实现

基于DS2172的误码测试仪的设计

一种基于FPGA的误码性能测试方案

基于FPGA的2M误码测试仪设计

基于FPGA的新型误码测试仪的设计与实现

基于FPGA的高速误码测试仪的设计

应用于光互连的高速误码仪的设计

一种基于FPGA的新型误码测试仪的设计与实现

以FPGA为核心的高速误码测试仪设计流程概述

误码仪的使用方法 基于FPGA的误码仪设计案例

误码仪的使用方法 基于FPGA的误码仪设计案例

评论