MOSFET器件是数字集成电路的最小单位,因为MOSFET的开关特性和输出曲线特性,由PMOS和NMOS组成的CMOS门电路,则为数字集成电路最基本的电路结构。而想很好地理解CMOS电路结构,必须先熟悉CMOS反相器电路及其设计和分析方法,因为其他门电路,很多分析方式都是相通的。

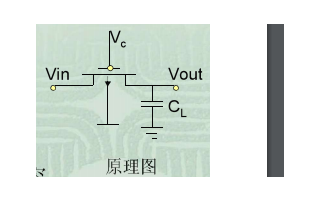

原理图与版图

下图所示是CMOS反相器电路的原理图以及物理版图。物理版图就可以理解为MASK的图形,之前的章节中,我们已经知道,集成电路制造就是根据图形一层一层光刻、生长、注入而实现的,所以无论是什么电路图,最终都必须转换成物理版图的图形,交到工厂去生产。

当然因为知道生产出来的电路,是一层一层堆叠的,所以CMOS反相器电路实际剖面图如下所示。

正常来说VDD与VBBp会连接在一起,接在VDD上,是PMOS的源端,而VBBn与GND会连接在一起,接在地上,是NMOS的源端。当然随着工艺尺寸逐步降低,VBBp和VBBn不会与每一个门电路的VDD和GND连接,而是每几个电路连接一个门电路,这样做的好处是,节省面积,但因此会造成衬底偏置电压(VBS,Substrate Biasing Voltage,偏置与衬底的电压差)与源端产生少许电压差,改变阈值电压VT。一般来说VBS与VT成反比关系,也就是说VBS越大,VT越小,VBS越小VT越大。

对于数字集成电路工程师来说,知道衬底偏置电压对VT有影响影响就好,不需要了解太多了。因为在先进工艺下,为了做好低功耗设计,有专门的Body Biasing Generator(BBG)来微调偏置电压,以便获得功耗与性能之间的取舍。降低VT可以提高性能,但带来较大漏电;提高VT可以减少漏电,但会提高性能。

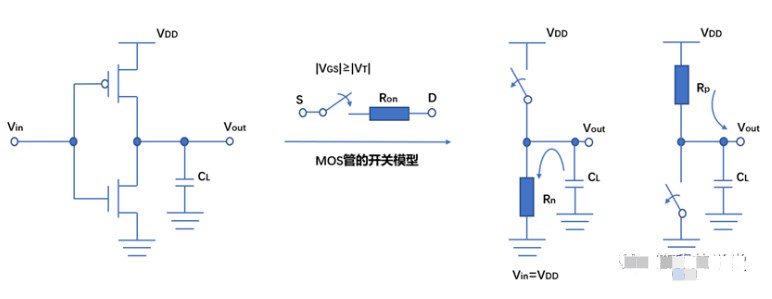

首先看CMOS反相器的电路,与之前不同的是,多了一个CL,负载电容。无论是什么CMOS门电路,其输出一定是要驱动一个负载的,而对于CMOS门电路来说一般负载指的是金属连线与地之间的电容,以及下一级电路输入栅极与地之间的电容。因为MOSFET是电压控制电流,如果把负载电压VDD看成逻辑1,地电势看成逻辑0,那么只是电流是无法实现逻辑传递的,因此负载电容在被电流充电与放电的过程中,完成其节点在VDD与地电势之间跳变,才能真正把逻辑数值传递出去。

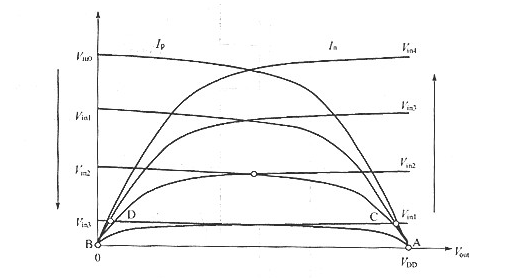

假设PMOS和NMOS使用相同的VT值,则输入电压改变引起输出电压变化的曲线(反相器转移特性曲线)图如下:

- A区域,Vin在0V到VTN之间,因此NMOS截止,PMOS非饱和,但没有电流通路,因此没有电流,输出电压也不会发生变化。

- B区域,Vin在VTN到1/2VDD之间,NMOS处于饱和状态,PMOS处于非饱和状态,对于PMOS来说,VDS不大,因此电流不大,电容放电速度比较慢。

- C区域,Vin在1/2VDD左右,NMOS和PMOS同时处于饱和状态,放电速度突然增大,对于PMOS来说,很快达到饱和状态(VDS增加),而NMOS很快达到非饱和状态(VDS减少),进入D区域。

- D区域,Vin处于1/2VDD到接近(VDD-VTP)区间,NMOS处于非饱和,PMOS处于饱和状态,对于NMOS来说,VDS不大,因此电流不大,电容放电速度较慢。

- E区域,Vin大于VDD-VTP,PMOS截止,没有电流通路,输出电压也就固定在0V。

由以上特性可见,当输入电压为VDD的时候,输出电压为0V,而输入电压为0V时,输出电压为VDD,刚好相反,满足反相器的逻辑关系。

接着我们看一下,输入电压与电路电流的关系:

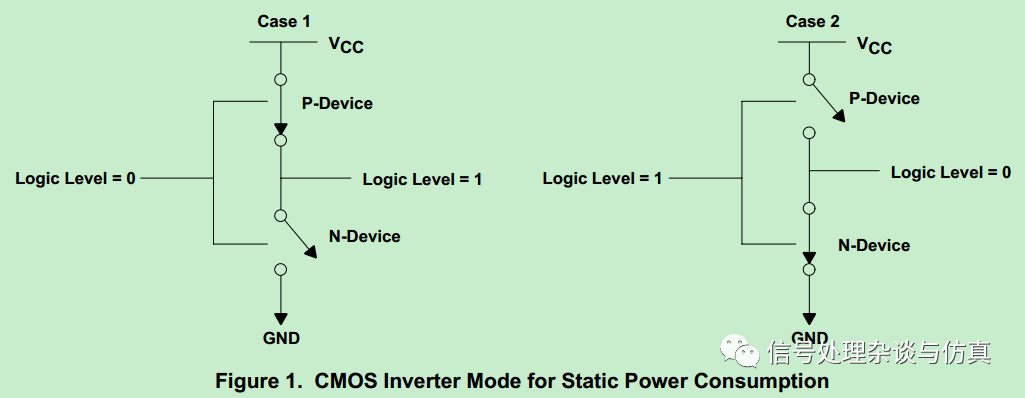

可以看出,只要输入电压小于nMOS的VT,或者大于VDD-|VTP|,则电路是不会产生电流的。只有在这中间区间,才会产生一个比较大的电流,特别是两个管子都处于饱和状态时。这样的好处是只要电路不发生翻转,就不会产生电流,而一旦发生翻转,因为nMOS和pMOS的互补性,会快速实现状态转换,提高性能。

影响CMOS反相器特性的因素

除电源电压外,影响反相器特性的主要有:

- NMOS和PMOS管的阈值电压;

- NMOS的W/L和PMOS管的W/L;

- NMOS和PMOS管W/L值之比。

刚才的分析是假设nMOS和pMOS的阈值电压一样,但实际上可能会有偏差,如果阈值电压不同,则会影响转换曲线的偏移,毕竟开关的时间都不一样了,但峰值电流不会有太大变化,也不会对充电时间有太大影响。当然实际设计的时候,我们尽量让两个管子的阈值相近,以便转换过程尽可能接近于中心位置,减少对噪声容限的影响。

同时阈值越小,中间阶段越大,短路状态也会持续越长的时间。输出曲线斜率越平缓,输出变化越慢。如果想减少短路状态下的能量损耗,需要选择VT值大一些的器件,当然对电容充电时间减少了,性能也会降低。

另一个方面,如果两个管子宽长比越大,则电流越大,等效电阻越小,跨导越大,传输效率越高,对负载充电的性能越高,当然2个管子都处于饱和状态时,电流也会越大。想获得更快的工作频率,更大的宽长比选择是有必要的。

第三点,宽长比之比,是很有意思的。假设当pMOS的宽长比与nMOS宽长比是2:1的时候,传输曲线最陡峭的位置处于1/2 VT的位置,这是最理想的结果。

那么如果我们增加pMOS的宽长比,则曲线就会向右偏移,这意味着如果输入电压在VDD范围不稳定时,输出电压可能发生变化,也就是偏向于VDD的噪声容限减小了。同样的,如果我们减小pMOS的宽长比,则曲线就会向左偏移,这意味着如果输入电压在地范围不稳定,被抬升时,输出电压可能发生变化,也就是偏向于地的噪声容限减小了。

为什么要用CMOS结构电路

这是一个比较奇葩的问题,因为现在已经很少,或者说在数字集成电路设计过程中,已经不会再有人问这个问题了。但是作为入门工程师来说,了解一下历史,可以更好地展望未来。

首先我们要知道一个好的反相器应该有以下4个特质:

- 电压摆幅:接近电源电压好

- 高增益区电压增益:越高越好

- 静态电流:越小越好

- 直流噪声容限:越大越好(转换电平居中)

现在我们回到远古时期,看看老古董都是什么样子的。

有兴趣的小伙伴可以把4种中古反相器都分析一下,我们这里只详细分析以下电阻负载反相器,也就是利用电阻替代pMOS来对电容进行充电。

图中Source与GND直接连接,因此Source电压Vs=0;Gate上的电压Vg就是是Vin,Drain上电压就是Vout。因此Gate与Source电势差Vgs=Vg-Vs=Vin-0=Vin,Drain与Source电势差Vds=Vd-Vs=Vout-0=Vout。

Vgs<=VT时,NMOS不导通,电路没有电流,因此Vout=VDD。

Vgs>=VT后,电路产生电流,CL开始放电,但由于VCC与Vout之间因为电阻的原因一直有通路,因此CL通过NMOS放电的同时,还会有一定的充电,Vout无法达到0V。输入与输出关系曲线如下图所示:

可以看出,电阻负载反相器,在输出逻辑0的时候,是无法达到0V的,有一个小的电压,且同时电路中存在电流。根据好的反相器标准,电阻负载反相器电压摆幅无法达到0V,且存在静态电流。电阻越大,电流越小,且约接近于0V。但电阻的噪声随着频率增加,是无法被接受的,除了本身性能不好外,随着性能的要求,电阻负载反相器一定会被淘汰。

那么这些中古反相器和CMOS反相器差别的对比,如下图所示,如果理想的反相器是目标,只有CMOS反相器是最接近于这个目标的。

反相器的直流参数

之所以说反相器的分析非常重要,是因为在芯片中反相器的应用,除了作为逻辑电路外,还会作为增大驱动能力的IO Buffer以及放大器基础结构(放大器电路不是数字集成电路设计必须学习的)。

所以反相器的直流参数就尤为重要了,会看芯片datasheet的小伙伴应该很容易理解这些参数。

首先是VIL和VIH,分别是输入低电平的最高值以及输入高电平的最低值,这意味着如果给一个芯片送信号(假设芯片IO输入是一个buffer),那么输入的信号只有稳定在VIL以下以及VIH以上,才能够被正确的识别到。

问题回到pMOS和nMOS的宽长比之比,小伙伴们可以思考一下,如果修改宽长比之比,对于VIL和VIH有什么影响呢?

VOL和VOH分别指输出低电平的最高值,和输出高电平的最低值。如果是中古反相器Buffer,那么输出值就会与地和供电电压VDD有一些不同,但在当今CMOS结构的电路中,基本上就是地电势和供电电压VDD。

VNL和VNH分别指输入低电平抗干扰以及输入高电平抗干扰,在保证输出电平不变的条件下,输入电平允许波动的范围。它们表示门电路的抗干扰能力,这两个值当然越大越好。VNH可以理解为驱动门的VOH-负载门的VIH,而VNL可以理解为负载门的VIL-驱动门的VOL。

所以如果要提高VNH和VNL,那么就需要尽量让VOH和VOL接近于VDD和0V(CMOS电路驱动时,输出摆幅满足此要求,但连线过长,寄生电阻可能产生的压降就会降低VOH或太高VOL,实际电路时要注意这一点),而VIH和VIL尽可能的接近于中心位置。也就是说约接近于理想反相器,那么VNH和VNL越大。

回忆一下,影响CMOS反相器特性的因素,现在可以理解,为什么我们尽量使用更大的VT值,以及配比PMOS和NMOS的宽长比,使其传输曲线的中心电压处于1/2 VDD的位置了。

反相器设计如此,其实后续我们接触到的门电路设计都会因为VNH和VNL的需要,都会希望传输曲线都能尽可能地靠近1/2 VDD。

-

CMOS

+关注

关注

58文章

5163浏览量

233394 -

MOSFET

+关注

关注

141文章

6578浏览量

210169 -

反相器

+关注

关注

6文章

256浏览量

42717 -

负载电容

+关注

关注

0文章

128浏览量

10276 -

PMOS管

+关注

关注

0文章

79浏览量

6376

发布评论请先 登录

相关推荐

virtuoso中进行CMOS反相器和静态寄存器的电路设计

CMOS反相器构建Big Muff

CMOS反相器工作原理及传输特性

MOS反相器和CMOS反相器的详细资料说明

CMOS反相器电路及其设计和分析方法

CMOS反相器电路及其设计和分析方法

评论