在数字设备中,数据的传输是大量的,传输的数据都是由0和1构成的进制数字组成。在数据传输或数字通信中,由于存在噪声和干扰,二进制信息的传输可能会出现差错(0变为1,或者1变为0)。

为了检验这种错误,常采用奇偶校验的方法。即在原二进制信息码组后添加一位检验位(监督码元),使得添加校验位码元后整个码组中1码元的个数为奇数或偶数。若为奇数,称为奇校验;若为偶数,则称为偶校验。

在数据发送端用来产生奇(或偶) 校验位的电路称为奇(或偶)校验发生器;在接收端,对接收的代码进行检验的电路称为奇(或偶)校验器。

一、设计目标:

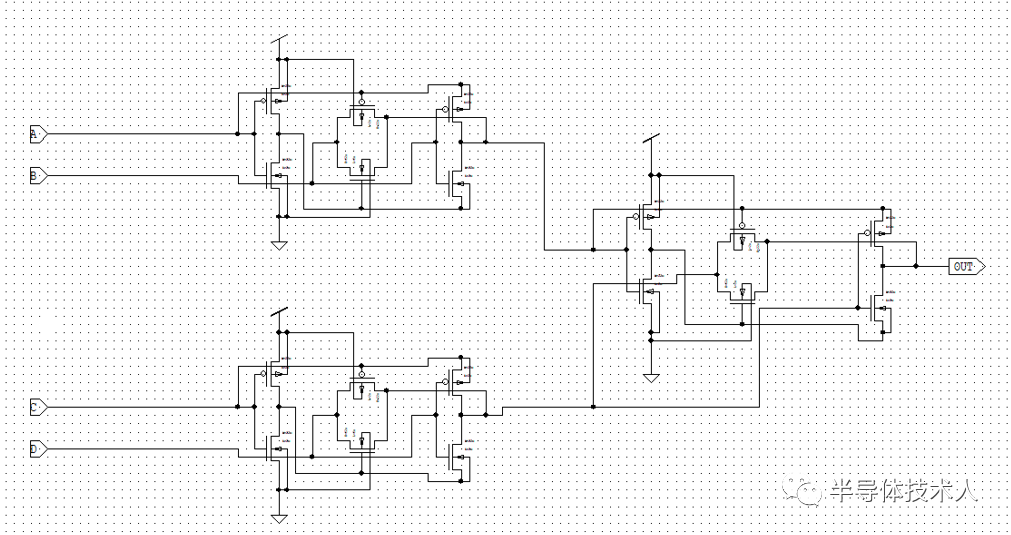

1)设计一个4位奇偶校验器(4位输入中有奇数个1时输出1,偶数个1时输出0),给出电路图,完成由电路图到晶体管级的转化;

2)绘制原理图, 完成电路特性模拟;

3)遵循设计规则完成晶体管级电路图的版图,流程如下:

版图布局规划-基本单元绘制-功能块的绘制-布线规划—总体版图);

4)版图检查与验证( DRC检查);

5)针对版图,给出实现该电路的工艺流程图;

二、设计过程:

电路图:

瞬态特性仿真:

版图:

-

发生器

+关注

关注

4文章

1423浏览量

64409 -

仿真器

+关注

关注

14文章

1048浏览量

86764 -

晶体管

+关注

关注

78文章

10257浏览量

146291 -

奇偶校验器

+关注

关注

0文章

7浏览量

7263 -

DRC

+关注

关注

2文章

156浏览量

37947

发布评论请先 登录

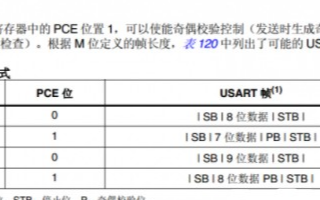

UART中有奇偶校验位和无奇偶校验位的数据传输是怎样的?

DES使用一个56位的密钥以及附加的8位奇偶校验位详细资料说明

STM32的UART奇偶校验注意

怎么设计一个4位奇偶校验器呢?

怎么设计一个4位奇偶校验器呢?

评论