Versal™ 是由多个高度耦合的可配置块组成的自适应计算加速平台(ACAP)。这些块包括NoC、AIE、PL和CIPS(CIPS本身包含不同的域:LPD和FPD)等,启动这些块时,需使用Vivado中的配置集进行配置。

本篇博文是Versal“从零开始”调试系列的首篇。

这么多互连块乍看之下似乎很复杂...但实际不尽然。在本篇博文中,我们将探讨这些启动文件及其使用方式。

这就切入正题...希望您不介意我用首字母缩写词。

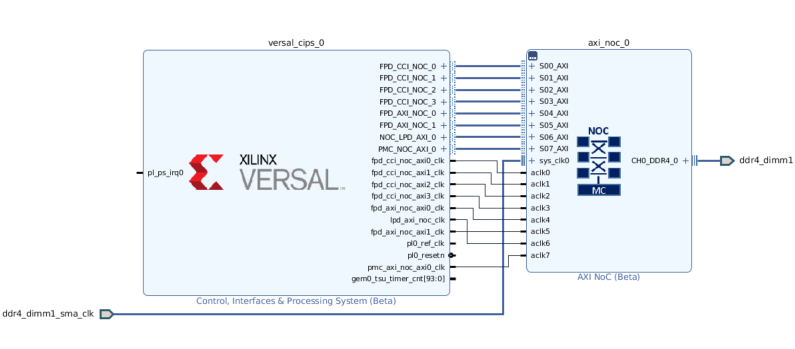

以下我准备的一个基础设计,其中只有CIPS和NoC:

Control, Interfaces, and Processing Subsystem (CIPS)是所有Versal设计的通用IP,包含所有Versal器件通用的硬化IP。

其中主要包含两个域:LDP和FDP。低功耗域(LPD)包含可配置启动器件和I2C。全功耗域(FPD)则包含所有其它可配置IP,如GEM和USB等。此外还有AXI和调试接口,连接到PL、可配置NoC接口、时钟、中断和处理器子系统,全都可在Vivado IP integrator内根据您的设计需求进行配置。

片上网络(NoC)经高度耦合,可连接到PL IP和/或AIE以及DDR存储器控制器。

所有这些配置二进制文件(CDO)都封装到单一容器文件内,此文件称为PDI文件,PDI表示可编程定义文件(Programmable Definition File)。

PDI:

如上所述,PDI包含所有可配置二进制文件。其中还包含用于执行这些二进制文件的可执行文件。

并且,如果PL包含带有存储器映射存储器控制器的MicroBlaze,那么PDI中还包含存储器映射接口(MMI)文件。

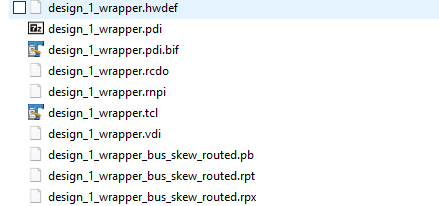

此 PDI 文件将在实现期间创建,并且可包含在 XSA 文件内交付至 Vitis。来看看 impl_1 文件夹:

此处值得注意的两个文件是PDI文件和BIF文件。

启动镜像格式:

启动镜像格式(BIF)文件包含所有启动分区。

让我们来一探究竟:

new_bif:

{

id_code=0x04ca8093

extended_id_code=0x01

id=0x2

image

{

name=WDI_FLAT

id=0x1c000000

partition

{

id=0x01

type=bootloader

file=gen_files/executable.elf

}

partition

{

id=0x09

type=pmcdata,load=0xf2000000

file=gen_files/pmc_data.cdo

}

partition

{

id=0x0C

type=cdo

file=gen_files/lpd_data.cdo

}

partition

{

id=0x0B

core=psm

file=static_files/psm_fw.elf

}

partition

{

id=0x03

type=cdo

file=design_1_wrapper.rcdo

}

partition

{

id=0x05

type=cdo

file=design_1_wrapper.rnpi

}

partition

{

id=0x08

type=cdo

file=gen_files/fpd_data.cdo

}

partition

{

id=0x0D

type=cdo

file=gen_files/subsystem.cdo

}

}

}

下表提取自《Versal 系统软件开发指南》,可用于描述其中每个分区:

| PDI 组件 | 描述 |

|

PLM elf (executable.elf) |

Platform Loader and Manager。 |

|

PLM CDO (pmc_data.cdo) |

器件拓扑 - 固定配置 PMC 配置 - 寄存器写入/读取 |

|

LPD CDO (lpd_data.cdo) |

PS LPD PM 初始化节点命令(SC、LBIST、BISR 和 MBIST) LPD 配置 - 寄存器写入/读取 |

|

PSM elf (psm_fw.elf) |

PSM ELF |

|

CFI 数据 (.rcdo) |

PM 初始化节点命令(清理 PL、HB SC 和 GT MBIST) 寄存器写入 CFU 适用于 CFI 数据的 DMA 锁眼传输命令 寄存器写入/读取 CFU 如无 NPI: 全局信号 GMC_B、GRESTORE 和 GHIGH_B。- 寄存器写入/读取 全局信号 - GWE、EOS、EN_GLOb - 寄存器写入/读取 |

|

() [此文件与以上 .rcdo 文件合并] |

|

|

NPI CDO (.rnpi) |

PM 初始化节点命令(SC、BISR 和 MBIST) NPI 数据加载 - DMA 写入/寄存器写入 如果 CFI 存在: 全局信号 GMC_B、GRESTORE 和 GHIGH_B。- 寄存器写入/读取 NPI 序列 - 寄存器写入/读取 如果 CFI 存在 全局信号 - GWE、EOS、EN_GLOb - 寄存器写入/读取 隔离和 PL 复位命令 |

|

CPM CDO (cpm_data.cdo) |

PM 初始化节点命令(BISR 和 MBIST) 适用于 CPM 和 CPM PCSR 的寄存器写入 |

|

AIE NPI CDO (ai_engine_data.cdo) |

AIE scan clear,BISR - PM 命令 AIE PLL 配置 - 寄存器写入/PM 命令 AIE mem clear - PM 命令 |

|

FPD CDO (fpd_data.cdo) |

FPD 配置 - PM 初始化节点命令(SC、BISR 和 MBIST) 寄存器写入 |

|

子系统 CDO (subsystem.cdo) |

子系统 CDO |

| DONE 位由 PLM 断言有效 |

转储PDI:

用户可以在Vitis中使用Bootgen实用工具来转储和查看PDI中的内容:

bootgen-archversal-dump.pdi

用户可以使用以下Bootgen命令从BIF创建PDI:

bootgen-archversal-image.bif-w-o.pdi

Platform Loader and Manager:

PLM负责加载分区(如上所示)和执行平台管理。所有CDO都加载到RAM中,然后执行。ELF文件直接加载到目标存储器中,然后执行。不支持就地执行。

要调试潜在的PLM故障,可在此处的表 14 中找到错误代码。

在某些情况下,用户可能需要修改Vitis生成的PDI,下面提供了两个常见用例。

调试PLM:

用户可以覆盖PDI中的PLM,如UG1283中的第 129 页所述,也可以重新生成PDI并导出硬件以将修改后的PDI添加到XSA中。

BIF文件如下所示:

new_bif:

{

image

{

{type=bootimage,file=base.pdi}

{type=bootloader,file=plm_debug.elf}

}

}

随后,重新生成PDI。请务必保留PDI文件名(与Vivado生成的文件名相同):

bootgen-archversal-image{filename.bif}-w-o{design_1_wrapper.pdi}

如果用户随后在Vivado中导出硬件,那么,修改后的PDI将被添加到XSA中。

浏览CDO/RNPI文件:

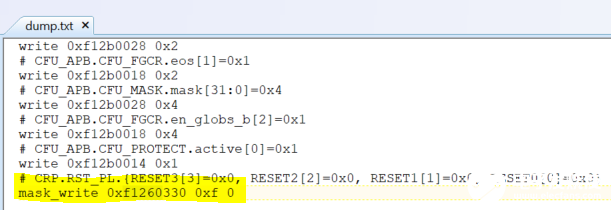

用户可以使用XSCT中的cdoutil将二进制文件转换为可读文本文件。以RNPI为例:

cdoutil-annotate-output-filedump.txt.rnpi

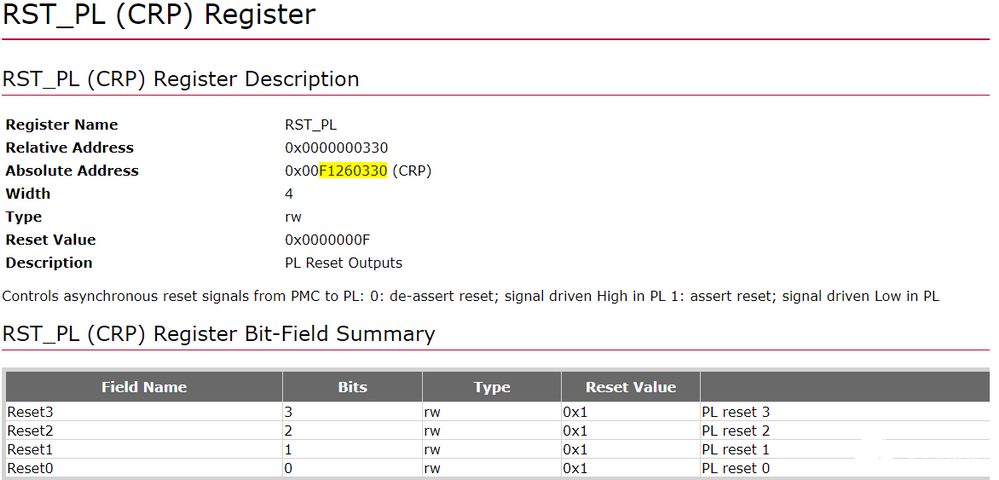

从上表中可以看到,rnpi文件包含PL复位命令。

我们可以在转储后的文本文件中查看这些命令:

在《Versal 寄存器参考资料》中可以交叉引用这些命令:

将定制CDO文件添加到PDI:

用户还可以创建定制CDO文件,并将其添加到PDI中。

例如,我有一个IP,它在CIPS上受PS GPIO控制。

因此,我需要切换此PS GPIO:

首先创建一个txt文件,其中包含您希望在PDI内执行的寄存器写入操作:

version2.0 mask_write0xff0b00180x10x1 mask_write0xff0b02c40x10x1 mask_write0xff0b02c80x10x1 mask_write0xff0b004c0x10x1

随后,使用以下命令将此转换为CDO文件:

cdoutil-output-binary-be-output-filecustom.cdocustom.txt

下一步,导航到Vivado工程目录内的 .runs_0/impl_1 文件夹,打开BIF文件,并追加以下内容(在最后一个 } 内):

image

{

name=custom_cdo

id=0x1234567

partition

{

id=0x12

type=cdo

file=custom.cdo

}

}

随后,重新生成PDI并导出至硬件,更新后的PDI将添加到XSA:

bootgen-archversal-imagedesign_1_wrapper.bif-w-odesign_1_wrapper.pdi

依次单击“File -> Export Hardware (Include Device Image)”(文件 > 导出硬件(包含器件镜像))

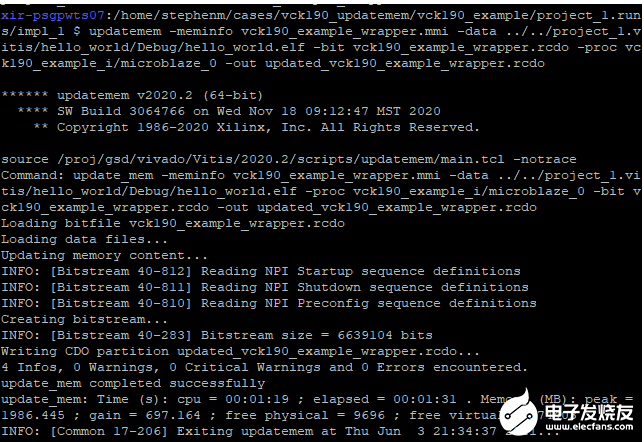

运行Updatemem

如果Versal设计包含 MicroBlaze(含LMB存储器),并且您要使用可执行ELF来更新LMB BRAM,那么同样可以使用以上方法。例如:

浏览至 .runs/impl_0 文件夹,并运行Updatemem。例如,这里我创建了更新后的RCDO。但您也可以保留名称不变。否则,您需要更新BIF文件:

随后,重新生成PDI并导出至硬件,更新后的PDI将被添加到XSA中:

bootgen-archversal-imagedesign_1_wrapper.bif-w-odesign_1_wrapper.pdi

依次单击“File -> Export Hardware (Include Device Image)”(文件 > 导出硬件(包含器件镜像))

总结:

本篇博文并非Versal启动文件的完整指南。

所有这些信息都能在TRM和SSDG中找到。我希望本文能够向用户简要介绍 Versal 启动文件,供用户以此作为起点,按需进一步深入调研。

后续内容

如何在 Vitis 中调试 Versal PLM

在这篇博文中,我们将探讨如何在Vitis™ 中调试Platform Loader Manager (PLM)。

审核编辑:汤梓红

-

NoC

+关注

关注

0文章

43浏览量

12218 -

Vivado

+关注

关注

19文章

860浏览量

71400 -

启动文件

+关注

关注

0文章

16浏览量

2469 -

Versal

+关注

关注

1文章

176浏览量

8542

发布评论请先 登录

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

DXP导出SMT坐标文件的简述步骤详细说明

使用QEMU启动Versal VCK190

在Versal VCK190评估套件上使用器件固件升级(DFU)执行USB辅助启动模式测试

使用QEMU启动Versal VCK190 ACAP

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

Versal启动文件简述

Versal启动文件简述

评论