工程师都在知道在设计的时候会考虑到ESD,通常也会使用到TVS二极管。但是重点在于需要多保护,什么时候不需要保护了?这篇文章会对电路进行模拟。

一、ESD 保护电路的作用

主要就是减少电压和电流,一旦减少,IC的内部ESD保护就可以解决剩下的问题。

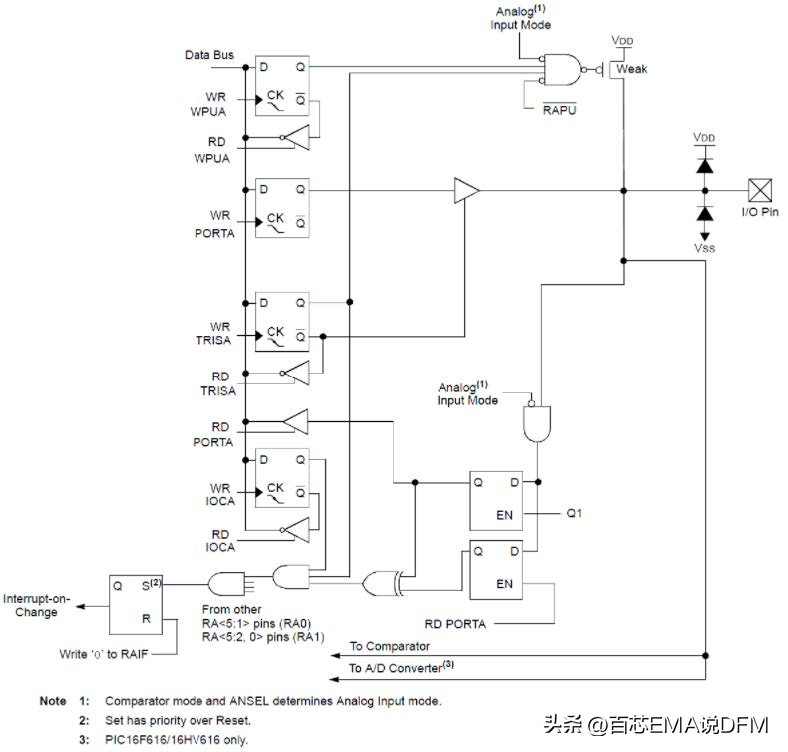

下图显示了普通PIC16控制器的框图,虽然说并不是所有的微控制器/IC都会使用这种完全相同的ESD保护电路,但是会非常相似。通常来说,二极管的尺寸非常小,没有办法在烧毁的情况下处理通过的大量电流。

注意引脚左侧的两个二极管,是内部ESD保护电路。

任意 IO 引脚的 PIC16F616 内部框图

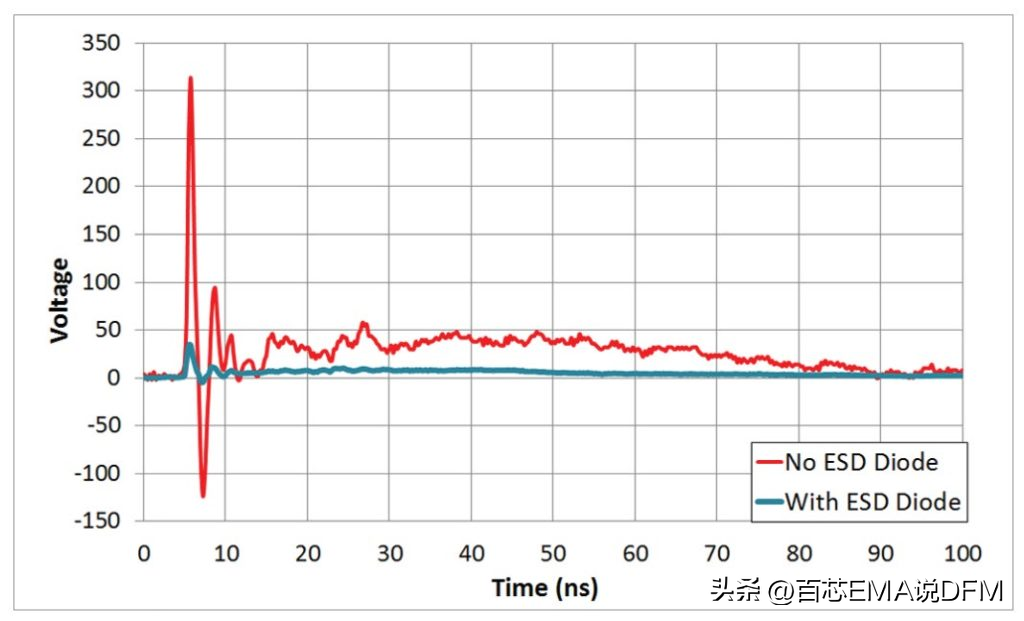

下图这个例子,在ESD事件期间,如果没有外部TVS二极管,IC会在引脚上看到超过300V的电压,很有可能会使内部保护过载并损坏设备。通过添加单个外部TVS二极管,可以减少这种情况发生。

二、5种ESD保护电路+模拟

为了更好地展示ESD事件期间不同保护方案的工作原理,下面对5种不同ESD保护电路的方案进行模拟。

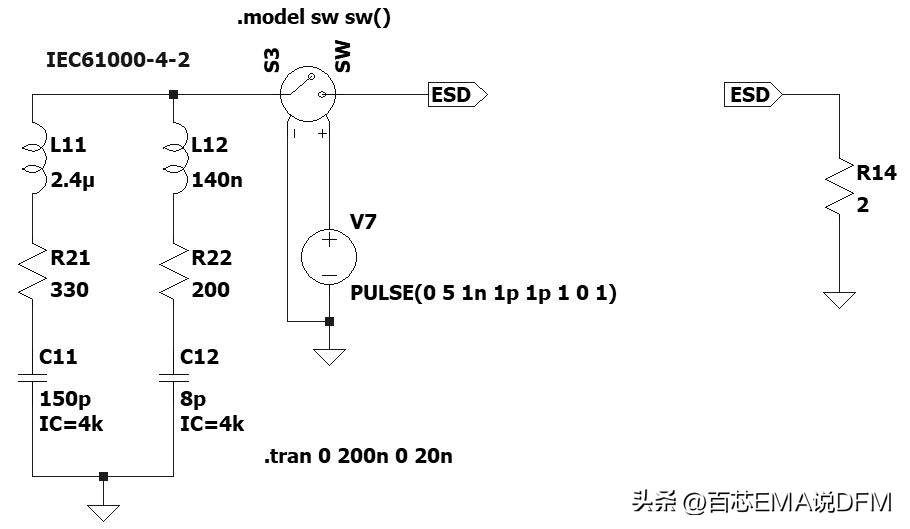

下面为ESD:

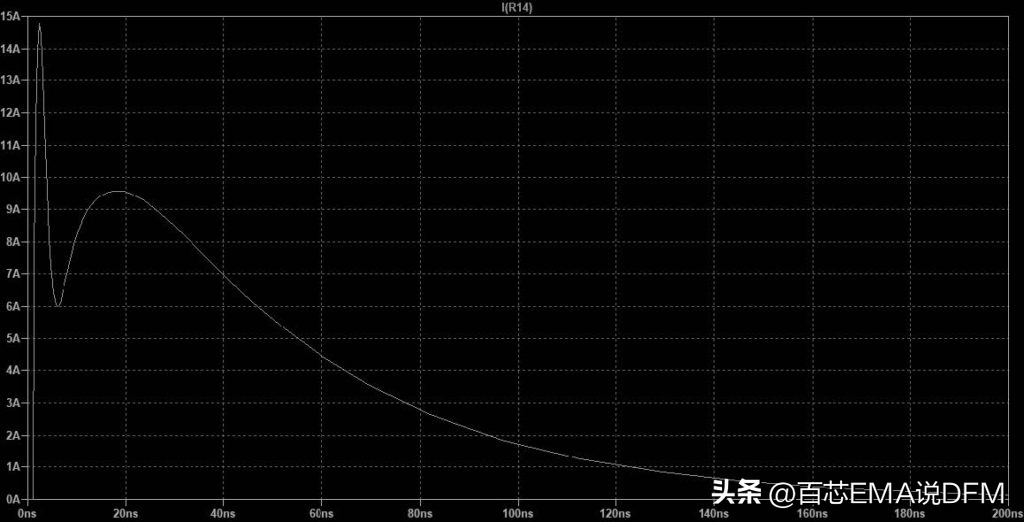

对该电路进行测试,使用2R校准电阻(R14),会生成一下电流/时间图。

使用 2R 校准电阻

了解后,使用此电路测试各种不同的ESD保护电路。

1、无ESD保护电路

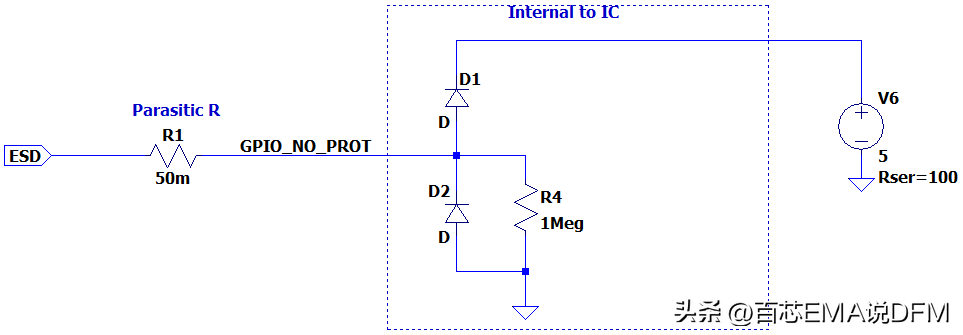

下面这个电路模拟了IC内部的ESD保护电路,ESD应用于暴露的GPIO引脚,具有少量寄生电阻:

无ESD保护电路

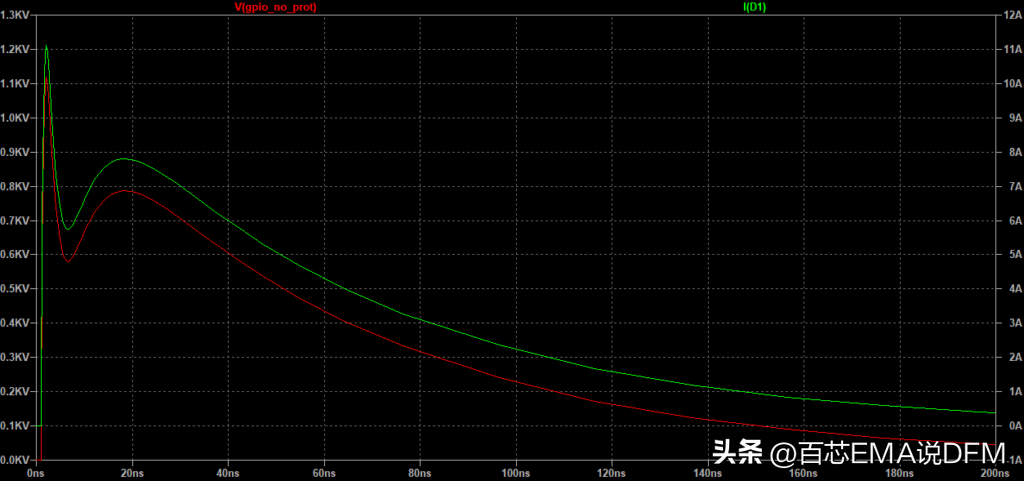

模拟

GPIO引脚电压超过1KV,11A通过D1。根据下图曲线,没有ESD保护会使内部保护二极管暴露在极端的电压和电流下,可能会导致二极管失效。由于通过 D1 的电流与电压 GPIO 直接相关。

无ESD保护电路,GPIO 引脚电压超过 1kV,11A 通过 D1。

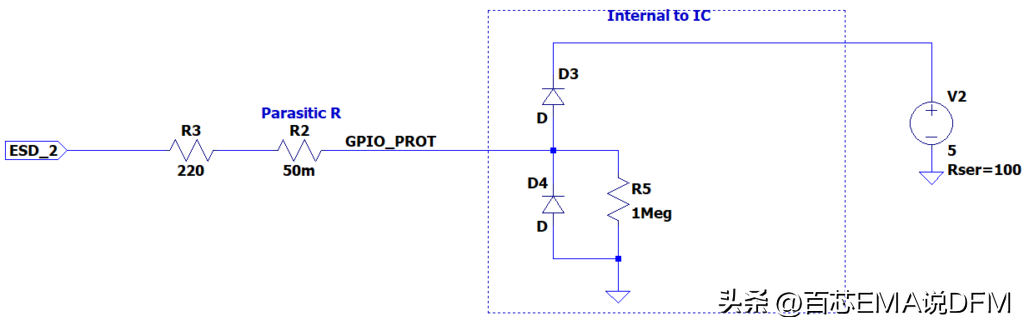

2、串联ESD保护电路

这里的ESD保护电路只是简单地使用一个串联电阻。对于这个模拟,使用220R,串联电阻用于减缓信号的上升时间,并且可以大大改善电路的EMC和SI。

ESD保护电路使用一个串联电阻

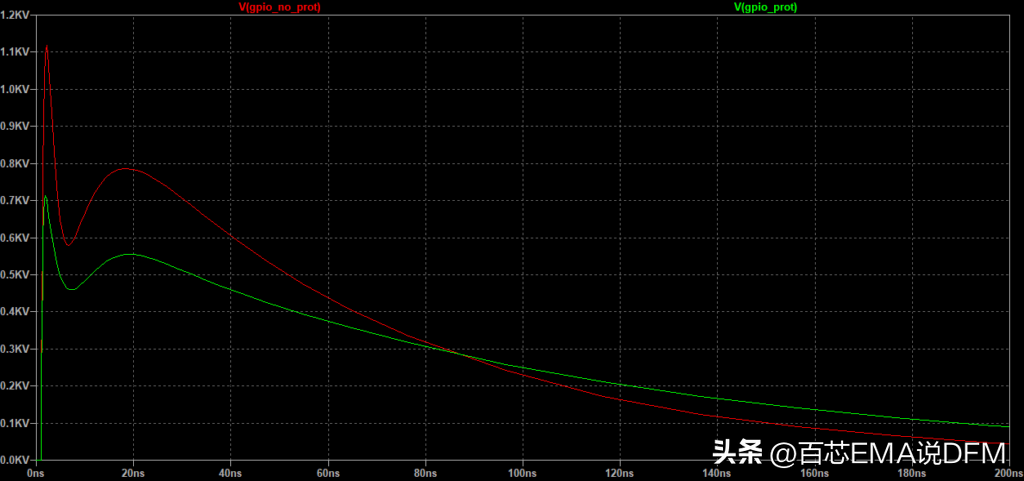

模拟

如下图所示,最大GPIO电压降低了近50%,通过D10的电流降低了40%。虽然说依旧会损坏IC,但确实也显示了单个电阻可以增加ESD保护产生的影响,如果IO引脚上的信号允许,可以使用更大的电阻提供额外保护。

与无 ESD 保护相比,串联电阻的曲线图显示出显着改善。

3、电容

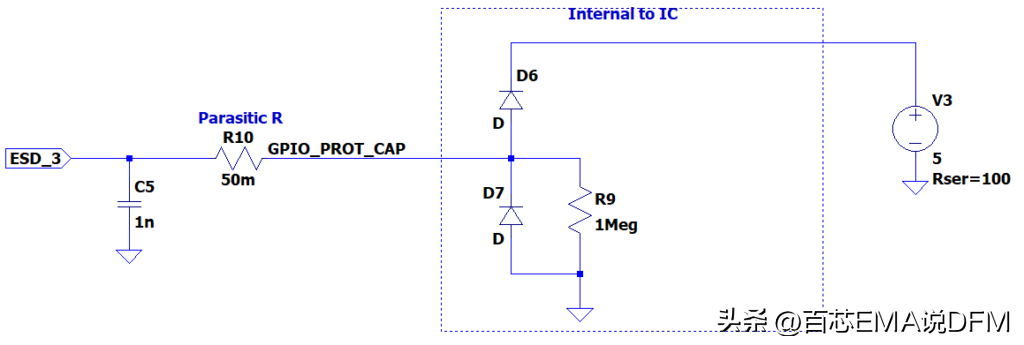

另一种简单的ESD保护电路在引脚到地之间简单地加一个1nF电容。与串联电阻类似,电容的大小取决于线路的用途。

在 GPIO 线与地之间添加了一个 1nF 电容

模拟

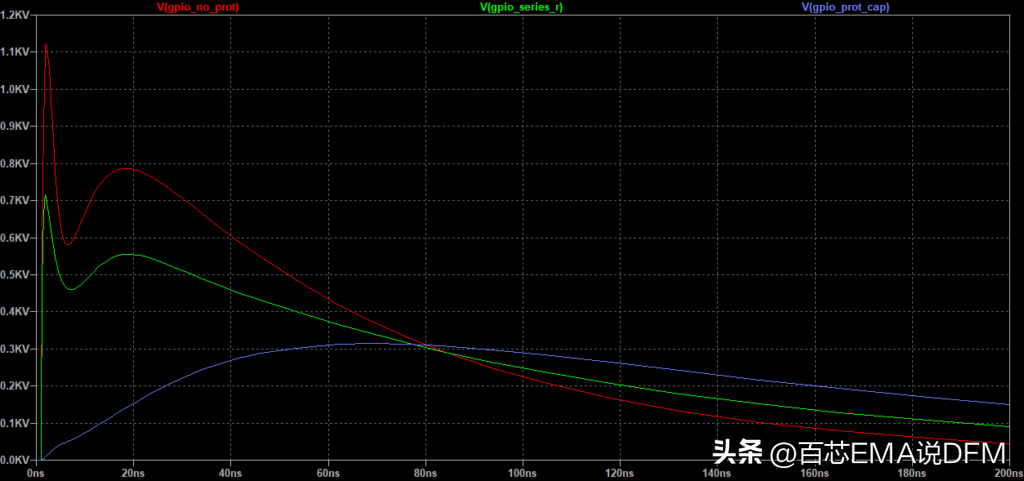

如下图所示,单个1nF小电容使曲线图发生巨大变化。峰值电压小于330V,电流限制在3A左右。

这个ESD保护电路潜在的问题是事件比现在要长的多,可能使内部保护二极管过热,并且可能破坏线路上的任何数据。

这个图与前面2个完全不一样,电容显著减慢了事件的上升时间

将电容换成10nF,进一步降低了峰值电压,但是事件发生的事件也被延长了。

一个 10nF 的电容进一步降低了峰值电压

串联电阻也是这样,电容越大,提供的保护越多,但是有个例外,具有低ESR的大陶瓷电容会导致振铃。因此,通常需要将串联电阻与电容结合使用,至少用其串联的电阻来阻尼电容。另外,不可以将这种方法用于任何通信或者高速信号,因为电容会使总线负载过大。

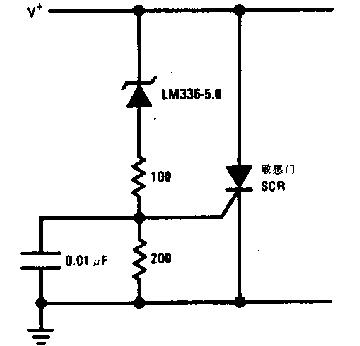

4、TVS二极管

接下来是TVS二极管,是ESD保护电路最常用的方法之一,作用与齐纳二极管基本相同,传导速度更快,浪涌额定值更高(有时候也没有指定的连续电路/额定功率)。

有一些重要的定义/规范:

-

反向工作最大电压 (VRWM):正常工作条件下应施加的最大反向电压。

-

击穿电压 (VBR):二极管刚开始导通时的电压。

-

钳位电压 (VCLAMP):系统在浪涌期间将经历的最大电压。

-

动态电阻 (RDYN):二极管完全导通时的估计电阻。

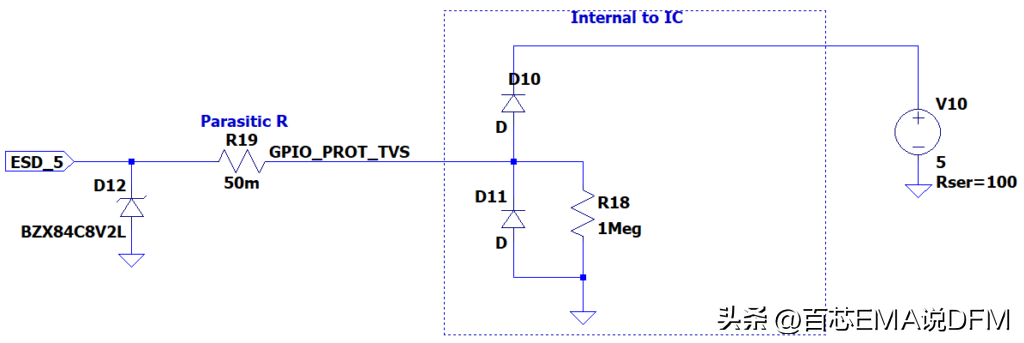

这里要注意单向二极管和双向二极管是不一样的。在GPIO上使用 8.2V 齐纳 (TVS) 二极管接地。

在GPIO上使用 8.2V 齐纳 (TVS) 二极管接地。

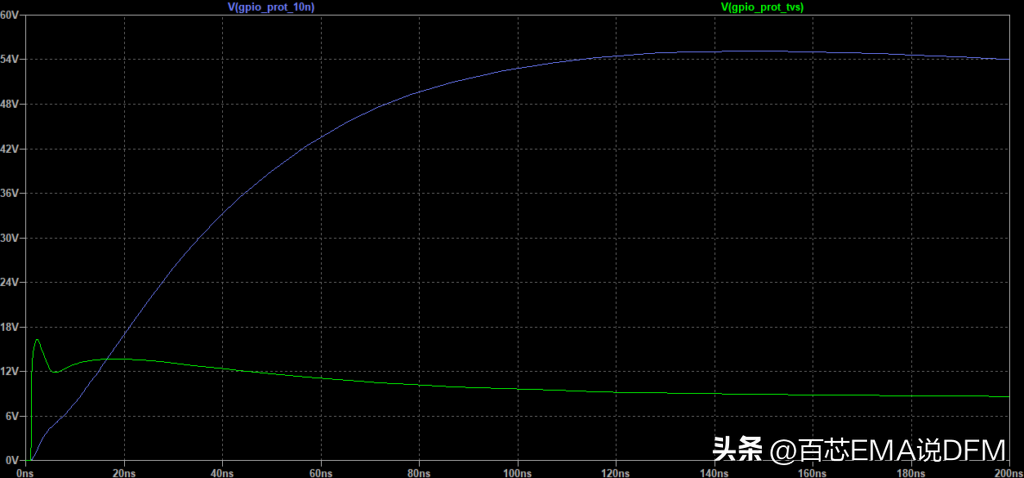

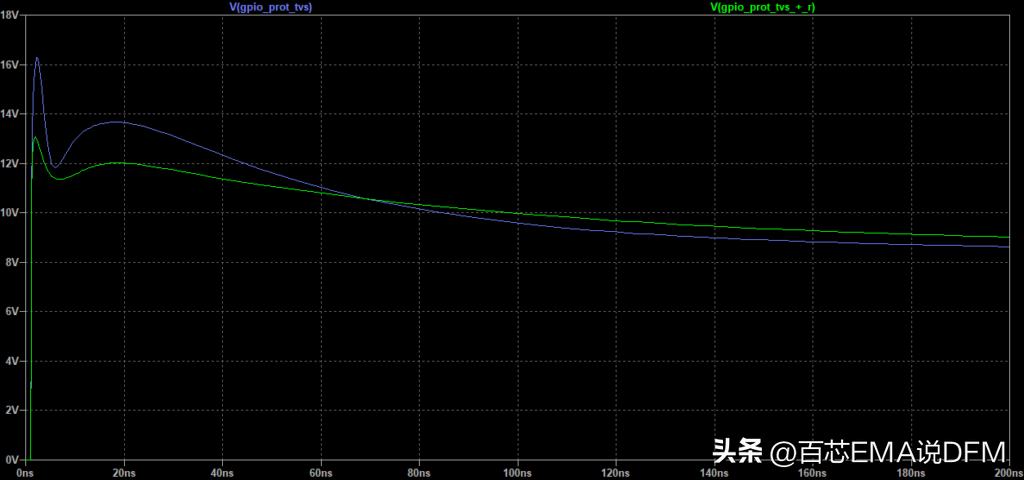

模拟

可以看到GPIO 引脚上的电压大幅下降。最大现在约为16V,通过D10的电流仅为100mA。内部保护二极管可以这样使用。

GPIO 引脚上的电压大幅下降

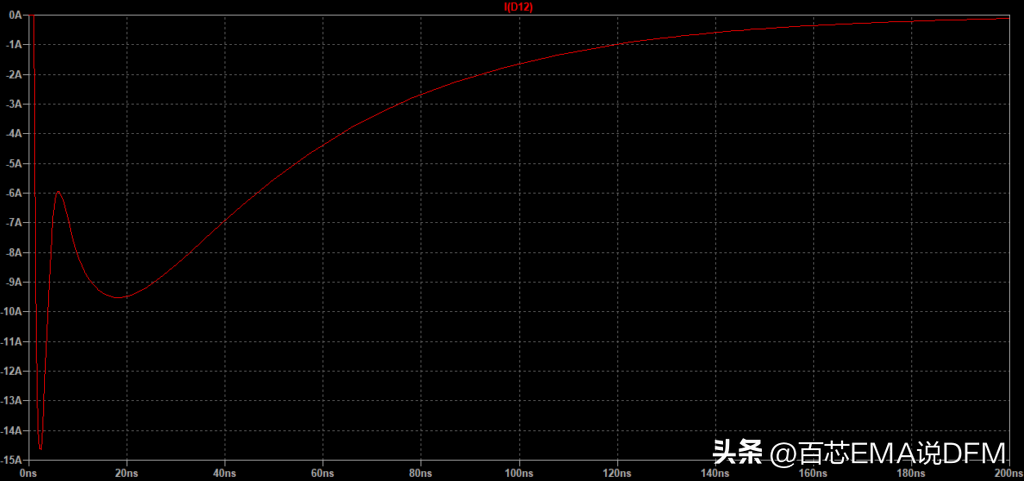

这里必须要知道的是外部TVS二极管D12承受的压力,如下图所示:

显示了 TVS 二极管 D12 在 ESD 事件期间承受的电流

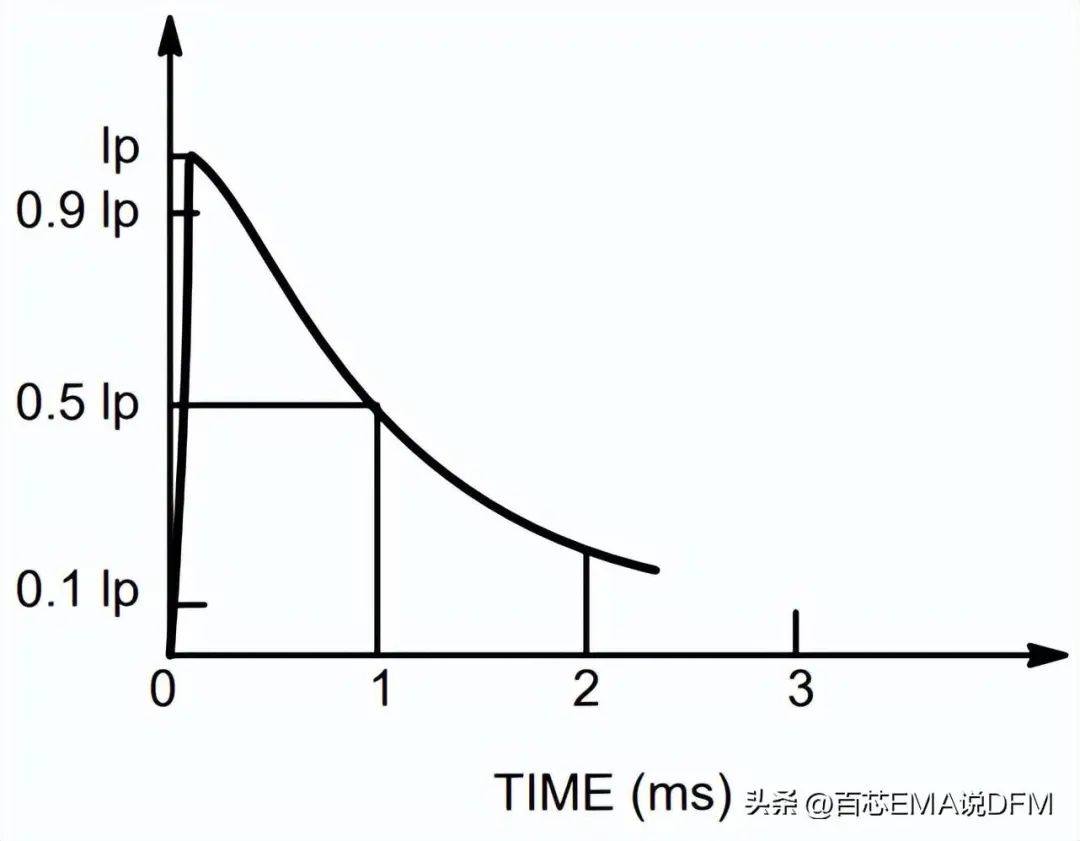

TVS的电流等级

当使用 TVS 二极管时,Datasheet上会有“电流 – 峰值脉冲 (10/1000µs)”的规格。这是 TVS 二极管在指定时间和波形下可以处理的最大额定电流。

TVS的电流等级

10/1000µs 是衡量 TVS 二极管功率处理性能的常用规格。

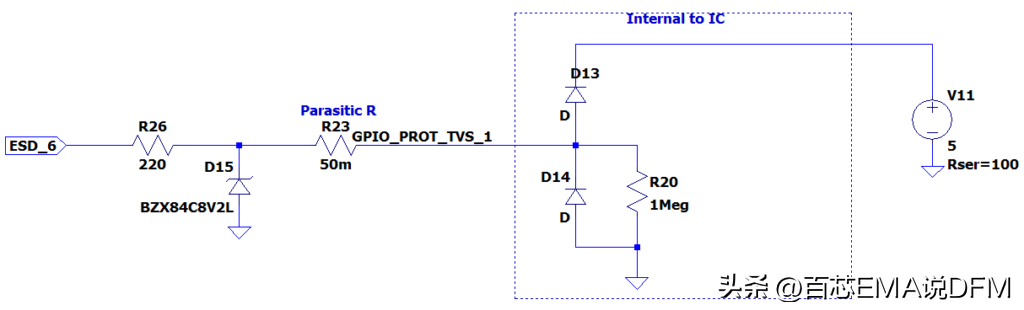

降低电流并保护TVS二级管的一种简单方法是在TVS的连接器侧使用串联电阻。在在 TVS 二极管的 ESD 侧放置了一个 220R 电阻。

在 TVS 二极管的 ESD 侧放置了一个 220R 电阻

在 TVS 二极管的 ESD 侧放置了一个 220R 电阻。

模拟

下图显示通过 TVS 二极管的电流减少了近 50%。当峰值电流/电压降低时,事件的长度增加。

通过 TVS 二极管的电流减少了近 50%

电阻还会影响 GPIO 引脚上的峰值电压。如下图所示:TVS 二极管 + 串联电阻的曲线图显示 GPIO 引脚上的峰值电压略有下降。

TVS 二极管 + 串联电阻的曲线图显示 GPIO 引脚上的峰值电压略有下降

TVS 二极管 + 串联电阻的曲线图显示 GPIO 引脚上的峰值电压略有下降。

5、双肖特基二极管

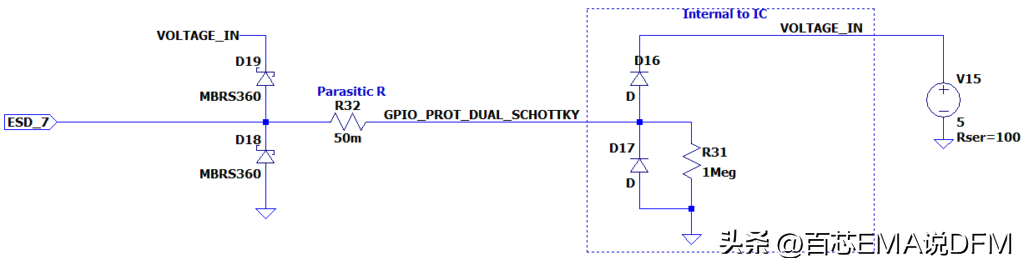

我偶尔会使用到的一个ESD保护电路是双肖特基二极管,将一个偏置到地,另一个偏置到输入电压轨。与TVS方法不同的地方在于,在正电压尖峰期间,功率会转储到正轨,而不是接地。这意味着必须有一个低阻抗的配电网络。如下图:

两个肖特基二极管 D18 和 D19,分别偏置到地和正电压轨。

两个肖特基二极管 D18 和 D19,分别偏置到地和正电压轨

两个肖特基二极管 D18 和 D19,分别偏置到地和正电压轨。

模拟

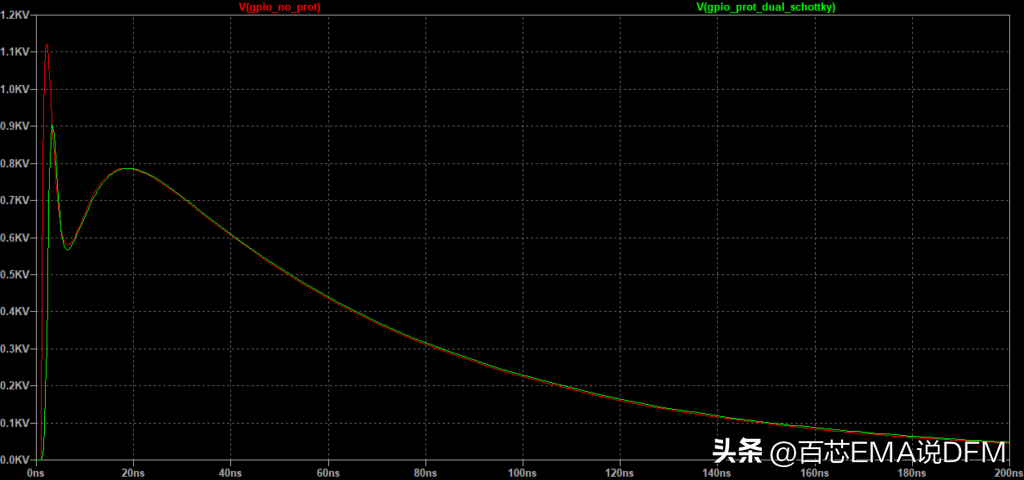

V15(电源)仍然具有相当大的 100R 串联电阻。这意味着在正 ESD 事件中,浪涌基本上通过 D19,然后是 100R 电阻,然后通过接地完成电路。如下图所示,这并不是一个很好的保护方案。

用 100R 电源时,双 TVS 二极管基本上不提供保护

这里需要注意的另一个问题是肖特基的反向额定电压,如果超过就会损坏二极管。电压电源的阻抗更改为 1R,即可使双肖特基方法比 TVS 更有效。

电压电源的阻抗更改为 1R,可使双肖特基方法比 TVS 更有效。

考虑到大多数电源的阻抗远低于 1R,这种方案可能非常有效。如果使用这种方法,就必须要考虑到你的配电网络。

三、使用什么ESD保护电路

这里主要是3个:

此类的信号比较容易设计保护,因为对于每个信号在降级发生之前可以具有的最大总线电容有非常详细的规范。

通常我会使用专为信号类型设计的TVS二极管,然后看串联是不是能接受,一般取值会大一点。

2、慢速接口,一般保护

这些是离开PCB的通用引脚,一般用于LED或者开关或者触摸板。这里的关键是不会受到恶劣环境的影响。

对于这些,通常会使用TVS+大串联电阻,根据应用,可能会使用双肖特基方法,因为用这个还可以提供过流和短路保护。

3、慢接口,高防护

与上面的非常相似,除了针对工业应用,或者故障是不可接受的情况,这样的话,会在信号中添加一个额外电容,从而显著降低转换率。

本文来源百芯EMA说DFM 在此特别鸣谢!

-

ESD

+关注

关注

50文章

2377浏览量

178873 -

保护电路

+关注

关注

46文章

942浏览量

103383 -

电路设计

+关注

关注

6732文章

2576浏览量

217996 -

模拟技术

+关注

关注

17文章

471浏览量

40680 -

张飞电子

+关注

关注

56文章

176浏览量

13521

原文标题:5种ESD保护电路设计(电路图+仿真模拟)

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

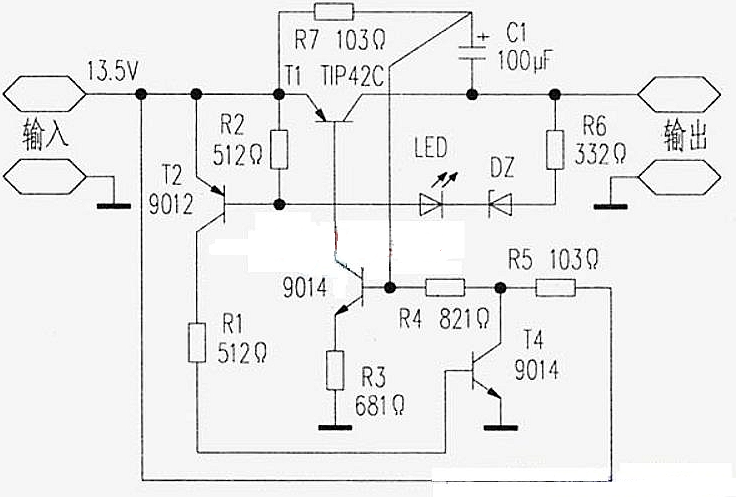

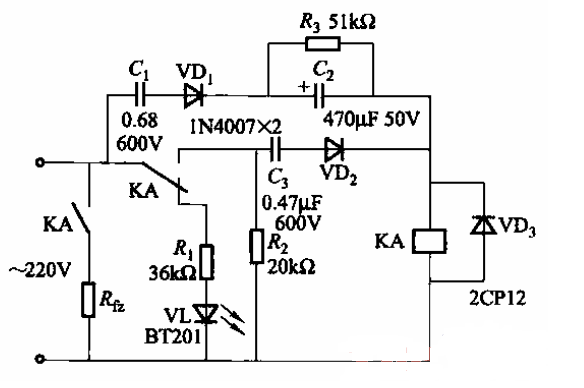

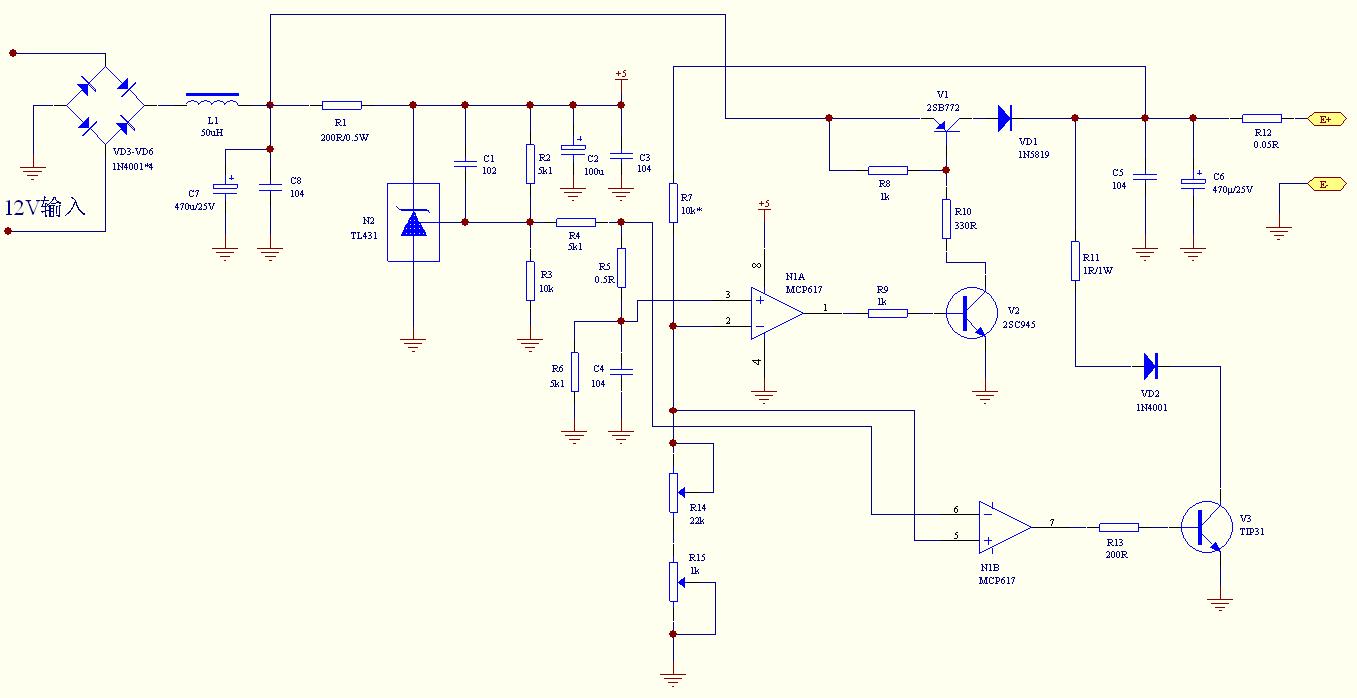

36v欠压保护电路图大全(六款模拟电路设计原理图详解)

求助,关于LM386芯片内ESD保护电路设计和引脚分配情况求解

ESD保护电路的设计pdf

电路图及电路设计资料分享

12v过压保护简单电路图大全(四款模拟电路设计原理图详解)

过流保护自恢复电路图大全(六款模拟电路设计原理图详解)

最简单的短路保护电路图汇总(六款模拟电路设计原理图详解)

5种ESD保护电路设计(电路图+仿真模拟)

5种ESD保护电路设计(电路图+仿真模拟)

评论