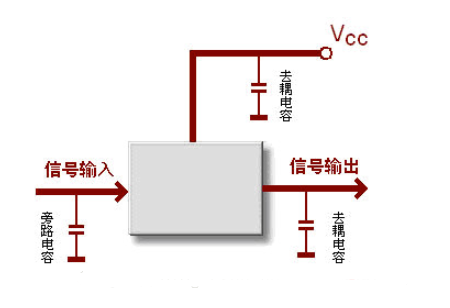

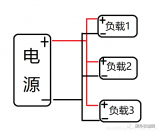

去耦电容在补偿集成片或电路板工作电压跌落时能起到储能作用。它可以分成整体的、局部的和板间的三种。整体去耦电容又称旁路电容,它工作于低频(《1MHz)范围状态,为整个电路板提供一个电流源,补偿电路板工作时产生的ΔI噪声电流,保证工作电源电压的稳定。它的大小为PCB上所有负载电容和的50~100倍。它应放置在紧靠PCB外接电源线和地线的地方,印制线密度很高的地方。这不仅不会减小低频去耦,而且还会为PCB上布置关键性的印制线提供空间。

局部去耦电容有两个作用。第一,出于功能上的考虑:通过电容的充放电使集成片得到的供电电压比较平稳,不会由于电压的暂时跌落导致集成片功能受到影响;第二,出于EMC考虑:为集成片的瞬变电流提供就近的高频通道,使电流不至于通过环路面积较大的供电线路,从而大大减小向外的辐射噪声。同时由于各集成片拥有自己的高频通道,相互之间没有公共阻抗,抑止了其阻抗耦合。局部去耦电容安装在每个集成片的电源端子和接地端子之间,并尽量靠近集成片。

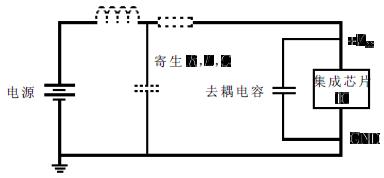

板间去耦电容是指电源面和接地面之间的电容,它是高频率时去耦电流的主要来源。板间电容可以通过增加电源层和接地层间面积来增大。在PCB中,一些接地面可以布到了电源层,移去这些接地面,用电源隔离区代之,可以增加板间电容。

二、PCB板中去耦电容的大小

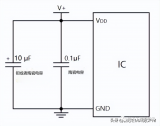

在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法,好的高频去耦电容可以去除高到1GHz的高频成分。陶瓷片电容或多层陶瓷电容的高频特性较好。设计印制线路板时,每个集成电路的电源、地之间都要加一个去耦电容。去耦电容有两个作用:一方面是本集成电路的蓄能电容,提供和吸收该集成电路开门关门瞬间的充放电能;另一方面旁路掉该器件的高频噪声。去耦电容的配置原则如下:

1、电源分配滤波电容

电源输入端跨接一个10μF~100μF的电解电容器,如果印制电路板的位置允许,采用以上的电解电容器的抗干扰效果会更好。1μF,10μF电容,并行共振频率在20MHz以上,去除高频率噪声的效果要好一些。在电源进入印制板的地方和一个1μF或10μF的去高频电容往往是有利的,即使是用电池供电的系统也需要这种电容。

2、芯片配置去耦电容

为每个集成电路芯片配置一个0.01μF的陶瓷电容器。数字电路中典型的去耦电容为0.1/μF的去耦电容有5nH分布电感,它的并行共振频率在7MHz左右,也就是说对于10MHz以下的噪声有较好的去耦作用,对40MHz以上的噪声几乎不起作用。如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1μF~10μF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1μF~10μF而且漏电流很小(0.5μA以下)。去耦电容值的选取并不严格,可按C=1/f计算,即10MHz取0.1μF。对微控制器构成的系统,取0.1μF~0.01μF之间都可以。

3、必要时加蓄放电容

每10片左右的集成电路要加一片充放电电容,或称为蓄放电容,电容大小可选10μF。通常使用的大电容为电解电容,但是在滤波频率比较高时,最好不用电解电容,电解电容是两层薄膜卷起来的,这种卷起来的结构在高频时表现为电感,最好使用钽电容或聚碳酸酯电容。

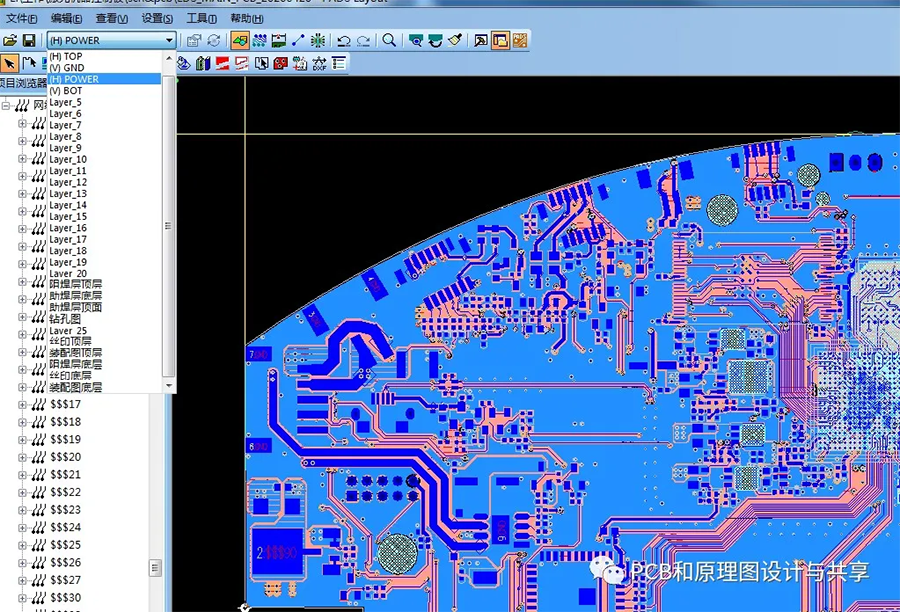

三、PCB板中合理布置去耦电容

(一)电容的等效模型在用电容抑制电磁骚扰和滤波的时候,最容易忽视的问题就是电容引线对滤波效果的影响。电容器的容抗与频率成反比,正是利用这一特性,将电容并联在信号线与地线之间起到对高频噪声的旁路作用。然而,在实际工程中,很多人发现这种方法并不能起到预期滤除噪声的效果,面对顽固的电磁噪声束手无策。出现这种情况的一个原因是忽略了电容引线对旁路效果的影响。

实际电容器是由等效电感(ESL)、电容和等效电阻(ESR)构成的串联网络。

理想电容的阻抗是随着频率的升高降低,而实际电容的阻抗是图6-7所示网络的阻抗特性,在频率较低的时候,呈现电容特性,即阻抗随频率的增加而降低,在某一点发生谐振,在这点电容的阻抗等于等效串联电阻ESR。在谐振点以上,由于ESL的作用,电容阻抗随着频率的升高而增加,这使电容呈现电感的阻抗特性。在谐振点以上,由于电容的阻抗增加,因此对高频噪声的旁路作用减弱,甚至消失。所以在布置去耦电容的时候一定要注意电容的分布参数对滤波的影响。

(二)电容引线的作用

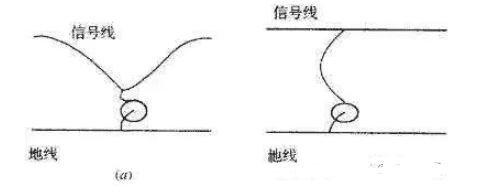

电容的谐振频率由ESL和C共同决定,电容值或电感值越大,则谐振频率越低,也就是电容的高频滤波效果越差。ESL除了与电容器的种类有关外,电容的引线长度是一个十分重要的参数,引线越长,则电感越大,电容的谐振频率越低。因此在实际工程中,要使电容器的引线尽量短,电容器的正确安装方法和不正确安装方法如图1所示:

图1:滤波电容的安装方法

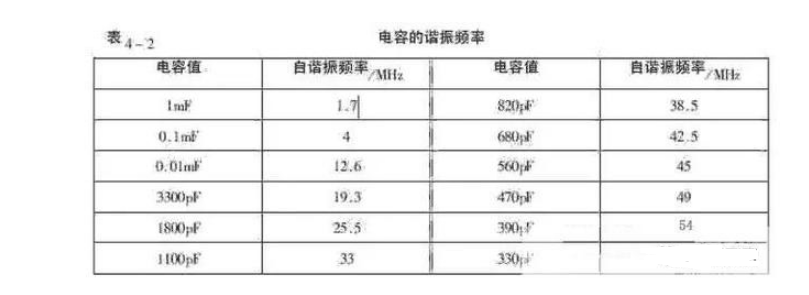

根据LC电路串联谐振的原理,谐振点不仅与电感有关,还与电容值有关,电容越大,谐振点越低。许多人认为电容器的容值越大,滤波效果越好,这是一种误解。电容越大对低频干扰的旁路效果虽然好,但是由于电容在较低的频率发生了谐振,阻抗开始随频率的升高而增加,因此对高频噪声的旁路效果变差,所以在滤波的时候要选取合适的电容。表4-2是不同容量瓷片电容器的自谐振频率,电容的引线长度是1.6mm。

尽管从滤除高频噪声的角度看,电容的谐振是不希望的,但是电容的谐振并不是总是有害的。当要滤除的噪声频率确定时,可以通过调整电容的容量,使谐振点刚好落在骚扰频率上。

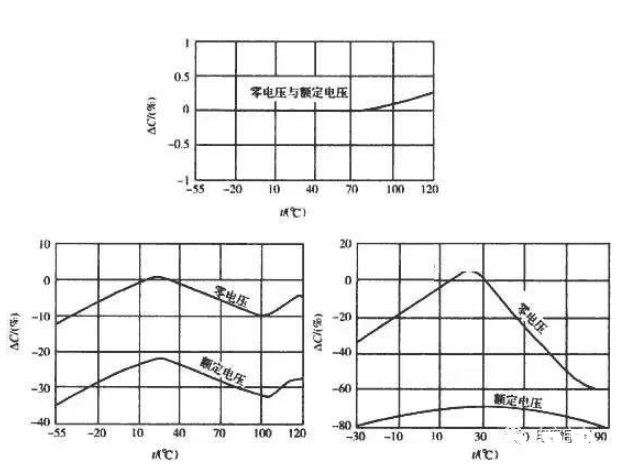

(三)温度对电容的影响

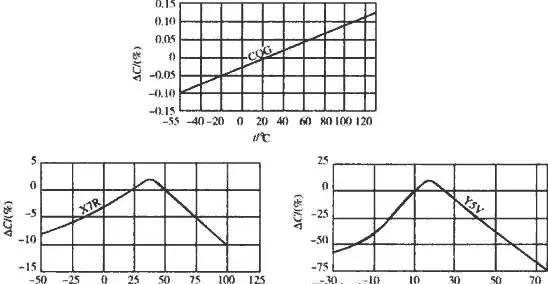

温度对电容的特性也有很大的影响,由于电容器中的介质参数受到温度变化的影响,因此电容器的电容值也随着温度变化。不同的介质随着温度变化的规律不同,有些电容器的容量当温度升高时会减小70%以上。常用的滤波电容为瓷介质电容。瓷介质电容器有超稳定型(如COG或NPO)、稳定型(如X7R)以及通用型(如Y5V或Z5U)三种。不同介质的电容器的温度特性如图2所示:

图2:不同介质电容器的温度特性

从图2中可以看到,C0G电容器的容量几乎随温度没有变化,X7R电容器的容量在额定工作温度范围变化12%以下,YSV电容器的容量在额定工作温度范围内变化70%以上。这些特性是必须注意的,否则会出现滤波器在高温或低温时性能变化而导致设备产生电磁兼容问题。

C0G介质电容虽然受温度影响很小,特性稳定,但其介电常数较低,一般在10~100,因此当体积较小时,容量较小。XTR介质电容的介电常数高得多,为2000~4000,因此较小的体积能产生较大的电容。YSV介质电容的介电常数最高,为5000~25000。通常是用在要求较小的体积,较大的容值的地方。

许多人在选用电容器时,片面追求电容器的体积小,这种电容器的介质虽然具有较高的介质常数,但温度稳定性很差,这会导致设备的温度特性变差。这在选用电容器时要特别注意,尤其是在军用设备中。

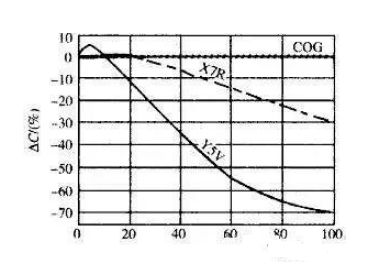

(四)PCB板中电压对电容的影响

电容器的电容量不仅随着温度变化,还会随着工作电压变化,这一点在实际工程必须注意。X7R电容器在额定电压状态下,其容量降为原始值的70%而YSV电容器的容量降为原始值的30%了解了这个特性,在选用电容时要在电压或电容量上留出余量,否则在额定工作电压状态下,滤波器会达不到预期的效果。

图3:电容器的电压特性

综合考虑温度和电压的影响时,电容的变化如图3所示。

所以在滤波电容放置时一定要全面考虑电容的滤波效果,而不是越多越好,越大越好。排除盲目使用电容的误区,也排除不使用的观点。

图4:电容器的温度/压特性

四、PCB板去耦电容合理配置

(1)合理布置电源滤波/退耦电容:一般在原理图中仅画出若干电源滤波/退耦电容,但未指出它们各自应接于何处。其实这些电容是为开关器件(门电路)或其他需要滤波/退耦的件而设置的,布置这些电容就应尽量靠近这些元部件,离得太远就没有作用了。当电源滤波/退耦电容布置的合理时,接地点的问题就显得不那么明显。

(2)对于噪声能力弱、关断时电流变化大的器件和ROM ,RAM等存储型器件,应在芯片的电源线(VCC)和地线(GND)间直接接入去耦电容。

(3)去耦电容的引线不能过长,引线越短,去耦效果越好。特别是高频旁路电容不能带引线。

(4)去耦不是越多越好,而是要注意滤波的效果,根据电路板和器件的时间情况来选用电容的个数和大小。

(5)去耦电容在要求较高的时候不用瓷片电容和电解电容,以为它们的容值精度差,分布电感大。要选用比较精确的钽电容或者聚酯电容等。

(6)在芯片较多、去耦电容比较多地方,可以安装一个充放电电容,来电荷的泻放电路开关工作过程中产生的积累。

-

电容

+关注

关注

100文章

6437浏览量

158033 -

去耦电容

+关注

关注

12文章

325浏览量

23477 -

PCB

+关注

关注

1文章

2265浏览量

13204

发布评论请先 登录

PCB设计吐槽有理/礼,老司机带你成长带你飞

去耦电容和旁路电容的电容值选择方法

PCB板去耦电容的大小选择与布置

PCB板去耦电容的大小选择与布置

评论