出于各种原因,电子系统需要实施隔离。它的作用是保护人员和设备不受高电压的影响,或者仅仅是消除PCB上不需要的接地回路。在各种各样的应用中,包括工厂和工业自动化、医疗设备、通信和消费类产品,它都是一个基本设计元素。

虽然隔离至关重要,但它的设计也极其复杂。控制功率和数据信号通过隔离栅时,会产生电磁干扰(EMI)。这些辐射发射(RE)会对其他电子系统和网络的性能产生负面影响。

对于带隔离的电路设计,一个重要的步骤是跨隔离栅传输功率,并缓解产生的RE。虽然传统方法可能行之有效,但它们往往需要权衡取舍。其中可能包括使用分立式电路和变压器来传输功率。这种方法笨重耗时,会占用宝贵的PCB空间,无一不会增加成本。更经济高效的解决方案是将变压器和所需的电路集成到更小外形中,如芯片封装。

虽然这样可以节省电路板空间,降低设计的复杂性和成本,但也使得变压器体积变小,具备的绕组更少,需要更高的开关频率(高达200MHz)才能高效地将所需的功率传输到次级端。在更高频率下,寄生共模(CM)电流可能通过变压器的绕组以容性方式从初级端耦合至次级端。因隔离栅的性质所限,没有物理路径可以让这些CM电流返回初级端。隔离栅形成一个偶极,将能量以CM电流的形式辐射,并让其返回到初级端。这就引发了另一个重要考虑因素:合规性。

产品上市前,必须符合EMC规定。将变压器和所需的电路集成到更小的封装中会产生EMI,因此需要采用复杂且成本高昂的RE抑制技术,以满足电磁兼容性(EMC)法规的要求。

EMC是指电子系统在其目标环境中正常工作而不干扰其他系统的能力。全球不同地区都有EMC法规,用于确保所有产品在有其他产品存在的情况下都能正常工作。辐射发射量必须低于目标使用环境和应用场合所对应的规定水平。因此,EMC测试和认证已成为产品上市过程的一个重要组成部分。在欧盟销售的产品需要具有CE标志,而在美国销售的产品则需要获得FCC分类认证。为取得这些认证,需要对系统执行一套EMC测试。在工业、医疗、通信和消费环境中,辐射发射通常必须符合CISPR 11/EN 55011、CISPR 22/EN 55022或FCC Part 15标准。

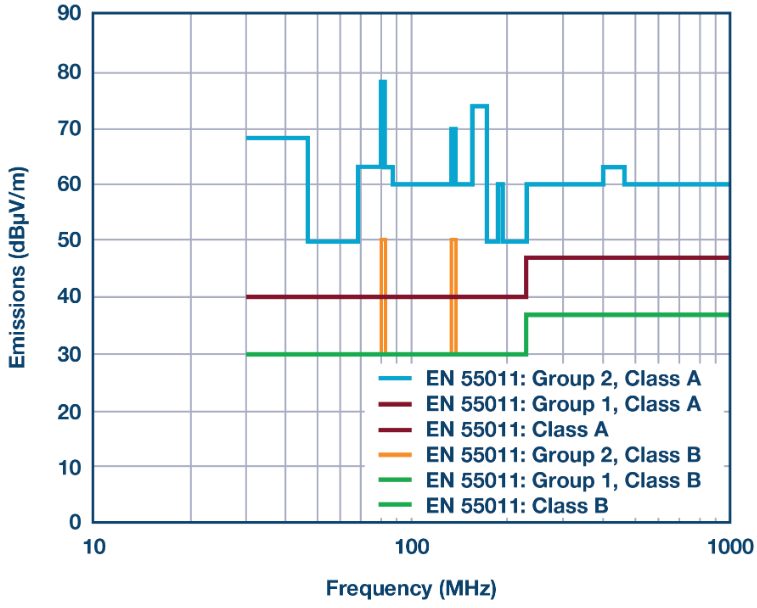

CISPR 11/EN 55011

此标准适用于为工业、科学和医疗(ISM)目的而设计的产生射频能量的设备。在标准范围内,设备可能分为两组。第2组包含有意生成并在局部使用射频能量的所有ISM RF设备。第1组包含此标准范围内不属于第2组的所有设备。

CISPR 22/EN 55022

此标准适用于满足下述条件的信息技术设备(ITE):主要功能是将输入、存储、显示、检索、传输、处理、交换或控制数据和电信信息结合起来,可能配备一个或多个终端端口,通常用于传输信息。

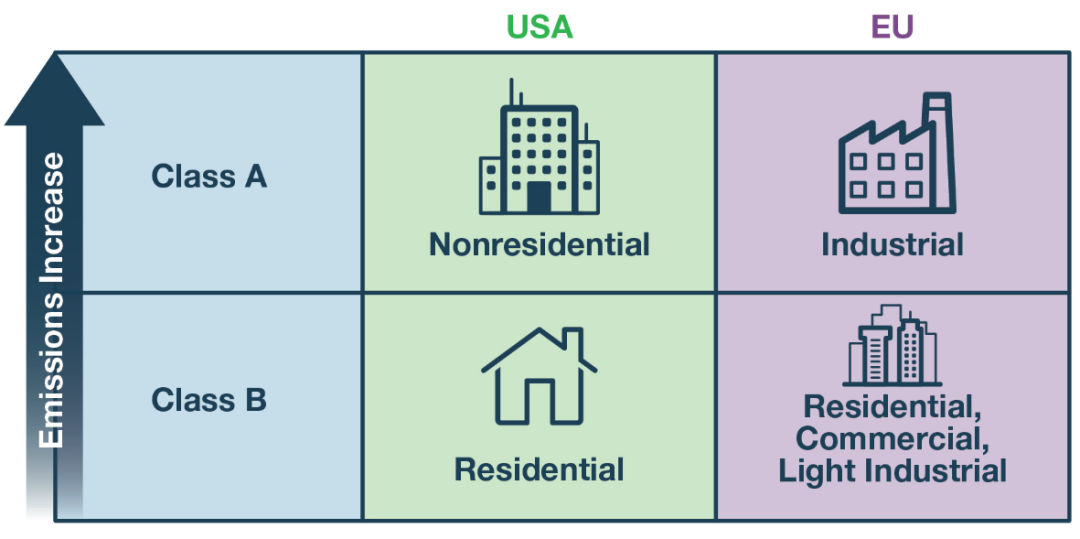

在各个标准下,设备被进一步分类,每个类别需遵循一组单独的排放限制。

A类:用在工业应用和非住宅区的设备

B类:用在住宅环境中的设备

由于B类限制覆盖的是住宅(或轻工业)环境,而这种环境中的产品更有可能彼此非常接近(广播和电视接收器的10米范围内),因此更加严格(比A类低10 dB之多),以免引起干扰问题。

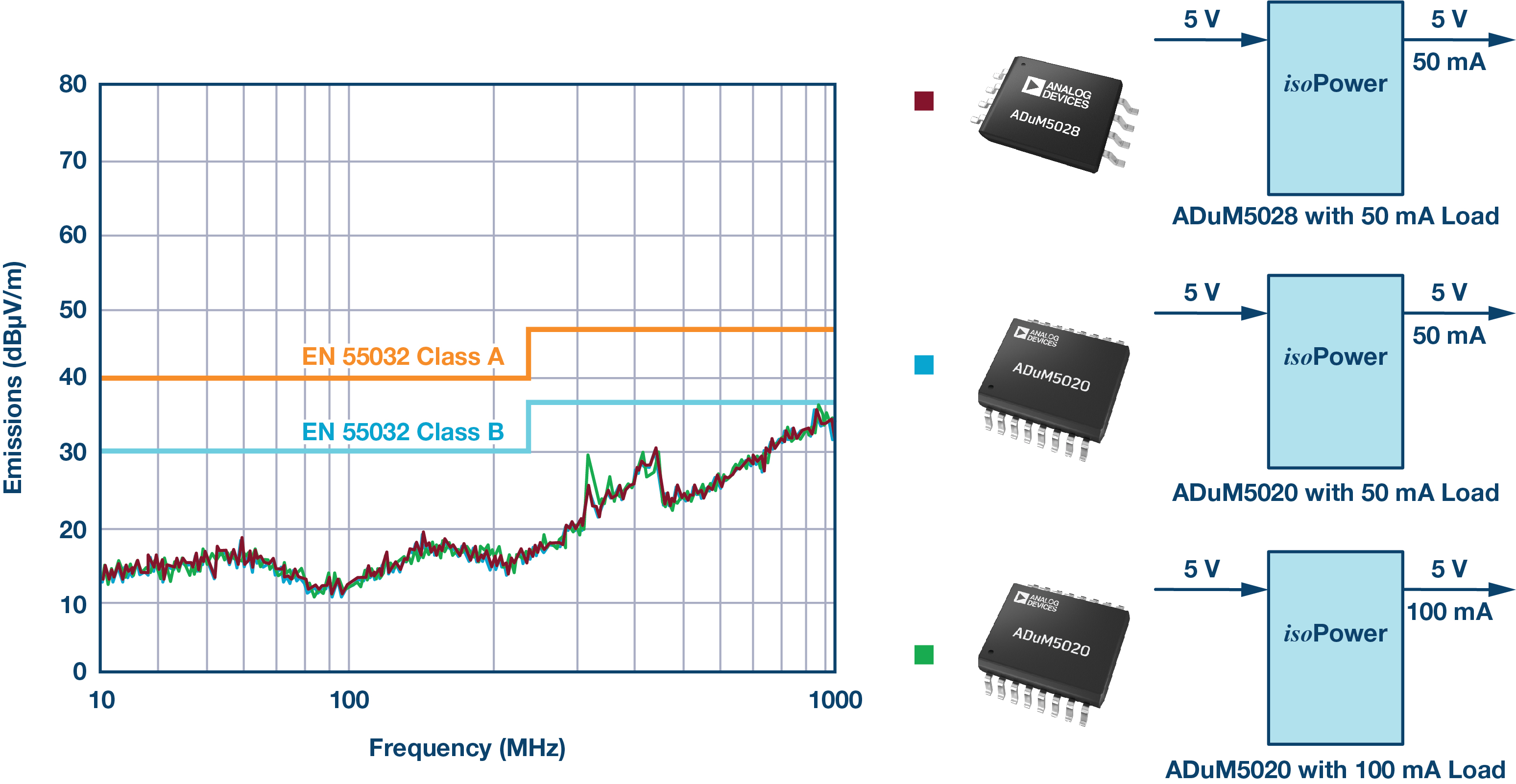

图2显示了与CISPR 11/EN 55011和CISPR 22/EN 55022相关的A类和B类限制线。在这个频率范围内,符合CISPR 22/EN 55022 B类标准意味着也符合CISPR 11/EN 55011 B类标准。

图2. 辐射发射标准—限制线。

在设计周期一开始就考虑EMC

据报道,50%的产品首次EMC测试都以失败告终。1这可能是因为缺乏相关知识,且未能在产品设计阶段的早期应用EMC设计技术。如果在功能设计完成之前一直忽略EMC问题,通常会带来耗费时间且代价高昂的挑战。此外,随着产品开发过程的不断深入,能够用来解决EMC问题的技术也越来越少,因为产品方面的更改必将导致计划超时和成本增加。

想要较大限度地缩短设计时间和降低项目成本,在项目开始时就进行EMC设计是至关重要的。组件的选择和放置也很重要。将已经符合行业标准的器件纳入选择和设计可以提高合规性。

EMI抑制技术:亟需更好的方法

与使用分立式变压器的传统方法相比,将变压器和电路集成到芯片级封装中可减少组件数量,进而大大节省PCB空间,但可能会引入更高的辐射发射。辐射发射抑制技术会使PCB的设计更加复杂,或需要额外组件,因此可能会抵消集成变压器所节省的成本和空间。

例如,在PCB级别抑制辐射发射的一种常见方法是为CM电流形成一个从次级端至初级端的低阻抗路径,从而降低RE水平。要实现这一点,可以在初级端和次级端之间使用旁路电容。该旁路电容可以是分立式电容,也可以是嵌入式夹层电容。

分立式电容是简单的解决方案,可能是有引线或表面安装组件。它还具有适用于2层PCB的优点,但分立式电容价格昂贵且体积庞大,会占用宝贵的PCB空间,特别是在可能堆叠了多个组件的隔离栅旁。

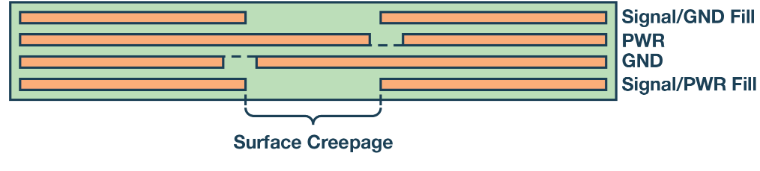

另一个不是很理想的解决方案是使用嵌入式旁路电容,当PCB中的两个面重合时就会形成该电容(图3)。此类电容具有一些非常有用的特性,原因在于平行板电容的电感极低,因此在更大的频率范围内都有效。它可以提高发射性能,但因为需要自定义层厚来获得正确的电容,且PCB需要四层或更多层,所以设计复杂性和成本都会增高。此外,还必须通过隔离的方式,确保内部重叠层的间距满足相关隔离标准所规定的最低距离标准。

旁路电容还允许交流泄漏及瞬变跨隔离栅从一个接地层耦合至另一个接地层。虽然旁路电容一般很小,但高压高速瞬变可通过此电容跨隔离栅注入大量电流。如果应用需承受恶劣的电磁瞬变,如静电放电、电快速瞬变和浪涌,也必须考虑到这一点。

无论是分立式还是嵌入式,使用旁路电容都不是理想的抑制技术。它虽然可以帮助减少辐射发射,却要以增加组件、采用复杂的PCB布局和提高瞬态敏感性为代价。理想的抑制技术不需要采用旁路电容,因此可以降低成本和PCB设计的复杂性。

免去使用复杂抑制技术的必要

理想情况下,集成的隔离电源组件应该包含降低芯片辐射发射的措施,无需在外部额外增加复杂的措施,即可确保通过系统级辐射发射测试。这样一来,只需将组件放置到2层板上,即可通过严格的辐射发射测试,而无需多次制作电路板。

低辐射发射隔离器

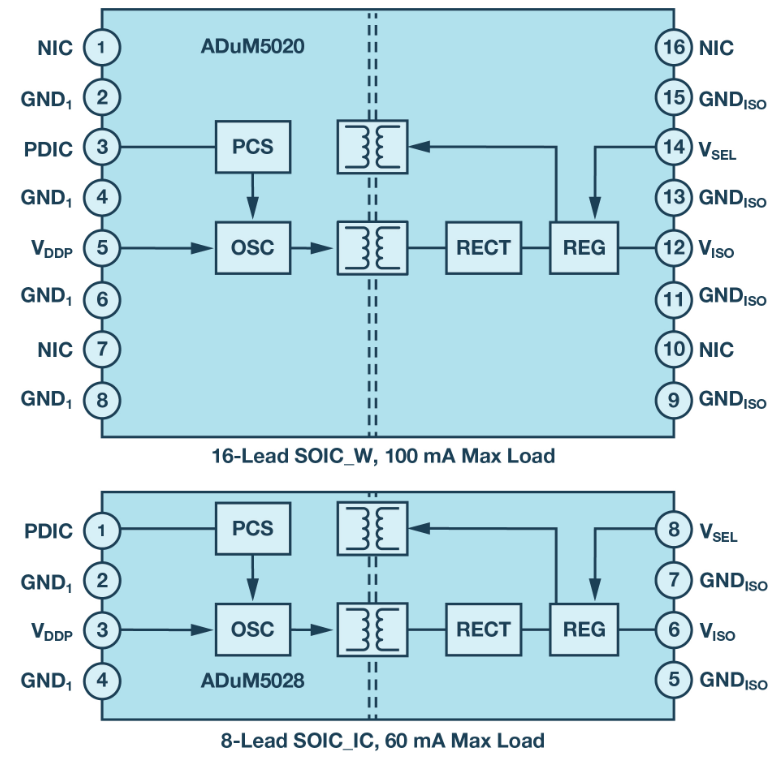

ADI公司的下一代isoPower® 系列产品采用创新的设计技术,可以避免产生大量辐射发射,甚至在没有旁路电容的2层板上也不例外。ADuM5020和ADuM5028在以大幅裕量满足CISPR22/EN55022B类限制的同时,可以分别跨隔离栅提供500 mW和330 mW功率。

图4. ADuM5020和ADuM5028。

ADuM5020采用16引脚宽体SOIC封装,而对于ADuM5028,可以选择的最小封装是8引脚SOIC。ADuM5020/ADuM5028提供3 V和5 V两种电源选项,以及3 kV rms额定隔离。ADuM5020/ADuM5028提供5 kV rms,可以达到与ADuM5020/ADuM5028相同的功率和辐射发射水平。

为了减少辐射发射,ADuM5020/ADuM5028具有出色的线圈对称性和线圈驱动电路,有助于将通过隔离栅的CM电流传输较小化。扩频技术也被用来降低某一特定频率的噪声浓度,并将辐射发射能量扩散到更广泛的频段。在次级端使用低价的铁氧体磁珠会进一步减少辐射发射。在RE合规测试期间,这些技术可以改善峰值和准峰值测量水平。

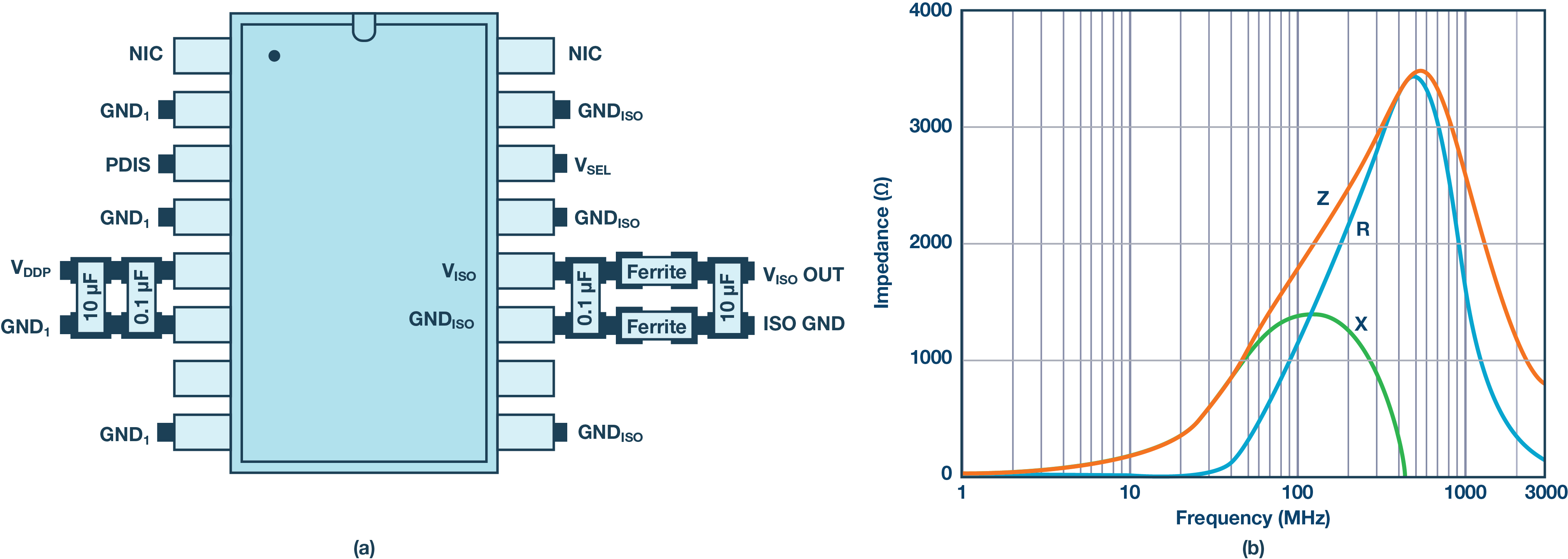

图5. 概念ADuM5020和铁氧体特性曲线。

图5显示了放置在靠近VISO和GNDISO引脚的次级端的铁氧体磁珠。下一段中用于收集辐射发射图的铁氧体是MurataBLM15HD182SN1。这些铁氧体在宽频率范围内具有高阻抗(100MHz时为1800Ω,1GHz时为2700Ω)。这些铁氧体降低了偶极的有效辐射效率。如图6所示,因为铁氧体磁珠的阻抗,CM电流环减小,偶极的有效长度明显缩短,使得偶极效率降低,辐射发射减少。

图6. 使用铁氧体磁珠来减少有效偶极。

ADuM5020/ADuM5028提供即用型直流-直流电源解决方案。这种解决方案的性价比高、复杂性低,占地面积小,且RE性能出色,如果在设计周期开始时就纳入到产品设计中,将有助于满足EMC法规的要求。

来自测试室的结果

ADuM5020/ADuM5028根据CISPR22/EN55022测试指南在10m半波暗室中进行测试。图7所示为一个典型的10m测试室。按照标准规定,ADuM5020/ADuM5028评估PCB被放置在距离天线校准点10m远的非导电工作台上。确保DUT附近没有其他导电表面,因为这会影响测试结果。图8显示了用于确定DUT的高发射频率的峰值扫描。这些点定位后,就可以进行准峰值测量。在准峰值测量期间,工作台会旋转360°,天线高度从1m升高到4m。记录最坏情况的准峰值测量结果,并与限制线要求进行比较。

图7. 10 m测试室的图像和评估PCB

确保没有任何外部设备、金属平面或电缆会干扰DUT的辐射发射测试。为了测试ADuM5020/ADuM5028评估板,使用带板载低压差稳压器的电池来保持较小的电源电流环,并消除不必要的布线。

图8. 峰值图—ADuM5020/ADuM5028。.

图8显示了在不同配置下捕获的ADuM5020/ADuM5028的峰值图。由于在ADuM5020/ADuM5028中采用了扩频技术,注意宽频段范围内的能量扩散情况。图9显示了最坏情况的准峰值测量值与CISPR22/EN55022B类限制线相比的裕量。ADuM5020在输出电源为5V(500mW),负载为100mA的情况下,以超过5dB的裕量通过了CISPR22/EN55022测试。这提供了大幅的设计灵活性。这种裕量幅度很有益,而且推荐达到这种裕量,因为在不同的测试设施中,测试室的质量、校准和设备的精度可能存在差异,可能导致测量结果出现波动。如果最终产品需要在不同的测试室进行测试,且必须符合CISPR 22/EN 55022标准,那么这一点至关重要。

| VIN/VISO 5 V/5 V | VISO 输出电流(mA) | 最坏情况的准峰值频率(MHz) | CISPR 22 B类准峰值dBµV/m B类裕量(dB) |

| ADuM5028 | 50 | 920 | 以–6.3裕量通过 |

| ADuM5020 | 50 | 935 | 以-6.9裕量通过 |

| ADuM5028 | 100 | 915 | 以-5.1裕量通过 |

ADI公司的下一代isor系列产品提供紧凑的即用型电源解决方案,无需为了满足辐射发射限制而采用复杂的PCB级抑制技术。ADuM5020/ADuM5028提供适用于隔离设计的直流-直流即用型电源解决方案,满足以下辐射发射和产品标准要求:

X CISPR 22/EN 55022(B类):信息技术设备

CISPR 11/EN 55011(B类):工业、科学和医疗设备

X IEC 61000-6-4:通用标准—工业环境的辐射发射标准

X IEC 61000-6-3:通用标准—住宅、商业和轻工业环境的辐射发射标准

IEC 61131-2:可编程控制器—第2部分:设备要求和测试

X IEC 621326:用于测量、控制及实验室用途的电气设备

X EMC要求—第1部分:一般要求

IEC 60601-1-2:医疗电气设备第1-2部分:基本安全和基本性能的一般要求—附加标准:电磁干扰—要求和测试

IEC 61800-3:变速电力驱动系统—第3部分:EMC要求和具体的测试方法

IEC 63044-5-1:家用和建筑电子系统(HBES)及建筑自动化和控制系统(BACS)—第5-1部分:EMC要求、条件和测试设置

减少隔离设计中的复杂性和矛盾

设计隔离式电源可能是设计过程中最具挑战性的一个方面。构建一个解决方案需要权衡各种设计需求,且需要遵守全球多个不同地区的法规要求。由此做出的牺牲往往带来了尺寸、重量和性能方面的负面影响,或者降低了满足EMC标准的能力。

为了顺利满足EMC标准,可以在设计阶段的早期采用已经通过行业标准验证的器件。EMC应该纳入到设计过程中,而不是事后才考虑。采用诸如旁路电容之类的抑制技术会降低电子系统抗瞬变的能力,并增加成本和设计复杂性。ADI公司的下一代isoPower系列产品提供辐射发射抑制技术,无需具备旁路电容,仍可满足EN55022/CISPR22B类标准要求。ADuM5020/ADuM5028采用扩频技术,可降低任意频率下的功率水平。出色的设计、变压器线圈对称性和两个低价小铁氧体的使用有助于减少跨隔离栅流向次接地层的CM电流。ADM5020/ ADuM5028满足CISPR 22/EN 55022 B类要求,在2层PCB上具有大幅裕量,无需采用成本高昂的PCB级RE抑制技术,因此可降低成本。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18709浏览量

261374 -

emc

+关注

关注

174文章

4323浏览量

190336 -

变压器

+关注

关注

0文章

1817浏览量

4010

发布评论请先 登录

采用LDO实现LED控制和亮度匹配的高性价比参考设计包括BOM,原理图和参考指南

电源隔离和锁相环对于DSP中EMI的抑制

采用离散FET设计的EMI抑制技术

如何避免采用复杂的EMI抑制技术以实现紧凑、高性价比的隔离设计

ADI教你简化EMI抑制技术,搞定高性价比隔离设计

EMI 的工程师指南第 6 部分 — 采用离散 FET 设计的 EMI 抑制技术

EMI 的工程师指南第 5 部分 — 采用集成 FET 设计的 EMI 抑制技术

如何避免采用复杂的EMI抑制技术以实现紧凑、高性价比的隔离设计

如何避免采用复杂的EMI抑制技术以实现紧凑、高性价比的隔离设计

如何避免采用复杂的EMI抑制技术以实现紧凑、高性价比的隔离设计

如何避免采用复杂的EMI抑制技术以实现紧凑、高性价比的隔离设计

评论