前言

本文以一个简单的实例介绍RISC-V指令异常的调试过程,思路都是一样的,遇到其他情况时分析过程也类似。

相关内容参考《riscv-privileged-20211203.pdf》

过程

现象是程序执行后进入了异常中断,可以通过GDB的bt命令看到

#12 0x02002e9c in exception () at src/lib/riscv/src/exception.c:55

#13 0x02002b40 in is_exception ()

Backtrace stopped: frame did not save the PC

(gdb)

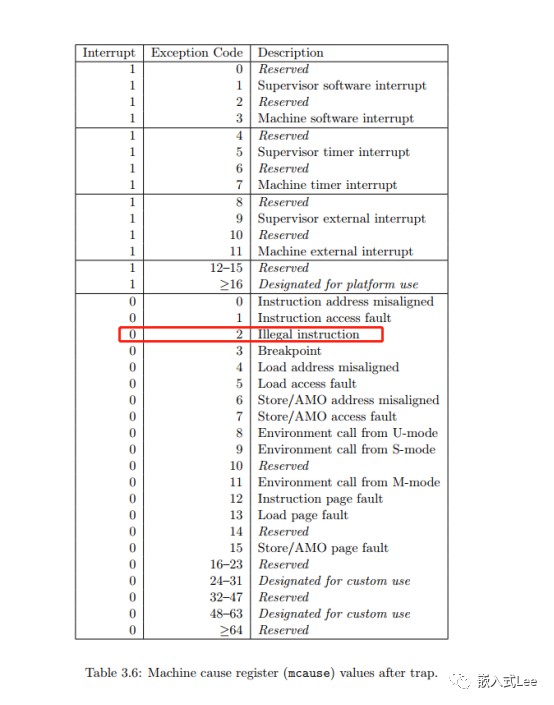

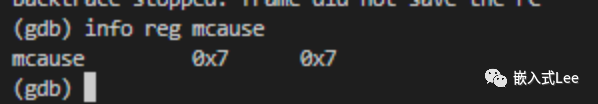

既然是进入了异常中断,那么就需要确认到底是什么异常,

这可以通过mcause寄存器查看

(gdb) info reg mcause

mcause 0x2 0x2

(gdb)

可以看到是非法指令异常

那么我们就搜索文档的Illegal instruction可以查看到所有可能导致Illegal instruction的原因。

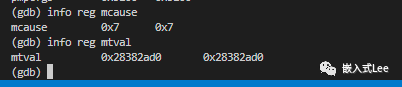

我们搜到以下信息,即mtval寄存器保存了异常指令,mepc指向了异常指令

可以看到mepc的内容是0,那么猜测应该是函数指针未初始化直接调用导致的

(gdb) info reg mtval

mtval 0x0 0x0

(gdb) info reg mepc

mepc 0x0 0x0

(gdb)

到这里基本就确认了方向了,可以重点看哪些地方有函数指针,或者逐步注释函数,或者逐步断点定位即可。

这里很快就确认了是

是如下代码导致

int xxx_ioctl(unsigned int dev_id, unsigned int cmd, void *data)

{

if (dev_id >= xxx_drv.dev_num)

return -1;

return xxx_drv.ops.ioctl(&(xxx_drv.dev[dev_id]), cmd, data);

}

查看函数指针正好是0

(gdb) p xxx_drv.ops.ioctl

$1 = (int (*)(struct xxx_dev_s *, unsigned int, void *)) 0x0

(gdb)

回溯代码确认了是某个外设没有初始化成功则这个回调函数没有初始化。原因就定位了。

总结

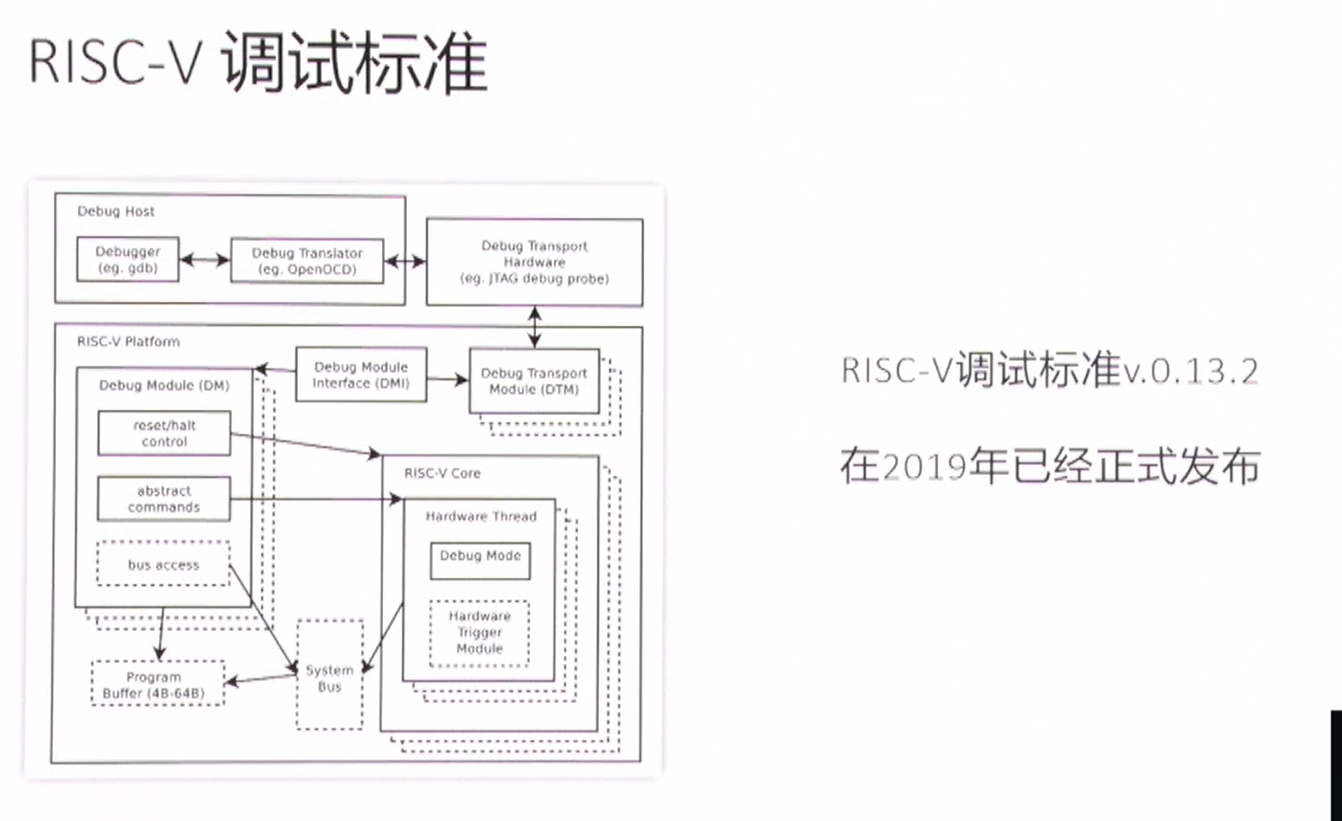

对于异常的调试可以参考手册《riscv-privileged-20211203.pdf》,从异常原因入手,逐渐反推,确认异常触发点然后确定原因。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

指令

+关注

关注

1文章

624浏览量

37668 -

调试

+关注

关注

7文章

653浏览量

35883 -

命令

+关注

关注

5文章

759浏览量

23928 -

RISC-V

+关注

关注

49文章

2952浏览量

53559

发布评论请先 登录

相关推荐

热点推荐

正式的RISC-V基础指令集架构与特权架构规范来了,RISC-V基金会已正式批准

根据RISC-V基金会官网发布的公告,RISC-V 基金会宣布了批准RISC-V 基础指令集架构与特权架构规范,为 RISC-V的可扩展性进

RISC-V的Store AMO access fault调试实例

本文以一个实例分享RISC-V的Store AMO access fault异常的调试过程。Store AMO access fault主要发生在非法地址访问时(栈溢出,指针

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

第2章 RV32I:RISC-V基础整数指令集

本章重点讲解构成RISC-V基础整数指令集的基本指令和指

发表于 01-31 21:10

关于RISC-V学习路线图推荐

的编程方法。

学习RISC-V汇编语言 :

了解RISC-V汇编语言的语法和指令格式,编写简单的汇编程序。

调试与优化 :

使用调试工具(如

发表于 11-30 15:21

RISC-V指令集手册中F指令部分

的设定。舍入模式可以分为静态舍入和动态舍入,静态舍入即按照浮点指令内固定的模式去执行,动态舍入可以通过frm域的值动态选择,此时指令编码中的rm域为111,无效的舍入会引起非法指令异常

发表于 10-22 08:18

RISC-V 发展

不完善的地方,有传言未来可能会形成x86、ARM、RISC-V三足鼎立的天下,但能够形成这个局面,还需要大家的共同努力。RISC-V指令集RISC-V

发表于 04-14 10:18

RISC-V指令异常调试实例

RISC-V指令异常调试实例

评论