前言

00

一般来说,面积是一个设计所消耗的目标器件的硬件资源数量或者ASIC芯片的面积。速度是指设计在芯片上稳定运行时所能够达到的最高频率,这个频率由设计的时序状况决定。

面积和速度是对立统一的矛盾体 ,既想要设计面积最小,又想运行频率最高,这是不现实的。科学的设计目标应该是在满足设计时序要求(包含对设计最高频率的要求)的前提下,占用最小的芯片面积,或者在所规定的面积下,使设计的时序余量更大,频率更高。

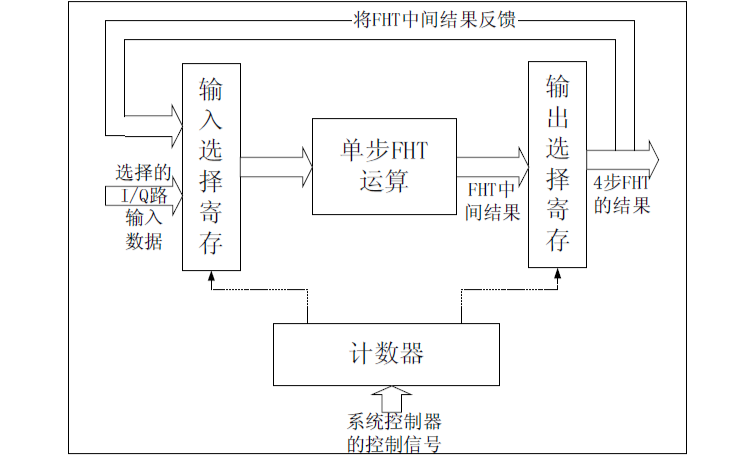

一个设计如果时序余量较大,所能跑的频率远远高于设计要求,能通过功能模块复用减少整个设计所消耗的芯片面积,用速度的优势对换面积的节约。

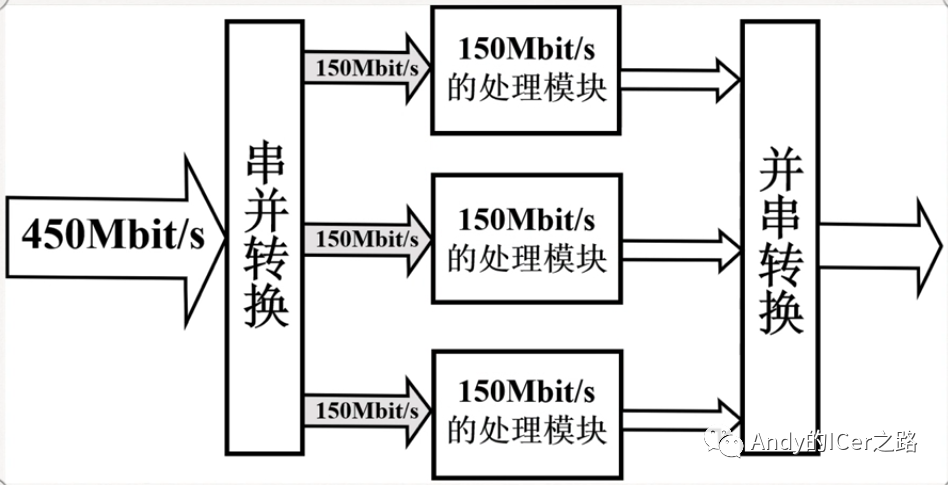

一个设计的时序要求很高,普通方法达不到设计频率,可以通过将数据流串并转换,并行复制多个操作模块,对整个设计采取“乒乓操作”和“串并转换”的思想进行处理,在芯片输出模块处再对数据进行“并串转换”。

串并转换 并串转换

01

例如输入数据流的速率是450Mbit/s,而在FPGA上设计的数据处理模块的处理速度最大为150Mbit/s,在这种情况就应该利用“面积换速度”的思想,至少复制3个处理模块。首先将输入数据进行串并转换,然后利用这3个模块并行处理分配的数据,最后将处理结果并串转换以满足数据速度的要求。

乒乓操作

02

“乒乓操作”是一个常常应用于数据流控制的处理技巧,乒乓操作的结构如下图所示:

数据缓冲模块一般是常用的存储单元,例如双口RAM(DPRAM)、单口RAM(SPRAM)、FIFO等。

第一个缓冲周期:将输入的数据流缓存到数据缓冲模块1;

第二个缓冲周期:通过输入数据选择单元的切换,将输入数据缓存到数据缓冲模块2,同时数据缓冲模块1通过输出数据选择单元输出数据;

第三个缓冲周期:通过输入数据选择单元的切换,将输入数据缓存到数据缓冲模块1,同时数据缓冲模块2通过输出数据选择单元的切换输出数据;

如此循环,直到输入结束。

乒乓操作有两个优点:1、完成数据的无缝缓冲与处理;2、节约缓冲区空间。

完成数据的无缝缓冲与处理 :从上面乒乓操作的描述中可以看出,数据基本上是源源不断地输入输出,只不过是中间的过程用了流水线式的设计来处理。根据这个优点可以 用低速模块处理高速数据流 ,其核心思想还是通过串并转换实现面 积换速度 。

节约缓冲区空间 :例如需要将一帧的数据延时一个时隙后处理,最直接的办法就是将这帧数据缓存起来,然后延时一个时隙进行处理,这时缓冲区的长度是一帧数据的长度。如果使用乒乓操作,用8个时隙完成一帧数据的传输,只需要两个小的缓冲区即可,一个缓冲区是1/8帧数据的大小,其核心思想是 速度换面积 。

流水线设计

03

流水线设计大家应该都不陌生,福特发明了流水线提高了工人的效率,硬件电路也因为流水线而元气满满。

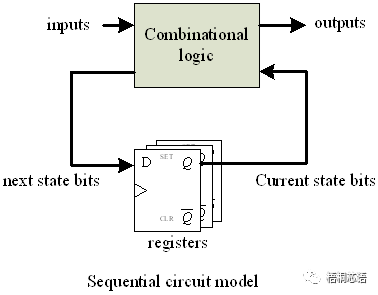

流水线特点: 通过插入寄存器,将长的串行逻辑链分成较小的部分;当系统运算是串行的时候,利用时钟控制,使运算依照顺序接续进行;在任何给定时刻,大部分电路都在工作。

流水线好处: 每一部分延时较小,可以使用更快的时钟;大部分电路同时进行运算,可以提高数据通过量。

电路的最高频率取决于最长组合逻辑链路的延迟值,所以减少最长组合逻辑链的延迟值,有利于提高电路速度。我们先来看一下不使用流水线的电路有什么问题:

可以从上面的图看出,组合逻辑链会有很大部分的闲置电路,根据这个基础我们来分析一下计算log(|a+b|)的硬件电路:

计算最小周期,即计算出电路最大频率,对照电路的最小周期主要是加法器延时+求绝对值延时+求对数延时,因为一个部分电路在工作时,另一个部分的电路在闲置;

而流水线电路的最小周期主要是取(加法器延时,求绝对值延时,求对数延时)的最大值,可以看出流水线电路比原来的电路频率大约快3倍左右,因为流水线是每一个部分的电路都在工作,效率大大提高。

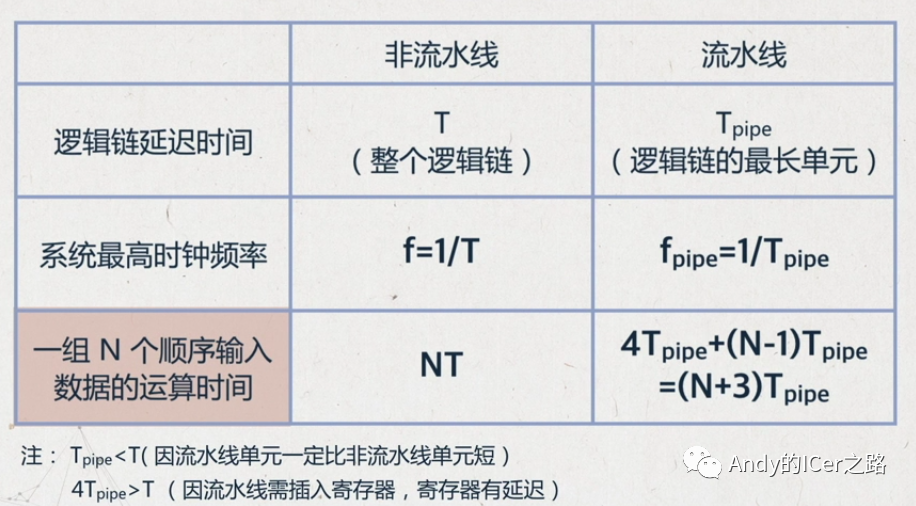

接下来我们来看一下流水线与非流水线电路的比较,以4级流水线为例。

以上是4级流水线的结构图, 要注意的是流水线是按照延迟划分的,不是按照功能划分的 。具体流水线与非流水线电路的性能比较如下:

根据上面的性能比较表格,可以得知,具体使用流水线好还是非流水线好,还是要根据实际情况计算比较,一般来说流水线会较好。

另外, 流水线分割点及级数的确定要考虑的因素:

①单元延迟时间及时钟频率的大小决定了数据通过速率;

②过多的级数不一定能产生最快的结果;

③太多寄存器的插入会导致芯片面积增加,布线困难,时钟偏差增加;

-

FPGA设计

+关注

关注

9文章

429浏览量

27996 -

加法器

+关注

关注

6文章

183浏览量

31230 -

RTL

+关注

关注

1文章

393浏览量

62388 -

DPRAM

+关注

关注

0文章

2浏览量

11233 -

ASIC芯片

+关注

关注

2文章

94浏览量

24632

发布评论请先 登录

速度面积互换设计原则简析

FPGA设计思想,速度和面积互换原则不可忽视

Labview 之面向对象编程。 里面有个例子 和视频教程地址

FPGA设计的指导原则

FPGA设计的十五条原则详细解析

FPGA的指导性原则详细资料说明

RTL设计指导原则之面积和速度互换

RTL设计指导原则之面积和速度互换

评论