在RTL编码中考虑延时

01

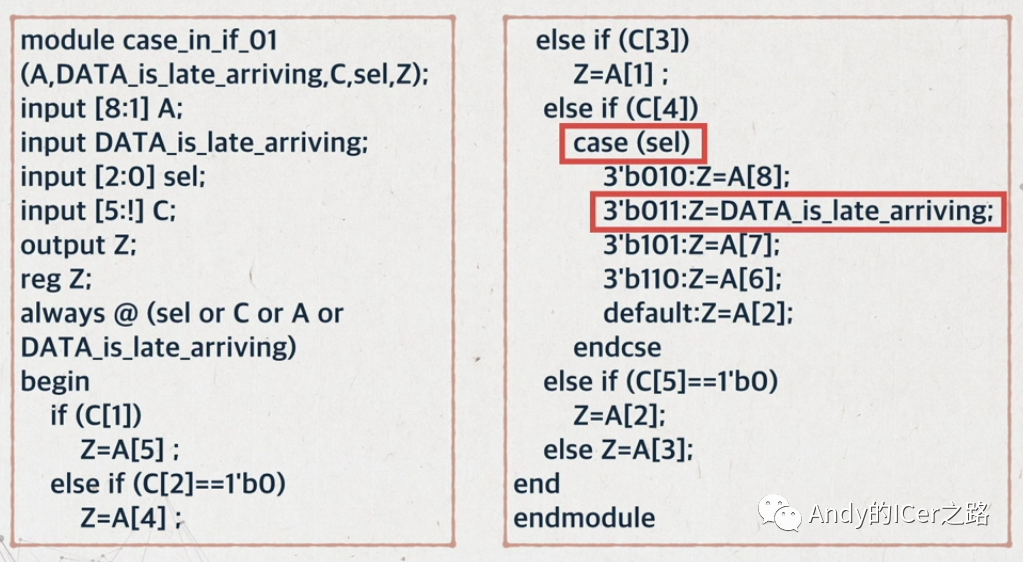

看下面一段代码,第四个else if 分支中的数据信号DATA_is_late_arriving延时比较高,要怎么处理,将电路的性能提高?

一般最高优先级给最迟到的关键信号,因此要将DATA_is_late_arriving这个信号单独拿出来分析,代码如下:

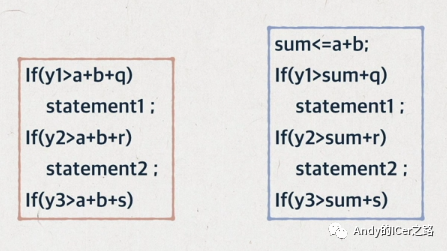

再来看下面一段代码以及其电路图,假设A信号到来比较晚,如何修改能够提高电路性能?

核心思想还是将延迟高的信号往后面优先级更高的地方放 ,只需做小小修改即可,代码如下:

在RTL编码中考虑面积

02

随着芯片工艺的进步和生产成本的降低,其实面积已经显得没有时序问题那么重要。一般综合过程中可以对面积进行优化,但是在RTL设计的时候还是需要尽量减小面积的开销,这样可以达到事半功倍的效果。

例如RTL代码中的一个“+”可能对应着一个64位的加法器,所以条件语句中的比较运算,我们要判断其必要性,是否能用更简单的运算代替。

比如判断A是否小于32(if(A<32)),可以改成判断A的第五位是否为0(if(A[5]==1'b0)),这两种表达形式是等价的,但是后者的判断条件更节省面积,相当于用一个1bit的逻辑门代替一个6bit的比较器,如果我们遇到定值的比较都可以这么操作。

如果必须使用复杂的运算符,则应考虑是否可以资源共享,尽管电路逻辑综合工具也会在综合的过程中采用资源共享的方法进行优化,但是,综合器的策略是有限的,因此,在编写RTL的时候,应该尽量考虑共享,而不是把这项工作完全留给综合工具。

如上面的代码所示,右边是修改之后的代码,这样可以减少两个不必要的加法器,实际的设计中资源共享可能不会像这样明显,因此平时应该按照这样的思路多多练习。

还有一种情况就是关于多比特位的信号问题, 多比特位操作意味着成倍使用资源 ,在使用多比特位的信号时,看看这个信号是否所有比特位都需要参与操作,如果不是,则可以只对需要的部分比特进行操作。例如访问RAM的地址有8比特,而写入操作时从0开始,每隔32个地址写入一个值,地址的产生可以有两种写法。显然右边这种写法操作的比特位会比左边的代码少。

在RTL编码中考虑功耗

03

一个电路中的功耗影响因素主要以下4个因素: 该点电路的翻转次数、电路的工作频率、该点的电容还有电压值 。

但是负载电容、工作电压和工作频率这些都是RTL设计无法改变的因素,因此在RTL级设计主要考虑尽量降低电路的翻转频率。

主要措施包括如下:

①门控时钟;

②增加使能信号,使得部分电路只有在需要工作时才工作;

(门控时钟与增加使能的区别是:门控时钟是关掉时钟,而使能关闭的是电路的功能,但是时钟仍然在翻转,显然门控时钟更好)

③对芯片各个模块进行控制,在需要工作时才工作;

④除了有用信号和时钟的翻转会消耗功耗,组合逻辑产生的毛刺也会大量消耗功耗。但是毛刺在设计中无法避免,因此,只有尽量减少毛刺在电路中的传播,才可以减少功耗。即在设计中,尽量把产生毛刺的电路放在传播路径的最后。另外可以使用一些减少毛刺的技术;

⑤对于有限状态机,可以通过低功耗编码来减少电路的翻转,比如将二进制编码改为独热码、格雷码等。

在RTL编码中考虑布线问题

04

如果可以在RTL编码阶段考虑代码,可能对布线产生的影响就可以避免最后出现无法布通的情况。

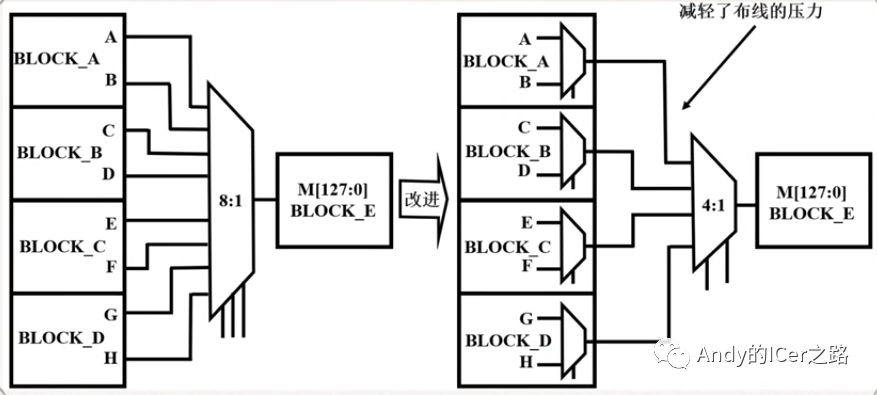

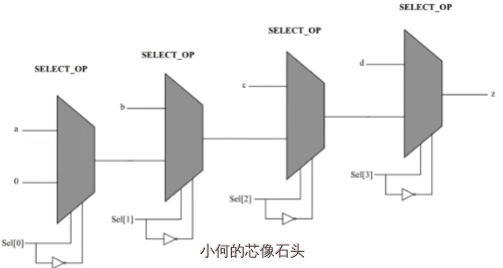

热点是指设计的功能需要在一个面积内占用大量的布线资源。热点产生原因:RTL编码时使用了特定的结构,如很大的mux。

这种结构产生的热点,在综合的时候,导致的延迟是看不出来的,只有到了布线阶段才能给看到它的负面影响。因此,我们在RTL阶段应该重视这种电路,及早发现可能在布线阶段产生的问题。

如果设计的功能中确实需要采用很大的mux,可以通过其他方式改变他的结构。其基本的思想就是将一个大的mux分解为多级较小的mux。

-

RAM

+关注

关注

8文章

1400浏览量

120989 -

比较器

+关注

关注

14文章

1936浏览量

112077 -

加法器

+关注

关注

6文章

183浏览量

31547 -

RTL

+关注

关注

1文章

395浏览量

62875 -

门控时钟

+关注

关注

0文章

27浏览量

9247

发布评论请先 登录

【设计技巧】PCB设计中考虑电磁兼容(上)

【设计技巧】PCB设计中考虑电磁兼容(下)

介绍RTL设计引入的后端实现过程中的布线问题

基于RTL的16位嵌入式微控制器(A8096)的设计

RTL功耗优化

现代SAR和∑-Δ型模数转换器的主要优势之一是在设计中考虑了易用性

芯片RTL设计中如何做到低功耗设计

在RTL设计中如何做到低功耗设计

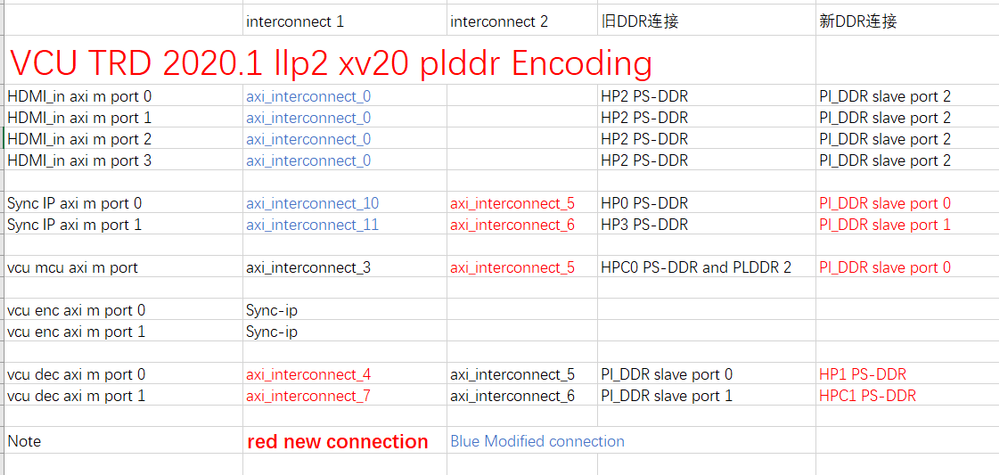

ZCU106在PLDDR实现超低延时编码

在RTL编码中考虑延时、面积、功耗与布线的问题

在RTL编码中考虑延时、面积、功耗与布线的问题

评论