作者:Anand Shirahatti,Mohd Adil Khan,Jamshed Alum

PCI Express Gen 4自2011年底以来一直在开发中,目标是令人印象深刻的16GT / s数据速率。物联网 (IoT) 继续发展其对一切互联的承诺,为下一代服务器和通信设备提供承诺的 16 GT/s 带宽将非常重要。

PCI Express Gen 4 的实施正在向 Gen 4 0.7 版本迈进。重要的是,不仅物理层提供 16 GT/s 的速率,而且整个协议栈应该能够优化完全分配的带宽。

为了利用全带宽,以下两个关键功能正在获得牵引力:

10 位扩展标签支持

按比例调整的流量控制配额

在即将发布的 PCIe 博客中,我们将简要介绍这些功能,以便快速启动任何提升最新规范的功能,并讨论上述功能带来的一些验证挑战和解决方案。博客范围仅限于根复合体和终结点。开关和桥接器不包括在内。

为什么这两个功能越来越受欢迎?

随着 16 GT/s 带宽的增加,PCIe Gen 4 提出了有效利用带宽以充分利用的新挑战。第 4 代延迟没有改变,并且引入了两个关键功能来有效处理延迟。第一个是 10 位扩展标记,用于增加未完成事务总数,第二个功能是缩放流控制信用,以增加通告和使用的总信用。这两个功能一起有效地隐藏了延迟的影响,从而使应用程序能够饱和链路带宽,从而获得第 4 代速度的全部优势。

10 位扩展标记

10 位扩展标记将标记字段的总大小从 8 位增加到 10 位。这将未完成的未发布请求 (NPR) 的数量从 256 个增加到 768 个。

特征:

该功能是通过抢救请求标头、设备功能 2 寄存器和设备控制 2 寄存器中的保留位来实现的。

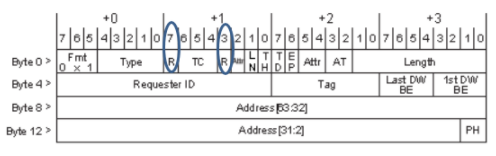

请求标头字节 1 中的两个保留位 [7, 3] 被重新定义,以获得两个额外的标记位。重载请求标头中的保留位有一个缺点。保留位初始值“0”不能重复使用。因此,总 10 位扩展标记空间(而不是 1024 个未完成标记)仅限于 768 个。从 2 位开始,只有 3 种组合 [01, 10, 11] 可用。256 * 3 = 768。不使用“00”。

图 1:10 位扩展标记支持的请求标头更新(图片由 PCI-SIG 提供)

器件功能寄存器2,另外两个保留位[17,16]用于添加两个新功能。一个用于 10 位标记完成器,另一个用于 10 位标记请求程序。请注意,支持 10 位标记完成器功能的接收方/完成器必须正确处理 10 位标记,无论其 10 位标记请求器启用位设置如何。

设备控制2寄存器11的保留位被重新定义为10位标签请求者使能控制。

功能验证

从正常操作的角度来看,每个未发布的请求单独和组合应该能够达到启用 768 位扩展标记功能的请求者的 10 个未完成请求中的最大值。需要验证从两端和单端启用请求者功能。这需要 VIP 能够在 DUT 充当请求者时阻止完成。

需要验证扩展标记位损坏的错误方案。这在实际系统中可能会发生,因为中间交换机或对等体不支持 10 位扩展标记。

审核编辑:郭婷

-

开关

+关注

关注

20文章

3307浏览量

97505 -

PCIe

+关注

关注

16文章

1422浏览量

87554 -

桥接器

+关注

关注

0文章

84浏览量

45683

发布评论请先 登录

PCI Express Gen 4验证挑战和解决方案

PCI Express Gen 4验证挑战和解决方案

评论