大家好!今天给大家分享的是4位计数器的代码以及仿真程序。

4位计数器代码:

module count4(out,reset,clk); output [3:0] out; input reset,clk; reg [3:0] out; always @( posedge clk) begin if (reset) out<=0; // 同步复位 else out<=out+1; // 计数 end endmodule

4位计数器的仿真程序:

`timescale 1ns/1ns `include " count4.v " module coun4_tp; reg clk,reset; // 测试输入信号定义为 reg 型 wire [3:0] out; // 测试输出信号定义为 wire 型 parameter DELY=100; count4 mycount(out,reset,clk); // 调用测试对象 always #(DELY/2) clk = ~clk; // 产生时钟波形 initial begin // 激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end // 定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule

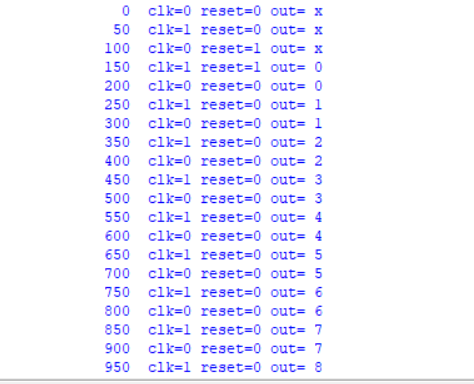

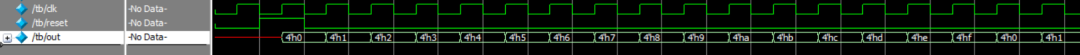

modelsim仿真结果:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21320浏览量

593194 -

仿真

+关注

关注

50文章

3872浏览量

132160 -

计数器

+关注

关注

32文章

2121浏览量

92976 -

程序

+关注

关注

114文章

3631浏览量

79541 -

代码

+关注

关注

30文章

4555浏览量

66767

原文标题:4位计数器代码及仿真程序

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

16位计数器仿真没结果,求助?

想写个16位计数器,仿真没结果,是不是哪里逻辑错了 [code]module counter_16(input clk,input clr ,output reg[15:0] outda

发表于 02-27 15:36

基于verilog hdl的19位计数器的仿真问题

一个19位计数器的仿真问题module counter(inclk,rst_n,en,out);input inclk,rst_n,en;output[18:0] out;reg[18:0] out

发表于 04-15 15:00

以太网控制器计数器模块实现代码

计数器模块提供数据发送过程中需要的所有计数器:DlyCrcCnt 用来在 CRC 校验序列产生过程中计数;按照 4 位传输时采用 NibCn

发表于 01-03 09:10

怎么实现两个32位计数器计数速率高达3GHz

两个32位计数器,但我希望这些计数器的计数速率高达3GHz。看起来低端FPGA(即Spartan 6)的最大频率为200-300 MHz。因

发表于 04-19 13:34

关于FPGA在仿真软件中计数器提前计数的问题

FPGA的人来说,非常之实用。但是,部分工程师在做仿真时,有时候会出现违反这一原则的奇怪现象。例如下面这个案例。关于在仿真软件中,为什么计数器的判定会在不满足加一条件的时候进行加一操作

发表于 04-24 14:54

用于4位计数器的SDK C程序怎么写

嗨好朋友,我正在研究4位计数器我已经创建了IP以及框图设计。现在停止使用SDK c程序启动硬件。这是我在HLS中的反击#include #include“ap_int.h”#defin

发表于 05-19 12:18

基于Proteus的任意进制计数器设计与仿真

提出一种基于Proteus 软件的任意进制计数器的设计。以74LS163 集成计数器为基础,用置数法设计了两种48 进制计数器,采用Proteus 软件对计数器进行

发表于 07-29 18:53

•0次下载

基于FPGA的十进制计数器

本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

发表于 12-20 14:52

•2次下载

FPGA设计:4位计数器代码及仿真程序

FPGA设计:4位计数器代码及仿真程序

评论