定义

4.1 阻抗:阻抗就是电阻+电抗,一般阻抗分特性和差分两种结构。

4.2 特性阻抗:在电路(含有组装的元件)两点间的传输波中的电压与电流的比值,即传输线的任一点对传输波产生的阻力,它由电阻和电抗(电抗=感抗和容抗)所组成。

4.3 差分阻抗:在印制板中导线平行于接地面,中间由介质隔开的一种传输线结构。

4.4 阻抗匹配:在电子电路中的信号传输,由电源输出起,希望在无能量损失条件下传输到接受端,而中间不发生任何信号反射,因此要求印制板中的阻抗(ZL)和电源端的阻抗(Z0)相等,即称之阻抗匹配。如阻抗不匹配,则收到的信号失真。

4.5 阻抗控制:按客户的阻抗叠层结构进行设计,过程中精确控制线宽、铜厚即可。(无须设计阻抗测试条,成品无须阻抗测试)

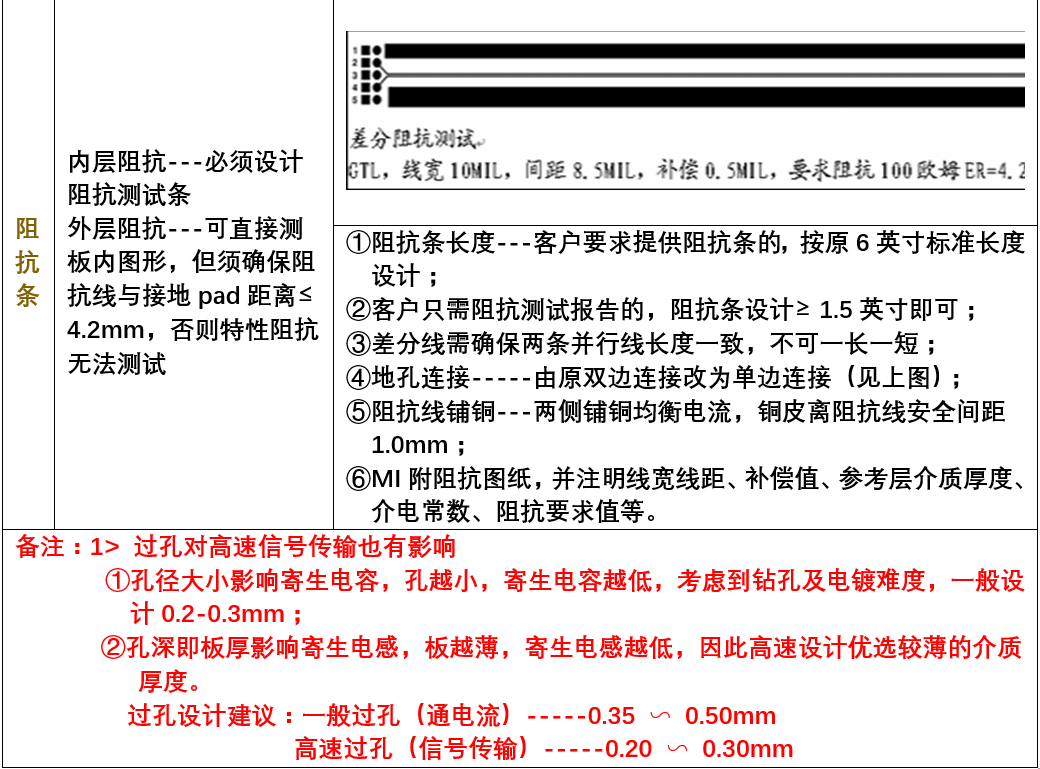

4.6 阻抗测试:按客户的阻抗要求进行线宽、铜厚及叠层结构设计,并在PCB工作边上设计同等的阻抗测试条,过程中精确控制线宽、铜厚,成品需阻抗测试仪检测合格方可出货。

实施要点

6.1 阻抗-设计简介

6.1.1阻抗设计目的

阻抗设计用于减少电子反射和能量衰减,确保信号在 PCB 线路和内部连接之间的转换正确无误,对产品的性能提供更好地控制和保障(阻抗匹配)。

6.1.2阻抗常用领域

1、 高频电路板 (发射系统)

6.1.3特性阻抗原理

什么样的线路才被定义为传输线?在国际标准IPC-2141 3.4.4说明其原由:当信号在导线中传输时,若该导线长度大于信号波长的1/7,则该导线应被视做传输线。例如当某电磁波信号以时钟频率为900M HZ(GSM手机传输频率)在导线中传播时,则如果线路的长度大于1/7波长=1C/7F=4.76cm时,该线路就被定义为传输线。

6.1.4阻抗计算公式

众所周知,直流电路中电流传输时遇到的阻力叫电阻,交流电路中电流遇到的阻力叫阻抗,而高频(>400M HZ)电路中传输信号所遇到的阻力叫特性阻抗,在高频情况下,印制板上的传输信号铜导线可以被视为由一串等效电阻及一并连电感所组合而成的传导线路,而此等效电阻在高频分析时小到可以忽略不计;因此,在对一个印制板的信号传输进行高频分析时,则只需考虑杂散分布之串联电感及并联电容的效应,简化可以得到以下公式:

** Z0=R+√L/C √≈√L/C ( Z0为特性阻抗值)**

6.1.5阻抗设计原则

1、在数字信号传输时,印制板线路的阻抗值必须与头尾元件的电子阻抗相匹配,如果不匹配的话,所传送的信号能量将出现反射、散失、衰减或延误等现象,从而产生杂信;

2、由于电子元件的电子阻抗越高时,其传输速率才越快,因而电路板的特性阻抗值也要随之提高,才能与之匹配;

3、射频通信用的PCB,除强调 Z0外,有时更加强调板材本身具有低的 Er值(介质常数)及低的Df值(介质损耗因子)。高频信号在介质中的传输速度为C/ Er,由此可知:Er越小,传输速度越快,这也是为何高频要用低介质常数的高频材料( Df影响着信号在介质传输过程中的失真,Df越小,失真越小)。

6.1.6阻抗的常见结构形式

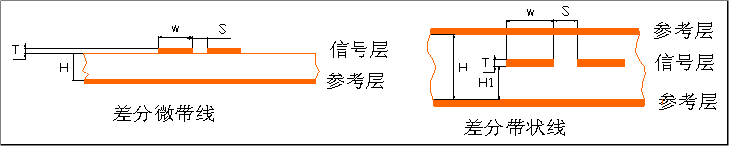

在线路板的设计中,传输信号最常见的有以下2种特性和2种差分布线方式:

常见特性阻抗设计结构

常见差分阻抗设计结构

6.1.7特性阻抗计算方法

⊙ 以上公式中:

Er-----印制板基材的介质常数

W-----印这制板传输导线宽度

T------印制板传输导线厚度

H------印制板介质厚度

(上述公式未考虑外层阻焊,一般印阻焊后阻抗值会下降,特性约下降2-4欧姆,差分下降 5-10欧姆)。

6.1.8影响阻抗的因素

1、 阻抗与板材介质常数Er的关系—成反比 Z。和 Er的平方根成反比,其影响程度相对较小;但是,对与高频线路来说,Er是非常重要的,从电磁波理论中的马克斯威尔公式可知,正玄波信号在介质中的传输速率(VS)与光速成正比,而与传输介质成反比,即:

**Vs=C / Er **

由公式可知,要提高信号的传输速度,必须降低材料的介质常数,同时,要获得高的传输就必须采用高的特性阻抗值,而高的特性阻抗就必须选用低的介质常数,这也就是为什么高频线路板为何多采用PTFE、BT、PI等材料,因这些料具有低的Er值。以下为几种常用板料的 Er值:

2、 阻抗与板材介质厚度的关系—成正比

介质层的厚度和 Z。成正比,是影响阻抗的一个重要因素,因此对于阻抗要求高的板,介质层厚度的均匀性是保证成功设计和制作阻抗线路板的关键一步,在设计中,应注意的是:随着导体走线密度的增加,其介质厚度的增加会引起电磁干扰的增加。因此,对于高频线路和高数字线路的信号传输随着导体布线的增加,应减少介质厚度以消除或降低电磁干扰。

(电磁干扰带来的杂信或串扰问题,其出路只有降低 Er,才能有利于采用较薄的介质厚度)

3、 阻抗与线路铜厚的关系—成反比铜箔厚度也是影响阻抗值的一个重要因素,铜箔越厚,其阻抗值越小;同时,铜箔厚度对线路蚀刻也会带来影响(厚度增加时,精细线路难以制作)。

4、 阻抗与线宽(W)的关系—成反比(差分阻抗与线距还有关系)由公式可以看出,导线宽度越小,Z。越大,与之成反比;导线宽度变化所导致的Z。值变化比导线厚度对Z。的影响程度要大得多,因此,改变和控制线宽是控制特性阻抗值最根本的途径和方法。(制造细线路也是提高高频线路和高效数字线路Z。的一个重要方法)

5、 其次,对于外层阻抗,阻焊厚度对阻抗值也有影响—成反比(印阻焊后阻抗值会降低,一般特性影响约2-4欧姆,差分影响5-10欧姆)。

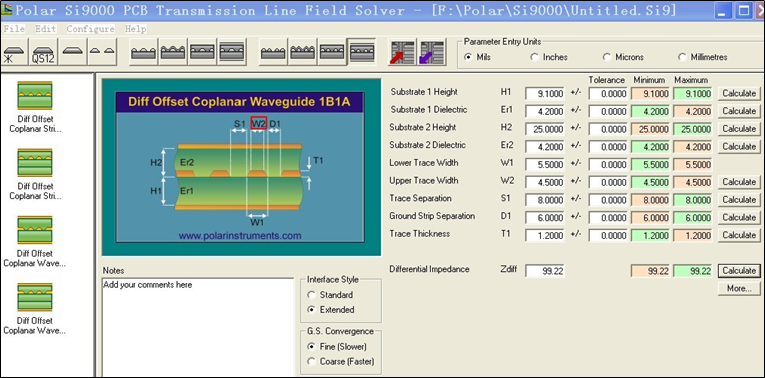

6.1.9 阻抗模拟计算

阻抗设计时,一般会先用专业软件(Polar)进行模拟计算,再根据实际结构进行微调。

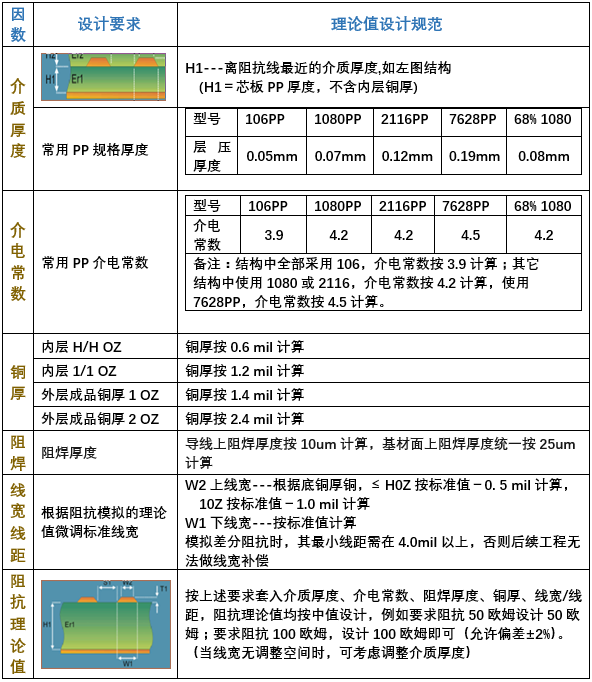

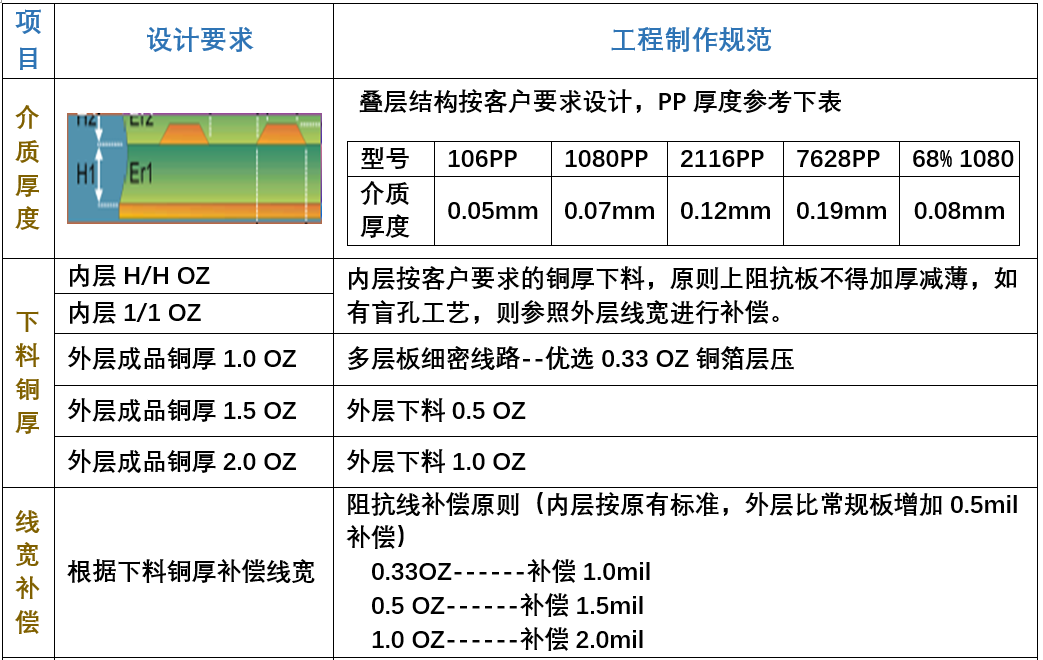

6.2 阻抗-设计规范

6.2 阻抗-设计规范

6.4阻抗-生产制作规范

6.4.1下料工序

6.4.1.1 使用的板料类型、板料厚度、铜箔厚度必须按MI要求生产。

6.4.1.2 阻抗板不接受自压芯板的方式以及铜面加厚减薄的方式进行制作。(压合厚度及铜面加厚偏差较大,无法完全受控)。

6.4.2内层线路

6.4.2.1 内层前处理微蚀:允许返工1次,不允许返工第2次(铜厚偏薄会导致阻抗偏高)。

6.4.2.2 对位曝光前测量菲林线宽、线距,对菲林进行全面检查,避免定位问题出现。

6.4.2.3 对位曝光时必须先做首板,QA用百位镜测量阻抗线宽/线距,合格才可批量生产。

6.4.2.4 曝光生产过程中,每生产1-2PNL或1框板用粘尘辘清洁菲林及麦拉一次;每生产3-5框板用酒精对曝光玻璃、麦拉擦洗一次,每套菲林生产25PNL进行一次全检。

6.4.2.5 阻抗板尽量避免返工。(不要采用阻抗板做曝光尺,生产时可采用其它板来做)

6.4.2.6 显影放板时必须将有阻抗线控制那一面朝下放板;如两面都有阻抗线,则阻抗线较

多或线路较密的一面朝下放板生产。

6.4.2.7 阻抗板QA抽检时按AQL0.40 进行抽检,并严格按0收1退执行。

6.4.3内层蚀刻

6.4.3.1 内层负片均采用酸蚀工艺,必须按要求做首件确认,满足要求后才能批量生产。

6.4.3.2 阻抗线宽(阻抗条及板内阻抗线)尽可能控制在要求值的中、上限。例如:阻抗线宽要求:0.20mm,公差+/-10%,那么蚀刻后要求阻抗线宽控制在0.20mm--0.22mm之间。(因内层棕化时有微蚀或返工,对线宽及铜厚有一定影响)

6.4.3.2 蚀刻放板时需将有阻抗线控制那一面朝下放板,如两面都有阻抗线的板,则阻抗线较多或线路较密的一面朝下放板。

6.4.3.4 阻抗板批量生产过程中必须加严检测频率,每生产30PNL做一次线宽检测,发现异常及时知会相关人员跟进改善。

6.4.4 AOI/内蚀检

6.4.4.1 所有阻抗板必须安排AOI检测,板内阻抗线如有开路,不允许补线;缺口可以进行邦线处理,但需保证邦线后的阻抗线宽及结合力满足要求。

6.4.4.2 阻抗条上如有开路及缺口,同样必须邦线,其在后序的阻抗检测中,检测阻抗条的结果同样可以代表生产板的阻抗情况。

6.4.5棕化

6.4.5.1 必须先做首板确认,OK后才能批量生产。

6.4.5.2 阻抗板内层铜厚≤HOZ的,棕化不允许返工;内层铜厚≥1OZ的,最多允许返工一次。(因棕化会咬铜,返工次数过多,会造成铜厚偏薄、线幼,影响阻抗控制精度)。

6.4.6压合

6.4.6.1 使用的铜箔、PP片及层压结构必须按MI要求生产。

6.4.6.2 注意叠板方式及压板参数的控制,尽可能保证板厚的一致性。

6.4.6.3 阻抗板批量生产时,需先做2-4PNL首板进行确认,重点检查板面有无层压凹坑,板厚测量是否符合品质要求;如有异常,及时反馈品质/工艺处理。

6.4.7外层线路

6.4.7.1 对位曝光前测量菲林线宽、线距,对菲林进行全面检查,避免定位问题出现。

6.4.7.2 对位曝光时必须先做首板,QA用百位镜测量阻抗线宽/线距,合格才可批量生产。

6.4.7.3 曝光生产过程中,每生产1-2PNL或1框板用粘尘辘清洁曝光玻璃及麦拉一次;每生产3-5框板用酒精对曝光玻璃、麦拉擦洗一次,每套菲林生产25PNL进行一次全检。

6.4.7.4 显影放板时必须将有阻抗线控制那一面朝下放板,如两面都有阻抗线,则阻抗线较多或线路较密的一面朝下放板。

6.4.7.5 阻抗板线检时,QA按AQL0.40 进行抽检,并严格按0收1退执行。

6.4.8图形电镀

6.4.8.1 注意夹板方式及电镀参数的控制,尽可能保证板面铜厚均匀一致;阻抗板图电时靠缸壁两侧必须夹分流条。

6.4.8.2 批量生产需做首槽板确认,按要求参数做一飞巴板后,随机抽取1PNL送物理室打切片确认孔铜、面铜、锡厚是否合格;合格后随机抽取1-2PNL板进行蚀刻,蚀刻时确保线宽/线距符合要求,并送物理室进行阻抗检测,检测合格才可批量生产;如有异常,及时反馈品质/工艺处理。

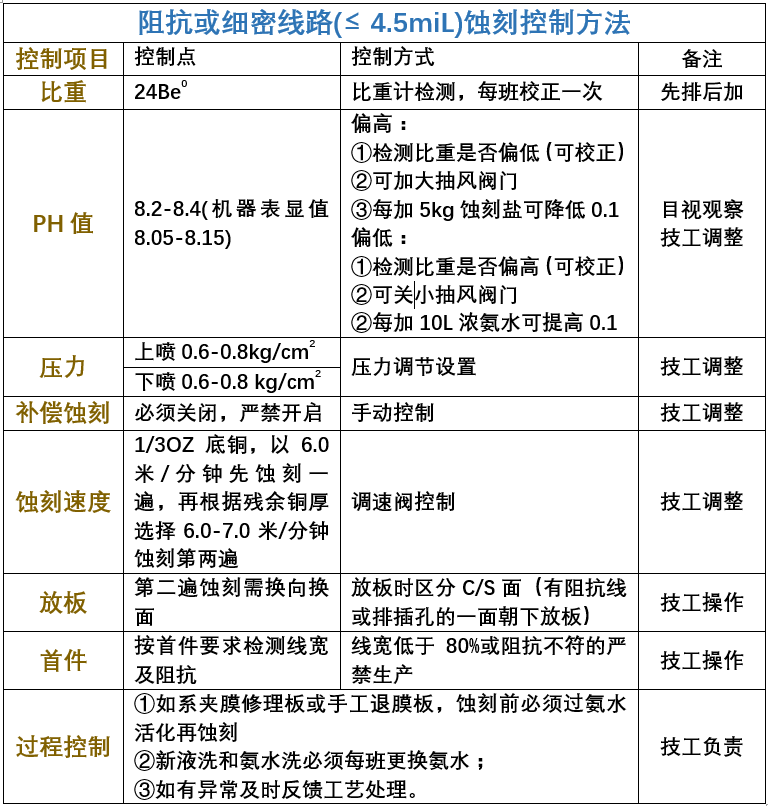

6.4.9外层蚀刻

6.4.9.1 每批阻抗板蚀刻时需做1-2PNL首板送物理室检测阻抗值,首板生产时操作员需记录生产的参数,依据阻抗仪检测的结果来调整蚀刻参数及线宽的大小。

6.4.9.2 生产过程中停机、未连续生产同一型号的阻抗板达2小时以上时,需按4.9.1要求重做首板,阻抗值确认OK后才能批量生产。

6.4.9.3 蚀刻工序生产时,阻抗值控制在要求的中上限,例如:特性阻抗要求50 Ω±10%,阻抗值控制在50-55Ω之间;差分阻抗值要求100Ω±10%,阻抗值控制在100-110Ω之间。(因阻焊工序后,特性阻抗会减少阻值2-4Ω,差分阻抗会减少阻值5-10Ω)

6.4.9.4 蚀刻放板时需将有阻抗线控制那一面朝下放板,如两面都有阻抗线,则阻抗线较多或线路较密的一面朝下放板生产。

6.4.9.5 如果在阻抗合格的情况下,线宽偏差太大,则需通知品质及工艺共同跟进处理。

6.4.9.6 每批阻抗板在蚀检工序检验时,必须安排AOI扫描, 如发现残铜或缺口等异常,需及时通知相关人员跟进处理。

6.4.10 阻焊

6.4.10.1 正常阻抗板生产时按正常生产参数和流程生产。

6.4.10.2 对于蚀刻工序检测外层阻抗超出最大上限的板,允许阻焊加印处理,以适当降低阻抗偏差值。

6.4.11 其它

上述6.4.1—6.4.10中未设计到的其它工序,按本厂的相关要求正常生产控制即可。

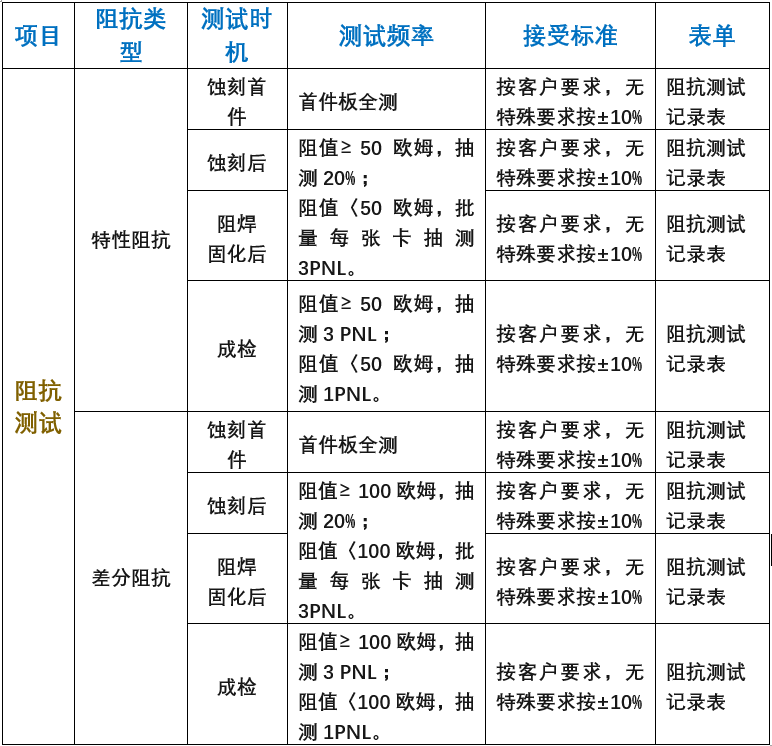

6.5.阻抗检测

由工序送阻抗板到物理室,在泰克阻抗测量仪上进行阻抗检测,测试频率界定如下

备注:

①内层及外层阻抗无阻焊印刷的板,阻抗标准按±10%控制。

②对于外层阻抗有阻焊印刷的板,蚀刻工段阻抗可按中、上限控制,允许超出上限公差5%(因阻焊工序后特性阻抗会减少阻值2--4Ω,差分阻抗会减少阻值5--10Ω),但需品质签字放行。

③实验室人员规范阻抗测试操作,发现阻抗不合格的板要多次测试确认(≥2次),排除人为测量误差(品质需备用一套新测试线放置现场)

6.6阻抗异常分析

对于阻抗不符的板,实验室第一时间打切片进行确认,主要对线宽、线距、铜厚、介质厚度做简单对比分析;如原因仍旧不明,可开单给工程查询或反馈工艺协助分析处理。

-

PCB设计

+关注

关注

396文章

4907浏览量

94010 -

电磁波

+关注

关注

21文章

1498浏览量

55383 -

等效电阻

+关注

关注

7文章

60浏览量

11907 -

差分阻抗

+关注

关注

1文章

27浏览量

10593

发布评论请先 登录

阻抗控制规范简析

阻抗控制规范简析

评论