基于DWC2的USB驱动开发-0x06 DWC2 USB2.0 IP 头文件与寄存器的读写操作 (qq.com)

前言

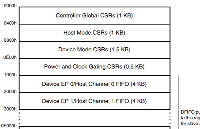

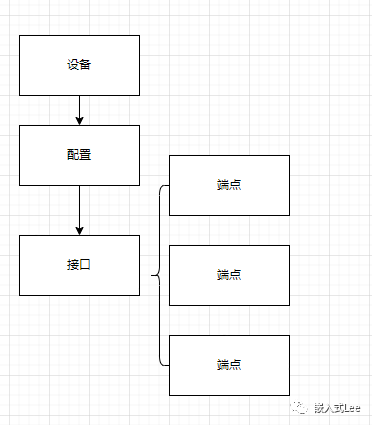

上一篇我们介绍了控制器的寄存器,而驱动的编写底层无非就是配置各种寄存器,所以第一步先要准备寄存器的头文件,对寄存器的操作进行封装。

我们这里提供两种形式,结构体形式和宏的形式。

结构体形式的头文件

该方式的好处是方便阅读,且编辑器可以自动补全输入。

先定义一个总的结构体包含所有寄存器

typedef struct usb_otg_reg {

gotgctl_u gotgctl;

gotgint_u gotgint;

gahbcfg_u gahbcfg;

gusbcfg_u gusbcfg;

grstctl_u grstctl;

gintsts_u gintsts;

gintmsk_u gintmsk;

grxstsr_u grxstsr;

grxstsp_u grxstsp;

grxfsiz_u grxfsiz;

gnptxfsiz_u gnptxfsiz;

gnptxsts_u gnptxsts;

uint32_t reserved_0;

gpvndctl_u gpvndctl;

uint32_t reserved_1[3];

ghwcfg1_u ghwcfg1;

ghwcfg2_u ghwcfg2;

ghwcfg3_u ghwcfg3;

ghwcfg4_u ghwcfg4;

uint32_t reserved_2[2];

gdfifocfg_u gdfifocfg;

uint32_t reserved_3;

grefclk_u grefclk;

uint32_t reserved_4[38];

hptxfsiz_u hptxfsiz;

dieptxf1_u dieptxf1;

uint32_t reserved_5[446];

dcfg_u dcfg;

dctl_u dctl;

dsts_u dsts;

uint32_t reserved_6;

diepmsk_u diepmsk;

doepmsk_u doepmsk;

daint_u daint;

daintmsk_u daintmsk;

uint32_t reserved_7[4];

dthrctl_u dthrctl;

uint32_t reserved_8;

deachint_u deachint;

deachintmsk_u deachintmsk;

diepeachmsk0_u diepeachmsk0;

uint32_t reserved_9[15];

doepeachmsk0_u doepeachmsk0;

uint32_t reserved_10[31];

diepctl0_u diepctl0;

uint32_t reserved_11;

diepint0_u diepint0;

uint32_t reserved_12;

dieptsiz0_u dieptsiz0;

diepdma0_u diepdma0;

dtxfsts0_u dtxfsts0;

diepdmab0_u diepdmab0;

diepctl1_u diepctl1;

uint32_t reserved_13[119];

doepctl0_u doepctl0;

uint32_t reserved_14;

doepint0_u doepint0;

uint32_t reserved_15;

doeptsiz0_u doeptsiz0;

doepdma0_u doepdma0;

uint32_t reserved_16;

doepdmab0_u doepdmab0;

doepctl1_u doepctl1;

uint32_t reserved_17[183];

pcgcctl_u pcgcctl;

pcgcctl1_u pcgcctl1;

} usb_otg_reg_t;

然后每个寄存器都按照结构体解析

以 gotgctl_u gotgctl;为例

typedef union gotgctl_union {

uint32_t w;

struct {

uint32_t sesreqscs:1; // [0]

uint32_t sesreq:1; // [1]

uint32_t vbvalidoven:1; // [2]

uint32_t vbvalidovval:1; // [3]

uint32_t avalidoven:1; // [4]

uint32_t avalidovval:1; // [5]

uint32_t bvalidoven:1; // [6]

uint32_t bvalidovval:1; // [7]

uint32_t hstnegscs:1; // [8]

uint32_t hnpreq:1; // [9]

uint32_t hstsethnpen:1; // [10]

uint32_t devhnpen:1; // [11]

uint32_t ehen:1; // [12]

uint32_t reserved_0:2; // [13,14]

uint32_t dbncefltrbypass:1; // [15]

uint32_t conldsts:1; // [16]

uint32_t dbnctime:1; // [17]

uint32_t asesvld:1; // [18]

uint32_t bsesvld:1; // [19]

uint32_t otgver:1; // [20]

uint32_t curmod:1; // [21]

uint32_t multvalidbc:5; // [22,26]

uint32_t chirpen:1; // [27]

uint32_t reserved_1:3; // [28,30]

uint32_t testmode_corr_eusb2:1; // [31]

} _b;

} gotgctl_u;

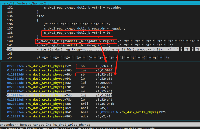

配置寄存器即配置结构体的位域

所只要按照如下方式先定义寄存器基地址

#define USB_MAC_REG_BASEADDR 0x03000000

然后定义一个指向上述结构体的指针,注意要添加volatile否则编译器会优化导致问题。

static volatile usb_otg_reg_t* g_usb_reg = (usb_otg_reg_t*)USB_MAC_REG_BASEADDR;

然后就可以通过如下形式写指定的位域,读也类似。

g_usb_reg->gotgctl._b.sesreq = 1;

如果直接访问整个寄存器则可以用g_usb_reg->gotgctl.w。

宏形式的头文件

该方式是先定义寄存器的偏移地址

#define CFG_GOTGCTL_ADDR 0x0000

然后定义位域的MASK操作值和位域的偏移值

#define TESTMODE_CORR_EUSB2_OFFSET 31

#define TESTMODE_CORR_EUSB2_MASK 0x80000000

#define CHIRPEN_OFFSET 27

#define CHIRPEN_MASK 0x08000000

#define MULTVALIDBC_OFFSET 22

#define MULTVALIDBC_MASK 0x07C00000

#define CURMOD_OFFSET 21

#define CURMOD_MASK 0x00200000

#define OTGVER_OFFSET 20

#define OTGVER_MASK 0x00100000

#define BSESVLD_OFFSET 19

#define BSESVLD_MASK 0x00080000

#define ASESVLD_OFFSET 18

#define ASESVLD_MASK 0x00040000

#define DBNCTIME_OFFSET 17

#define DBNCTIME_MASK 0x00020000

#define CONLDSTS_OFFSET 16

#define CONLDSTS_MASK 0x00010000

#define DBNCEFLTRBYPASS_OFFSET 15

#define DBNCEFLTRBYPASS_MASK 0x00008000

#define EHEN_OFFSET 12

#define EHEN_MASK 0x00001000

#define DEVHNPEN_OFFSET 11

#define DEVHNPEN_MASK 0x00000800

#define HSTSETHNPEN_OFFSET 10

#define HSTSETHNPEN_MASK 0x00000400

#define HNPREQ_OFFSET 9

#define HNPREQ_MASK 0x00000200

#define HSTNEGSCS_OFFSET 8

#define HSTNEGSCS_MASK 0x00000100

#define BVALIDOVVAL_OFFSET 7

#define BVALIDOVVAL_MASK 0x00000080

#define BVALIDOVEN_OFFSET 6

#define BVALIDOVEN_MASK 0x00000040

#define AVALIDOVVAL_OFFSET 5

#define AVALIDOVVAL_MASK 0x00000020

#define AVALIDOVEN_OFFSET 4

#define AVALIDOVEN_MASK 0x00000010

#define VBVALIDOVVAL_OFFSET 3

#define VBVALIDOVVAL_MASK 0x00000008

#define VBVALIDOVEN_OFFSET 2

#define VBVALIDOVEN_MASK 0x00000004

#define SESREQ_OFFSET 1

#define SESREQ_MASK 0x00000002

#define SESREQSCS_OFFSET 0

#define SESREQSCS_MASK 0x00000001

然后提供寄存器读写的宏

#define USB_MAC_REG_BASEADDR 0x03000000

#define SOC_READ_REG(addr) ((volatile uint32_t) * ((volatile uint32_t *)(addr)))

#define SOC_WRITE_REG(addr, value) (*((volatile uint32_t *)(addr)) = (value))

#define USB_OTG_READ_REG(addr) SOC_READ_REG(USB_MAC_REG_BASEADDR + addr)

#define USB_OTG_WRITE_REG(addr,value) SOC_WRITE_REG(USB_MAC_REG_BASEADDR + addr,value)

按照读-修改-写的操作方式

比如

uint32_t tmp = USB_OTG_READ_REG(CFG_GOTGCTL_ADDR); /* 读 */

tmp &= ~SESREQ_MASK; /* 清除需要修改的位 */

tmp |= 1 << SESREQ_OFFSET; /* 写对应的位值为1 */

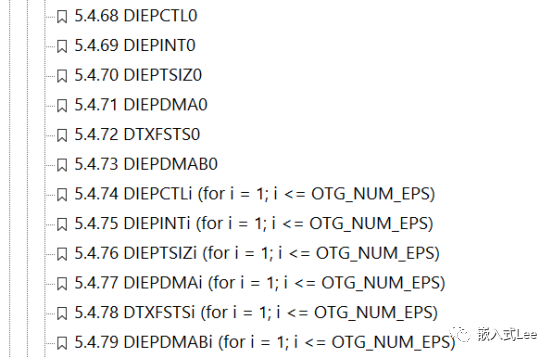

对于端点相关寄存器的处理

端点相关的寄存器内容都是一样的只是开始地址不一样

diepctl0_u diepctl0; 端点0

uint32_t reserved_11;

diepint0_u diepint0;

uint32_t reserved_12;

dieptsiz0_u dieptsiz0;

diepdma0_u diepdma0;

dtxfsts0_u dtxfsts0;

diepdmab0_u diepdmab0;

diepctl1_u diepctl1; 端点1 偏移0x20

uint32_t reserved_13[119];

可以根据端点偏移0x20得到后面端点对应的寄存器的地址。

最好是将其改为数组形式,因为端点0和后续端点有一点不一样,后续的端点单独设置为数组,通过数组索引得到端点对应的寄存器。

doepctlxxx等相关的也类似。

宏方式则直接通过端点1的地址偏移0x20得到后续寄存器地址。

总结

以上介绍了寄存器相关的头文件,这是驱动编写的第一步。保证寄存器的读写OK之后,后面就可以开始进行驱动的编写了。后面就是要不断的参考编程手册和寄存器描述。

附录 头文件

结构体

#ifndef USB_OTG_REG_H

#define USB_OTG_REG_H

#define USB_OTG_IP_VERSION 1

typedef union gotgctl_union {

uint32_t w;

struct {

uint32_t sesreqscs:1; // [0]

uint32_t sesreq:1; // [1]

uint32_t vbvalidoven:1; // [2]

uint32_t vbvalidovval:1; // [3]

uint32_t avalidoven:1; // [4]

uint32_t avalidovval:1; // [5]

uint32_t bvalidoven:1; // [6]

uint32_t bvalidovval:1; // [7]

uint32_t hstnegscs:1; // [8]

uint32_t hnpreq:1; // [9]

uint32_t hstsethnpen:1; // [10]

uint32_t devhnpen:1; // [11]

uint32_t ehen:1; // [12]

uint32_t reserved_0:2; // [13,14]

uint32_t dbncefltrbypass:1; // [15]

uint32_t conldsts:1; // [16]

uint32_t dbnctime:1; // [17]

uint32_t asesvld:1; // [18]

uint32_t bsesvld:1; // [19]

uint32_t otgver:1; // [20]

uint32_t curmod:1; // [21]

uint32_t multvalidbc:5; // [22,26]

uint32_t chirpen:1; // [27]

uint32_t reserved_1:3; // [28,30]

uint32_t testmode_corr_eusb2:1; // [31]

} _b;

} gotgctl_u;

typedef union gotgint_union {

uint32_t w;

struct {

uint32_t reserved_0:2; // [0,1]

uint32_t sesenddet:1; // [2]

uint32_t reserved_1:5; // [3,7]

uint32_t sesreqsucstschng:1; // [8]

uint32_t hstnegsucstschng:1; // [9]

uint32_t reserved_2:7; // [10,16]

uint32_t hstnegdet:1; // [17]

uint32_t adevtoutchg:1; // [18]

uint32_t dbncedone:1; // [19]

uint32_t multvalpchng:1; // [20]

uint32_t reserved_3:11; // [21,31]

} _b;

} gotgint_u;

typedef union gahbcfg_union {

uint32_t w;

struct {

uint32_t glbintrmsk:1; // [0]

uint32_t hbstlen:4; // [1,4]

uint32_t dmaen:1; // [5]

uint32_t reserved_0:1; // [6]

uint32_t nptxfemplvl:1; // [7]

uint32_t ptxfemplvl:1; // [8]

uint32_t reserved_1:12; // [9,20]

uint32_t remmemsupp:1; // [21]

uint32_t notialldmawrit:1; // [22]

uint32_t ahbsingle:1; // [23]

uint32_t invdescendianess:1; // [24]

uint32_t reserved_2:7; // [25,31]

} _b;

} gahbcfg_u;

typedef union gusbcfg_union {

uint32_t w;

struct {

uint32_t toutcal:3; // [0,2]

uint32_t phyif:1; // [3]

uint32_t ulpi_utmi_sel:1; // [4]

uint32_t fsintf:1; // [5]

uint32_t physel:1; // [6]

uint32_t ddrsel:1; // [7]

uint32_t srpcap:1; // [8]

uint32_t hnpcap:1; // [9]

uint32_t usbtrdtim:4; // [10,13]

uint32_t reserved:1; // [14]

uint32_t phylpwrclksel:1; // [15]

uint32_t otgi2csel:1; // [16]

uint32_t ulpifsls:1; // [17]

uint32_t ulpiautores:1; // [18]

uint32_t ulpiclksusm:1; // [19]

uint32_t ulpiextvbusdrv:1; // [20]

uint32_t ulpiextvbusindicator:1; // [21]

uint32_t termseldlpulse:1; // [22]

uint32_t complement:1; // [23]

uint32_t indicator:1; // [24]

uint32_t ulpi:1; // [25]

uint32_t ic_usbcap:1; // [26]

uint32_t ic_usbtrafctl:1; // [27]

uint32_t txenddelay:1; // [28]

uint32_t forcehstmode:1; // [29]

uint32_t forcedevmode:1; // [30]

uint32_t corrupttxpkt:1; // [31]

} _b;

} gusbcfg_u;

typedef union grstctl_union {

uint32_t w;

struct {

uint32_t csftrst:1; // [0]

uint32_t piufssftrst:1; // [1]

uint32_t frmcntrrst:1; // [2]

uint32_t intknqflsh:1; // [3]

uint32_t rxfflsh:1; // [4]

uint32_t txfflsh:1; // [5]

uint32_t txfnum:5; // [6,10]

uint32_t reserved:19; // [11,29]

uint32_t dmareq:1; // [30]

uint32_t ahbidle:1; // [31]

} _b;

} grstctl_u;

typedef union gintsts_union {

uint32_t w;

struct {

uint32_t curmodsts:1; // [0]

uint32_t modemis:1; // [1]

uint32_t otgint:1; // [2]

uint32_t sof:1; // [3]

uint32_t rxflvl:1; // [4]

uint32_t nptxfemp:1; // [5]

uint32_t ginnakeff:1; // [6]

uint32_t goutnakeff:1; // [7]

uint32_t ulpickint:1; // [8]

uint32_t i2cint:1; // [9]

uint32_t erlysusp:1; // [10]

uint32_t usbsusp:1; // [11]

uint32_t usbrst:1; // [12]

uint32_t enumdone:1; // [13]

uint32_t isooutdrop:1; // [14]

uint32_t eopf:1; // [15]

uint32_t rstrdoneint:1; // [16]

uint32_t epmis:1; // [17]

uint32_t iepint:1; // [18]

uint32_t oepint:1; // [19]

uint32_t incompsoin:1; // [20]

uint32_t incompip:1; // [21]

uint32_t fetsusp:1; // [22]

uint32_t resetdet:1; // [23]

uint32_t prtint:1; // [24]

uint32_t hchint:1; // [25]

uint32_t ptxfemp:1; // [26]

uint32_t lpm_int:1; // [27]

uint32_t conldstschng:1; // [28]

uint32_t disconnint:1; // [29]

uint32_t sessreqint:1; // [30]

uint32_t wkupint:1; // [31]

} _b;

} gintsts_u;

typedef union gintmsk_union {

uint32_t w;

struct {

uint32_t reserved:1; // [0]

uint32_t modemismsk:1; // [1]

uint32_t otgintmsk:1; // [2]

uint32_t sofmsk:1; // [3]

uint32_t rxflvlmsk:1; // [4]

uint32_t nptxfempmsk:1; // [5]

uint32_t ginnakeffmsk:1; // [6]

uint32_t goutnakeffmsk:1; // [7]

uint32_t ulpickintmsk:1; // [8]

uint32_t i2cintmsk:1; // [9]

uint32_t erlysuspmsk:1; // [10]

uint32_t usbsuspmsk:1; // [11]

uint32_t usbrstmsk:1; // [12]

uint32_t enumdonemsk:1; // [13]

uint32_t isooutdropmsk:1; // [14]

uint32_t eopfmsk:1; // [15]

uint32_t rstrdoneintmsk:1; // [16]

uint32_t epmismsk:1; // [17]

uint32_t iepintmsk:1; // [18]

uint32_t oepintmsk:1; // [19]

uint32_t incompsoinmsk:1; // [20]

uint32_t incompipmsk:1; // [21]

uint32_t fetsuspmsk:1; // [22]

uint32_t resetdetmsk:1; // [23]

uint32_t prtintmsk:1; // [24]

uint32_t hchintmsk:1; // [25]

uint32_t ptxfempmsk:1; // [26]

uint32_t lpm_intmsk:1; // [27]

uint32_t conldstschngmsk:1; // [28]

uint32_t disconnintmsk:1; // [29]

uint32_t sessreqintmsk:1; // [30]

uint32_t wkupintmsk:1; // [31]

} _b;

} gintmsk_u;

typedef union grxstsr_union {

uint32_t w;

struct {

uint32_t chnum:4; // [0,3]

uint32_t bcnt:11; // [4,14]

uint32_t dpid:2; // [15,16]

uint32_t pktsts:4; // [17,20]

uint32_t fn:4; // [21,24]

uint32_t reserved:7; // [25,31]

} _b;

} grxstsr_u;

typedef union grxstsp_union {

uint32_t w;

struct {

uint32_t chnum_pop:4; // [0,3]

uint32_t bcnt_pop:11; // [4,14]

uint32_t dpid_pop:2; // [15,16]

uint32_t pktsts_pop:4; // [17,20]

uint32_t fn_pop:4; // [21,24]

uint32_t reserved:7; // [25,31]

} _b;

} grxstsp_u;

typedef union grxfsiz_union {

uint32_t w;

struct {

uint32_t rxfdep:11; // [0,10]

uint32_t reserved:21; // [11,31]

} _b;

} grxfsiz_u;

typedef union gnptxfsiz_union {

uint32_t w;

struct {

uint32_t nptxfstaddr:11; // [0,10]

uint32_t reserved_0:5; // [11,15]

uint32_t nptxfdep:11; // [16,26]

uint32_t reserved_1:5; // [27,31]

} _b;

} gnptxfsiz_u;

typedef union gnptxsts_union {

uint32_t w;

struct {

uint32_t nptxfspcavail:16; // [0,15]

uint32_t nptxqspcavail:8; // [16,23]

uint32_t nptxftop:7; // [24,30]

uint32_t reserved:1; // [31]

} _b;

} gnptxsts_u;

typedef union gpvndctl_union {

uint32_t w;

struct {

uint32_t regdata:8; // [0,7]

uint32_t vctrl:8; // [8,15]

uint32_t regaddr:6; // [16,21]

uint32_t regwr:1; // [22]

uint32_t reserved_0:2; // [23,24]

uint32_t newregreq:1; // [25]

uint32_t vstsbsy:1; // [26]

uint32_t vstsdone:1; // [27]

uint32_t reserved_1:3; // [28,30]

uint32_t disulpidrv:1; // [31]

} _b;

} gpvndctl_u;

typedef union ghwcfg1_union {

uint32_t w;

struct {

uint32_t epdir:32; // [0,31]

} _b;

} ghwcfg1_u;

typedef union ghwcfg2_union {

uint32_t w;

struct {

uint32_t otgmode:3; // [0,2]

uint32_t otgarch:2; // [3,4]

uint32_t singpnt:1; // [5]

uint32_t hsphytype:2; // [6,7]

uint32_t fsphytype:2; // [8,9]

uint32_t numdeveps:4; // [10,13]

uint32_t numhstchnl:4; // [14,17]

uint32_t periosupport:1; // [18]

uint32_t dynfifosizing:1; // [19]

uint32_t multiprocintrpt:1; // [20]

uint32_t reserved:1; // [21]

uint32_t nptxqdepth:2; // [22,23]

uint32_t ptxqdepth:2; // [24,25]

uint32_t tknqdepth:5; // [26,30]

uint32_t otg_enable_ic_usb:1; // [31]

} _b;

} ghwcfg2_u;

typedef union ghwcfg3_union {

uint32_t w;

struct {

uint32_t xfersizewidth:4; // [0,3]

uint32_t pktsizewidth:3; // [4,6]

uint32_t otgen:1; // [7]

uint32_t i2cintsel:1; // [8]

uint32_t vndctlsupt:1; // [9]

uint32_t optfeature:1; // [10]

uint32_t rsttype:1; // [11]

uint32_t adpsupport:1; // [12]

uint32_t hsicmode:1; // [13]

uint32_t bcsupport:1; // [14]

uint32_t lpmmode:1; // [15]

uint32_t dfifodepth:16; // [16,31]

} _b;

} ghwcfg3_u;

typedef union ghwcfg4_union {

uint32_t w;

struct {

uint32_t numdevperioeps:4; // [0,3]

uint32_t partialpwrdn:1; // [4]

uint32_t ahbfreq:1; // [5]

uint32_t hibernation:1; // [6]

uint32_t extendedhibernation:1; // [7]

uint32_t reserved:1; // [8]

uint32_t enhancedlpmsupt1:1; // [9]

uint32_t servintflow:1; // [10]

uint32_t ipgisocsupt:1; // [11]

uint32_t acgsupt:1; // [12]

uint32_t enhancedlpmsupt:1; // [13]

uint32_t phydatawidth:2; // [14,15]

uint32_t numctleps:4; // [16,19]

uint32_t iddgfltr:1; // [20]

uint32_t vbusvalidfltr:1; // [21]

uint32_t avalidfltr:1; // [22]

uint32_t bvalidfltr:1; // [23]

uint32_t sessendfltr:1; // [24]

uint32_t dedfifomode:1; // [25]

uint32_t ineps:4; // [26,29]

uint32_t descdmaenable:1; // [30]

uint32_t descdma:1; // [31]

} _b;

} ghwcfg4_u;

typedef union gdfifocfg_union {

uint32_t w;

struct {

uint32_t gdfifocfg:16; // [0,15]

uint32_t epinfobaseaddr:16; // [16,31]

} _b;

} gdfifocfg_u;

typedef union grefclk_union {

uint32_t w;

struct {

uint32_t sof_cnt_wkup_alert:10; // [0,9]

uint32_t reserved:4; // [10,13]

uint32_t refclkmode:1; // [14]

uint32_t refclkper:17; // [15,31]

} _b;

} grefclk_u;

typedef union hptxfsiz_union {

uint32_t w;

struct {

uint32_t ptxfstaddr:12; // [0,11]

uint32_t reserved_0:4; // [12,15]

uint32_t ptxfsize:12; // [16,27]

uint32_t reserved_1:4; // [28,31]

} _b;

} hptxfsiz_u;

typedef union dieptxf1_union {

uint32_t w;

struct {

uint32_t inepntxfstaddr:11; // [0,10]

uint32_t reserved_0:5; // [11,15]

uint32_t inepntxfdep:9; // [16,24]

uint32_t reserved_1:7; // [25,31]

} _b;

} dieptxf1_u;

typedef union dcfg_union {

uint32_t w;

struct {

uint32_t devspd:2; // [0,1]

uint32_t nzstsouthshk:1; // [2]

uint32_t ena32khzsusp:1; // [3]

uint32_t devaddr:7; // [4,10]

uint32_t perfrint:2; // [11,12]

uint32_t endevoutnak:1; // [13]

uint32_t xcvrdly:1; // [14]

uint32_t erraticintmsk:1; // [15]

uint32_t reserved:1; // [16]

uint32_t ipgisocsupt_dev:1; // [17]

uint32_t epmiscnt:5; // [18,22]

uint32_t descdma_dev:1; // [23]

uint32_t perschintvl:2; // [24,25]

uint32_t resvalid:6; // [26,31]

} _b;

} dcfg_u;

typedef union dctl_union {

uint32_t w;

struct {

uint32_t rmtwkupsig:1; // [0]

uint32_t sftdiscon:1; // [1]

uint32_t gnpinnaksts:1; // [2]

uint32_t goutnaksts:1; // [3]

uint32_t tstctl:3; // [4,6]

uint32_t sgnpinnak:1; // [7]

uint32_t cgnpinnak:1; // [8]

uint32_t sgoutnak:1; // [9]

uint32_t cgoutnak:1; // [10]

uint32_t pwronprgdone:1; // [11]

uint32_t reserved_0:1; // [12]

uint32_t gmc:2; // [13,14]

uint32_t ignrfrmnum:1; // [15]

uint32_t nakonbble:1; // [16]

uint32_t encontonbna:1; // [17]

uint32_t deepsleepbeslreject:1; // [18]

uint32_t servint:1; // [19]

uint32_t reserved_1:12; // [20,31]

} _b;

} dctl_u;

typedef union dsts_union {

uint32_t w;

struct {

uint32_t suspsts:1; // [0]

uint32_t enumspd:2; // [1,2]

uint32_t errticerr:1; // [3]

uint32_t reserved_0:4; // [4,7]

uint32_t soffn:14; // [8,21]

uint32_t devlnsts:2; // [22,23]

uint32_t reserved_1:8; // [24,31]

} _b;

} dsts_u;

typedef union diepmsk_union {

uint32_t w;

struct {

uint32_t xfercomplmsk_in:1; // [0]

uint32_t epdisbldmsk_in:1; // [1]

uint32_t ahberrmsk_in:1; // [2]

uint32_t timeoutmsk:1; // [3]

uint32_t intkntxfempmsk:1; // [4]

uint32_t intknepmismsk:1; // [5]

uint32_t inepnakeffmsk:1; // [6]

uint32_t reserved_0:1; // [7]

uint32_t txfifoundrnmsk:1; // [8]

uint32_t bnainintrmsk:1; // [9]

uint32_t reserved_1:3; // [10,12]

uint32_t nakmsk:1; // [13]

uint32_t reserved_2:18; // [14,31]

} _b;

} diepmsk_u;

typedef union doepmsk_union {

uint32_t w;

struct {

uint32_t xfercomplmsk_out:1; // [0]

uint32_t epdisbldmsk_out:1; // [1]

uint32_t ahberrmsk_out:1; // [2]

uint32_t setupmsk:1; // [3]

uint32_t outtknepdismsk:1; // [4]

uint32_t stsphsercvdmsk:1; // [5]

uint32_t back2backsetup:1; // [6]

uint32_t reserved_0:1; // [7]

uint32_t outpkterrmsk:1; // [8]

uint32_t bnaoutintrmsk:1; // [9]

uint32_t reserved_1:2; // [10,11]

uint32_t bbleerrmsk:1; // [12]

uint32_t nakmsk:1; // [13]

uint32_t nyetmsk:1; // [14]

uint32_t reserved_2:17; // [15,31]

} _b;

} doepmsk_u;

typedef union daint_union {

uint32_t w;

struct {

uint32_t inepint0:1; // [0]

uint32_t inepint1:1; // [1]

uint32_t inepint2:1; // [2]

uint32_t inepint3:1; // [3]

uint32_t inepint4:1; // [4]

uint32_t inepint5:1; // [5]

uint32_t inepint6:1; // [6]

uint32_t inepint7:1; // [7]

uint32_t inepint8:1; // [8]

uint32_t inepint9:1; // [9]

uint32_t inepint10:1; // [10]

uint32_t inepint11:1; // [11]

uint32_t inepint12:1; // [12]

uint32_t inepint13:1; // [13]

uint32_t inepint14:1; // [14]

uint32_t inepint15:1; // [15]

uint32_t outepint0:1; // [16]

uint32_t outepint1:1; // [17]

uint32_t outepint2:1; // [18]

uint32_t outepint3:1; // [19]

uint32_t outepint4:1; // [20]

uint32_t outepint5:1; // [21]

uint32_t outepint6:1; // [22]

uint32_t outepint7:1; // [23]

uint32_t outepint8:1; // [24]

uint32_t outepint9:1; // [25]

uint32_t outepint10:1; // [26]

uint32_t outepint11:1; // [27]

uint32_t outepint12:1; // [28]

uint32_t outepint13:1; // [29]

uint32_t outepint14:1; // [30]

uint32_t outepint15:1; // [31]

} _b;

} daint_u;

typedef union daintmsk_union {

uint32_t w;

struct {

uint32_t inepmsk0:1; // [0]

uint32_t inepmsk1:1; // [1]

uint32_t inepmsk2:1; // [2]

uint32_t inepmsk3:1; // [3]

uint32_t inepmsk4:1; // [4]

uint32_t inepmsk5:1; // [5]

uint32_t inepmsk6:1; // [6]

uint32_t inepmsk7:1; // [7]

uint32_t inepmsk8:1; // [8]

uint32_t inepmsk9:1; // [9]

uint32_t inepmsk10:1; // [10]

uint32_t inepmsk11:1; // [11]

uint32_t inepmsk12:1; // [12]

uint32_t inepmsk13:1; // [13]

uint32_t inepmsk14:1; // [14]

uint32_t inepmsk15:1; // [15]

uint32_t outepmsk0:1; // [16]

uint32_t outepmsk1:1; // [17]

uint32_t outepmsk2:1; // [18]

uint32_t outepmsk3:1; // [19]

uint32_t outepmsk4:1; // [20]

uint32_t outepmsk5:1; // [21]

uint32_t outepmsk6:1; // [22]

uint32_t outepmsk7:1; // [23]

uint32_t outepmsk8:1; // [24]

uint32_t outepmsk9:1; // [25]

uint32_t outepmsk10:1; // [26]

uint32_t outepmsk11:1; // [27]

uint32_t outepmsk12:1; // [28]

uint32_t outepmsk13:1; // [29]

uint32_t outepmsk14:1; // [30]

uint32_t outepmsk15:1; // [31]

} _b;

} daintmsk_u;

typedef union dthrctl_union {

uint32_t w;

struct {

uint32_t nonisothren:1; // [0]

uint32_t isothren:1; // [1]

uint32_t txthrlen:9; // [2,10]

uint32_t ahbthrratio:2; // [11,12]

uint32_t reserved_0:3; // [13,15]

uint32_t rxthren:1; // [16]

uint32_t rxthrlen:9; // [17,25]

uint32_t reserved_1:1; // [26]

uint32_t arbprken:1; // [27]

uint32_t reserved_2:4; // [28,31]

} _b;

} dthrctl_u;

typedef union deachint_union {

uint32_t w;

struct {

uint32_t eachinepint0:1; // [0]

uint32_t eachinepint1:1; // [1]

uint32_t eachinepint2:1; // [2]

uint32_t eachinepint3:1; // [3]

uint32_t eachinepint4:1; // [4]

uint32_t eachinepint5:1; // [5]

uint32_t eachinepint6:1; // [6]

uint32_t eachinepint7:1; // [7]

uint32_t eachinepint8:1; // [8]

uint32_t eachinepint9:1; // [9]

uint32_t eachinepint10:1; // [10]

uint32_t eachinepint11:1; // [11]

uint32_t eachinepint12:1; // [12]

uint32_t eachinepint13:1; // [13]

uint32_t eachinepint14:1; // [14]

uint32_t eachinepint15:1; // [15]

uint32_t eachoutepint0:1; // [16]

uint32_t eachoutepint1:1; // [17]

uint32_t eachoutepint2:1; // [18]

uint32_t eachoutepint3:1; // [19]

uint32_t eachoutepint4:1; // [20]

uint32_t eachoutepint5:1; // [21]

uint32_t eachoutepint6:1; // [22]

uint32_t eachoutepint7:1; // [23]

uint32_t eachoutepint8:1; // [24]

uint32_t eachoutepint9:1; // [25]

uint32_t eachoutepint10:1; // [26]

uint32_t eachoutepint11:1; // [27]

uint32_t eachoutepint12:1; // [28]

uint32_t eachoutepint13:1; // [29]

uint32_t eachoutepint14:1; // [30]

uint32_t eachoutepint15:1; // [31]

} _b;

} deachint_u;

typedef union deachintmsk_union {

uint32_t w;

struct {

uint32_t eachinepmsk0:1; // [0]

uint32_t eachinepmsk1:1; // [1]

uint32_t eachinepmsk2:1; // [2]

uint32_t eachinepmsk3:1; // [3]

uint32_t eachinepmsk4:1; // [4]

uint32_t eachinepmsk5:1; // [5]

uint32_t eachinepmsk6:1; // [6]

uint32_t eachinepmsk7:1; // [7]

uint32_t eachinepmsk8:1; // [8]

uint32_t eachinepmsk9:1; // [9]

uint32_t eachinepmsk10:1; // [10]

uint32_t eachinepmsk11:1; // [11]

uint32_t eachinepmsk12:1; // [12]

uint32_t eachinepmsk13:1; // [13]

uint32_t eachinepmsk14:1; // [14]

uint32_t eachinepmsk15:1; // [15]

uint32_t eachoutepmsk0:1; // [16]

uint32_t eachoutepmsk1:1; // [17]

uint32_t eachoutepmsk2:1; // [18]

uint32_t eachoutepmsk3:1; // [19]

uint32_t eachoutepmsk4:1; // [20]

uint32_t eachoutepmsk5:1; // [21]

uint32_t eachoutepmsk6:1; // [22]

uint32_t eachoutepmsk7:1; // [23]

uint32_t eachoutepmsk8:1; // [24]

uint32_t eachoutepmsk9:1; // [25]

uint32_t eachoutepmsk10:1; // [26]

uint32_t eachoutepmsk11:1; // [27]

uint32_t eachoutepmsk12:1; // [28]

uint32_t eachoutepmsk13:1; // [29]

uint32_t eachoutepmsk14:1; // [30]

uint32_t eachoutepmsk15:1; // [31]

} _b;

} deachintmsk_u;

typedef union diepeachmsk0_union {

uint32_t w;

struct {

uint32_t eachin_xfercomplmsk:1; // [0]

uint32_t eachin_epdisbldmsk:1; // [1]

uint32_t eachin_ahberrmsk:1; // [2]

uint32_t eachin_timeoutmsk:1; // [3]

uint32_t eachin_intkntxfempmsk:1; // [4]

uint32_t eachin_intknepmismsk:1; // [5]

uint32_t eachin_inepnakeffmsk:1; // [6]

uint32_t reserved_0:1; // [7]

uint32_t eachin_txfifoundrnmsk:1; // [8]

uint32_t eachin_bnainintrmsk:1; // [9]

uint32_t reserved_1:3; // [10,12]

uint32_t eachin_nakmsk:1; // [13]

uint32_t reserved_2:18; // [14,31]

} _b;

} diepeachmsk0_u;

typedef union doepeachmsk0_union {

uint32_t w;

struct {

uint32_t eachout_xfercomplmsk:1; // [0]

uint32_t eachout_epdisbldmsk:1; // [1]

uint32_t eachout_ahberrmsk:1; // [2]

uint32_t eachout_setupmsk:1; // [3]

uint32_t eachout_outtknepdismsk:1; // [4]

uint32_t eachout_stsphsrcvdmsk:1; // [5]

uint32_t eachout_back2backsetup:1; // [6]

uint32_t reserved_0:1; // [7]

uint32_t eachout_outpkterrmsk:1; // [8]

uint32_t eachout_bnaoutintrmsk:1; // [9]

uint32_t reserved_1:2; // [10,11]

uint32_t eachout_bbleerrmsk:1; // [12]

uint32_t eachout_nakmsk:1; // [13]

uint32_t eachout_nyetmsk:1; // [14]

uint32_t reserved_2:17; // [15,31]

} _b;

} doepeachmsk0_u;

typedef union diepctl0_union {

uint32_t w;

struct {

uint32_t mps_in:2; // [0,1]

uint32_t reserved_0:9; // [2,10]

uint32_t nextep_in:4; // [11,14]

uint32_t usbactep_in:1; // [15]

uint32_t reserved_1:1; // [16]

uint32_t naksts_in:1; // [17]

uint32_t eptype_in:2; // [18,19]

uint32_t reserved_2:1; // [20]

uint32_t stall_in:1; // [21]

uint32_t txfnum_in:4; // [22,25]

uint32_t cnak_in:1; // [26]

uint32_t snak_in:1; // [27]

uint32_t reserved_3:2; // [28,29]

uint32_t epdis_in:1; // [30]

uint32_t epena_in:1; // [31]

} _b;

} diepctl0_u;

typedef union diepint0_union {

uint32_t w;

struct {

uint32_t xfercompl_in:1; // [0]

uint32_t epdisbld_in:1; // [1]

uint32_t ahberr_in:1; // [2]

uint32_t timeout_in:1; // [3]

uint32_t intkntxfemp_in:1; // [4]

uint32_t intknepmis_in:1; // [5]

uint32_t inepnakeff_in:1; // [6]

uint32_t txfemp_in:1; // [7]

uint32_t txfifoundrn_in:1; // [8]

uint32_t bnaintr_in:1; // [9]

uint32_t reserved_0:1; // [10]

uint32_t pktdrpsts_in:1; // [11]

uint32_t bbleerr_in:1; // [12]

uint32_t nakintrpt_in:1; // [13]

uint32_t nyetintrpt_in:1; // [14]

uint32_t reserved_1:17; // [15,31]

} _b;

} diepint0_u;

typedef union dieptsiz0_union {

uint32_t w;

struct {

uint32_t xfersize_in:7; // [0,6]

uint32_t reserved_0:12; // [7,18]

uint32_t pktcnt_in:2; // [19,20]

uint32_t reserved_1:11; // [21,31]

} _b;

} dieptsiz0_u;

typedef union diepdma0_union {

uint32_t w;

struct {

uint32_t dmaaddr0_in:32; // [0,31]

} _b;

} diepdma0_u;

typedef union dtxfsts0_union {

uint32_t w;

struct {

uint32_t ineptxfspcavail:16; // [0,15]

uint32_t reserved:16; // [16,31]

} _b;

} dtxfsts0_u;

typedef union diepdmab0_union {

uint32_t w;

struct {

uint32_t dmabuffaddr0_in:32; // [0,31]

} _b;

} diepdmab0_u;

typedef union diepctl1_union {

uint32_t w;

struct {

uint32_t mps_in1:11; // [0,10]

uint32_t nextep_in1:4; // [11,14]

uint32_t usbactep_in1:1; // [15]

uint32_t dpid_in1:1; // [16]

uint32_t naksts_in1:1; // [17]

uint32_t eptype_in1:2; // [18,19]

uint32_t reserved:1; // [20]

uint32_t stall_in1:1; // [21]

uint32_t txfnum_in1:4; // [22,25]

uint32_t cnak_in1:1; // [26]

uint32_t snak_in1:1; // [27]

uint32_t setd0pid_in1:1; // [28]

uint32_t setd1pid_in1:1; // [29]

uint32_t epdis_in1:1; // [30]

uint32_t epena_in1:1; // [31]

} _b;

} diepctl1_u;

typedef union doepctl0_union {

uint32_t w;

struct {

uint32_t mps_out:2; // [0,1]

uint32_t reserved_0:13; // [2,14]

uint32_t usbactep_out:1; // [15]

uint32_t reserved_1:1; // [16]

uint32_t naksts_out:1; // [17]

uint32_t eptype_out:2; // [18,19]

uint32_t snp_out:1; // [20]

uint32_t stall_out:1; // [21]

uint32_t reserved_2:4; // [22,25]

uint32_t cnak_out:1; // [26]

uint32_t snak_out:1; // [27]

uint32_t reserved_3:2; // [28,29]

uint32_t epdis_out:1; // [30]

uint32_t epena_out:1; // [31]

} _b;

} doepctl0_u;

typedef union doepint0_union {

uint32_t w;

struct {

uint32_t xfercompl_out:1; // [0]

uint32_t epdisbld_out:1; // [1]

uint32_t ahberr_out:1; // [2]

uint32_t setup_out:1; // [3]

uint32_t outtknepdis:1; // [4]

uint32_t stsphsercvd:1; // [5]

uint32_t back2backsetup:1; // [6]

uint32_t reserved_0:1; // [7]

uint32_t outpkterr:1; // [8]

uint32_t bnaintr_out:1; // [9]

uint32_t reserved_1:1; // [10]

uint32_t pktdrpsts_out:1; // [11]

uint32_t bbleerr_out:1; // [12]

uint32_t nakintrpt_out:1; // [13]

uint32_t nyetintrpt_out:1; // [14]

uint32_t stuppktrcvd_out:1; // [15]

uint32_t reserved_2:16; // [16,31]

} _b;

} doepint0_u;

typedef union doeptsiz0_union {

uint32_t w;

struct {

uint32_t xfersize:7; // [0,6]

uint32_t reserved_0:12; // [7,18]

uint32_t pktcnt:1; // [19]

uint32_t reserved_1:9; // [20,28]

uint32_t supcnt:2; // [29,30]

uint32_t reserved_2:1; // [31]

} _b;

} doeptsiz0_u;

typedef union doepdma0_union {

uint32_t w;

struct {

uint32_t dmaaddr0_out:32; // [0,31]

} _b;

} doepdma0_u;

typedef union doepdmab0_union {

uint32_t w;

struct {

uint32_t dmabuffaddr0_out:32; // [0,31]

} _b;

} doepdmab0_u;

typedef union doepctl1_union {

uint32_t w;

struct {

uint32_t mps_out1:11; // [0,10]

uint32_t reserved_0:4; // [11,14]

uint32_t usbactep_out1:1; // [15]

uint32_t dpid_out1:1; // [16]

uint32_t naksts_out1:1; // [17]

uint32_t eptype_out1:2; // [18,19]

uint32_t snp_out1:1; // [20]

uint32_t stall_out1:1; // [21]

uint32_t reserved_1:4; // [22,25]

uint32_t cnak_out1:1; // [26]

uint32_t snak_out1:1; // [27]

uint32_t setd0pid_out1:1; // [28]

uint32_t setd1pid_out1:1; // [29]

uint32_t epdis_out1:1; // [30]

uint32_t epena_out1:1; // [31]

} _b;

} doepctl1_u;

typedef union pcgcctl_union {

uint32_t w;

struct {

uint32_t stoppclk:1; // [0]

uint32_t gatehclk:1; // [1]

uint32_t pwrclmp:1; // [2]

uint32_t rstpdwnmodule:1; // [3]

uint32_t reserved:1; // [4]

uint32_t enbl_l1gating:1; // [5]

uint32_t physleep:1; // [6]

uint32_t l1suspended:1; // [7]

uint32_t resetaftersusp:1; // [8]

uint32_t restoremode:1; // [9]

uint32_t exthiberen:1; // [10]

uint32_t exthiberclmp:1; // [11]

uint32_t exthibersw:1; // [12]

uint32_t essregrestored:1; // [13]

uint32_t restorevalue:18; // [14,31]

} _b;

} pcgcctl_u;

typedef union pcgcctl1_union {

uint32_t w;

struct {

uint32_t gateen:1; // [0]

uint32_t cntgateclk:2; // [1,2]

uint32_t ramgateen:1; // [3]

uint32_t reserved:28; // [4,31]

} _b;

} pcgcctl1_u;

typedef struct usb_otg_reg {

gotgctl_u gotgctl;

gotgint_u gotgint;

gahbcfg_u gahbcfg;

gusbcfg_u gusbcfg;

grstctl_u grstctl;

gintsts_u gintsts;

gintmsk_u gintmsk;

grxstsr_u grxstsr;

grxstsp_u grxstsp;

grxfsiz_u grxfsiz;

gnptxfsiz_u gnptxfsiz;

gnptxsts_u gnptxsts;

uint32_t reserved_0;

gpvndctl_u gpvndctl;

uint32_t reserved_1[3];

ghwcfg1_u ghwcfg1;

ghwcfg2_u ghwcfg2;

ghwcfg3_u ghwcfg3;

ghwcfg4_u ghwcfg4;

uint32_t reserved_2[2];

gdfifocfg_u gdfifocfg;

uint32_t reserved_3;

grefclk_u grefclk;

uint32_t reserved_4[38];

hptxfsiz_u hptxfsiz;

dieptxf1_u dieptxf1;

uint32_t reserved_5[446];

dcfg_u dcfg;

dctl_u dctl;

dsts_u dsts;

uint32_t reserved_6;

diepmsk_u diepmsk;

doepmsk_u doepmsk;

daint_u daint;

daintmsk_u daintmsk;

uint32_t reserved_7[4];

dthrctl_u dthrctl;

uint32_t reserved_8;

deachint_u deachint;

deachintmsk_u deachintmsk;

diepeachmsk0_u diepeachmsk0;

uint32_t reserved_9[15];

doepeachmsk0_u doepeachmsk0;

uint32_t reserved_10[31];

diepctl0_u diepctl0;

uint32_t reserved_11;

diepint0_u diepint0;

uint32_t reserved_12;

dieptsiz0_u dieptsiz0;

diepdma0_u diepdma0;

dtxfsts0_u dtxfsts0;

diepdmab0_u diepdmab0;

diepctl1_u diepctl1;

uint32_t reserved_13[119];

doepctl0_u doepctl0;

uint32_t reserved_14;

doepint0_u doepint0;

uint32_t reserved_15;

doeptsiz0_u doeptsiz0;

doepdma0_u doepdma0;

uint32_t reserved_16;

doepdmab0_u doepdmab0;

doepctl1_u doepctl1;

uint32_t reserved_17[183];

pcgcctl_u pcgcctl;

pcgcctl1_u pcgcctl1;

} usb_otg_reg_t;

#endif

宏形式

//-----------------------------------

#define CFG_GOTGCTL_ADDR 0x0000

#define TESTMODE_CORR_EUSB2_OFFSET 31

#define TESTMODE_CORR_EUSB2_MASK 0x80000000

#define CHIRPEN_OFFSET 27

#define CHIRPEN_MASK 0x08000000

#define MULTVALIDBC_OFFSET 22

#define MULTVALIDBC_MASK 0x07C00000

#define CURMOD_OFFSET 21

#define CURMOD_MASK 0x00200000

#define OTGVER_OFFSET 20

#define OTGVER_MASK 0x00100000

#define BSESVLD_OFFSET 19

#define BSESVLD_MASK 0x00080000

#define ASESVLD_OFFSET 18

#define ASESVLD_MASK 0x00040000

#define DBNCTIME_OFFSET 17

#define DBNCTIME_MASK 0x00020000

#define CONLDSTS_OFFSET 16

#define CONLDSTS_MASK 0x00010000

#define DBNCEFLTRBYPASS_OFFSET 15

#define DBNCEFLTRBYPASS_MASK 0x00008000

#define EHEN_OFFSET 12

#define EHEN_MASK 0x00001000

#define DEVHNPEN_OFFSET 11

#define DEVHNPEN_MASK 0x00000800

#define HSTSETHNPEN_OFFSET 10

#define HSTSETHNPEN_MASK 0x00000400

#define HNPREQ_OFFSET 9

#define HNPREQ_MASK 0x00000200

#define HSTNEGSCS_OFFSET 8

#define HSTNEGSCS_MASK 0x00000100

#define BVALIDOVVAL_OFFSET 7

#define BVALIDOVVAL_MASK 0x00000080

#define BVALIDOVEN_OFFSET 6

#define BVALIDOVEN_MASK 0x00000040

#define AVALIDOVVAL_OFFSET 5

#define AVALIDOVVAL_MASK 0x00000020

#define AVALIDOVEN_OFFSET 4

#define AVALIDOVEN_MASK 0x00000010

#define VBVALIDOVVAL_OFFSET 3

#define VBVALIDOVVAL_MASK 0x00000008

#define VBVALIDOVEN_OFFSET 2

#define VBVALIDOVEN_MASK 0x00000004

#define SESREQ_OFFSET 1

#define SESREQ_MASK 0x00000002

#define SESREQSCS_OFFSET 0

#define SESREQSCS_MASK 0x00000001

//-----------------------------------

#define CFG_GOTGINT_ADDR 0x0004

#define MULTVALPCHNG_OFFSET 20

#define MULTVALPCHNG_MASK 0x00100000

#define DBNCEDONE_OFFSET 19

#define DBNCEDONE_MASK 0x00080000

#define ADEVTOUTCHG_OFFSET 18

#define ADEVTOUTCHG_MASK 0x00040000

#define HSTNEGDET_OFFSET 17

#define HSTNEGDET_MASK 0x00020000

#define HSTNEGSUCSTSCHNG_OFFSET 9

#define HSTNEGSUCSTSCHNG_MASK 0x00000200

#define SESREQSUCSTSCHNG_OFFSET 8

#define SESREQSUCSTSCHNG_MASK 0x00000100

#define SESENDDET_OFFSET 2

#define SESENDDET_MASK 0x00000004

//-----------------------------------

#define CFG_GAHBCFG_ADDR 0x0008

#define INVDESCENDIANESS_OFFSET 24

#define INVDESCENDIANESS_MASK 0x01000000

#define AHBSINGLE_OFFSET 23

#define AHBSINGLE_MASK 0x00800000

#define NOTIALLDMAWRIT_OFFSET 22

#define NOTIALLDMAWRIT_MASK 0x00400000

#define REMMEMSUPP_OFFSET 21

#define REMMEMSUPP_MASK 0x00200000

#define PTXFEMPLVL_OFFSET 8

#define PTXFEMPLVL_MASK 0x00000100

#define NPTXFEMPLVL_OFFSET 7

#define NPTXFEMPLVL_MASK 0x00000080

#define DMAEN_OFFSET 5

#define DMAEN_MASK 0x00000020

#define HBSTLEN_OFFSET 1

#define HBSTLEN_MASK 0x0000001E

#define GLBINTRMSK_OFFSET 0

#define GLBINTRMSK_MASK 0x00000001

//-----------------------------------

#define CFG_GUSBCFG_ADDR 0x000c

#define CORRUPTTXPKT_OFFSET 31

#define CORRUPTTXPKT_MASK 0x80000000

#define FORCEDEVMODE_OFFSET 30

#define FORCEDEVMODE_MASK 0x40000000

#define FORCEHSTMODE_OFFSET 29

#define FORCEHSTMODE_MASK 0x20000000

#define TXENDDELAY_OFFSET 28

#define TXENDDELAY_MASK 0x10000000

#define IC_USBTRAFCTL_OFFSET 27

#define IC_USBTRAFCTL_MASK 0x08000000

#define IC_USBCAP_OFFSET 26

#define IC_USBCAP_MASK 0x04000000

#define ULPI_OFFSET 25

#define ULPI_MASK 0x02000000

#define INDICATOR_OFFSET 24

#define INDICATOR_MASK 0x01000000

#define COMPLEMENT_OFFSET 23

#define COMPLEMENT_MASK 0x00800000

#define TERMSELDLPULSE_OFFSET 22

#define TERMSELDLPULSE_MASK 0x00400000

#define ULPIEXTVBUSINDICATOR_OFFSET 21

#define ULPIEXTVBUSINDICATOR_MASK 0x00200000

#define ULPIEXTVBUSDRV_OFFSET 20

#define ULPIEXTVBUSDRV_MASK 0x00100000

#define ULPICLKSUSM_OFFSET 19

#define ULPICLKSUSM_MASK 0x00080000

#define ULPIAUTORES_OFFSET 18

#define ULPIAUTORES_MASK 0x00040000

#define ULPIFSLS_OFFSET 17

#define ULPIFSLS_MASK 0x00020000

#define OTGI2CSEL_OFFSET 16

#define OTGI2CSEL_MASK 0x00010000

#define PHYLPWRCLKSEL_OFFSET 15

#define PHYLPWRCLKSEL_MASK 0x00008000

#define USBTRDTIM_OFFSET 10

#define USBTRDTIM_MASK 0x00003C00

#define HNPCAP_OFFSET 9

#define HNPCAP_MASK 0x00000200

#define SRPCAP_OFFSET 8

#define SRPCAP_MASK 0x00000100

#define DDRSEL_OFFSET 7

#define DDRSEL_MASK 0x00000080

#define PHYSEL_OFFSET 6

#define PHYSEL_MASK 0x00000040

#define FSINTF_OFFSET 5

#define FSINTF_MASK 0x00000020

#define ULPI_UTMI_SEL_OFFSET 4

#define ULPI_UTMI_SEL_MASK 0x00000010

#define PHYIF_OFFSET 3

#define PHYIF_MASK 0x00000008

#define TOUTCAL_OFFSET 0

#define TOUTCAL_MASK 0x00000007

//-----------------------------------

#define CFG_GRSTCTL_ADDR 0x0010

#define AHBIDLE_OFFSET 31

#define AHBIDLE_MASK 0x80000000

#define DMAREQ_OFFSET 30

#define DMAREQ_MASK 0x40000000

#define TXFNUM_OFFSET 6

#define TXFNUM_MASK 0x000007C0

#define TXFFLSH_OFFSET 5

#define TXFFLSH_MASK 0x00000020

#define RXFFLSH_OFFSET 4

#define RXFFLSH_MASK 0x00000010

#define INTKNQFLSH_OFFSET 3

#define INTKNQFLSH_MASK 0x00000008

#define FRMCNTRRST_OFFSET 2

#define FRMCNTRRST_MASK 0x00000004

#define PIUFSSFTRST_OFFSET 1

#define PIUFSSFTRST_MASK 0x00000002

#define CSFTRST_OFFSET 0

#define CSFTRST_MASK 0x00000001

//-----------------------------------

#define CFG_GINTSTS_ADDR 0x0014

#define WKUPINT_OFFSET 31

#define WKUPINT_MASK 0x80000000

#define SESSREQINT_OFFSET 30

#define SESSREQINT_MASK 0x40000000

#define DISCONNINT_OFFSET 29

#define DISCONNINT_MASK 0x20000000

#define CONLDSTSCHNG_OFFSET 28

#define CONLDSTSCHNG_MASK 0x10000000

#define LPM_INT_OFFSET 27

#define LPM_INT_MASK 0x08000000

#define PTXFEMP_OFFSET 26

#define PTXFEMP_MASK 0x04000000

#define HCHINT_OFFSET 25

#define HCHINT_MASK 0x02000000

#define PRTINT_OFFSET 24

#define PRTINT_MASK 0x01000000

#define RESETDET_OFFSET 23

#define RESETDET_MASK 0x00800000

#define FETSUSP_OFFSET 22

#define FETSUSP_MASK 0x00400000

#define INCOMPIP_OFFSET 21

#define INCOMPIP_MASK 0x00200000

#define INCOMPSOIN_OFFSET 20

#define INCOMPSOIN_MASK 0x00100000

#define OEPINT_OFFSET 19

#define OEPINT_MASK 0x00080000

#define IEPINT_OFFSET 18

#define IEPINT_MASK 0x00040000

#define EPMIS_OFFSET 17

#define EPMIS_MASK 0x00020000

#define RSTRDONEINT_OFFSET 16

#define RSTRDONEINT_MASK 0x00010000

#define EOPF_OFFSET 15

#define EOPF_MASK 0x00008000

#define ISOOUTDROP_OFFSET 14

#define ISOOUTDROP_MASK 0x00004000

#define ENUMDONE_OFFSET 13

#define ENUMDONE_MASK 0x00002000

#define USBRST_OFFSET 12

#define USBRST_MASK 0x00001000

#define USBSUSP_OFFSET 11

#define USBSUSP_MASK 0x00000800

#define ERLYSUSP_OFFSET 10

#define ERLYSUSP_MASK 0x00000400

#define I2CINT_OFFSET 9

#define I2CINT_MASK 0x00000200

#define ULPICKINT_OFFSET 8

#define ULPICKINT_MASK 0x00000100

#define GOUTNAKEFF_OFFSET 7

#define GOUTNAKEFF_MASK 0x00000080

#define GINNAKEFF_OFFSET 6

#define GINNAKEFF_MASK 0x00000040

#define NPTXFEMP_OFFSET 5

#define NPTXFEMP_MASK 0x00000020

#define RXFLVL_OFFSET 4

#define RXFLVL_MASK 0x00000010

#define SOF_OFFSET 3

#define SOF_MASK 0x00000008

#define OTGINT_OFFSET 2

#define OTGINT_MASK 0x00000004

#define MODEMIS_OFFSET 1

#define MODEMIS_MASK 0x00000002

#define CURMODSTS_OFFSET 0

#define CURMODSTS_MASK 0x00000001

//-----------------------------------

#define CFG_GINTMSK_ADDR 0x0018

#define WKUPINTMSK_OFFSET 31

#define WKUPINTMSK_MASK 0x80000000

#define SESSREQINTMSK_OFFSET 30

#define SESSREQINTMSK_MASK 0x40000000

#define DISCONNINTMSK_OFFSET 29

#define DISCONNINTMSK_MASK 0x20000000

#define CONLDSTSCHNGMSK_OFFSET 28

#define CONLDSTSCHNGMSK_MASK 0x10000000

#define LPM_INTMSK_OFFSET 27

#define LPM_INTMSK_MASK 0x08000000

#define PTXFEMPMSK_OFFSET 26

#define PTXFEMPMSK_MASK 0x04000000

#define HCHINTMSK_OFFSET 25

#define HCHINTMSK_MASK 0x02000000

#define PRTINTMSK_OFFSET 24

#define PRTINTMSK_MASK 0x01000000

#define RESETDETMSK_OFFSET 23

#define RESETDETMSK_MASK 0x00800000

#define FETSUSPMSK_OFFSET 22

#define FETSUSPMSK_MASK 0x00400000

#define INCOMPIPMSK_OFFSET 21

#define INCOMPIPMSK_MASK 0x00200000

#define INCOMPSOINMSK_OFFSET 20

#define INCOMPSOINMSK_MASK 0x00100000

#define OEPINTMSK_OFFSET 19

#define OEPINTMSK_MASK 0x00080000

#define IEPINTMSK_OFFSET 18

#define IEPINTMSK_MASK 0x00040000

#define EPMISMSK_OFFSET 17

#define EPMISMSK_MASK 0x00020000

#define RSTRDONEINTMSK_OFFSET 16

#define RSTRDONEINTMSK_MASK 0x00010000

#define EOPFMSK_OFFSET 15

#define EOPFMSK_MASK 0x00008000

#define ISOOUTDROPMSK_OFFSET 14

#define ISOOUTDROPMSK_MASK 0x00004000

#define ENUMDONEMSK_OFFSET 13

#define ENUMDONEMSK_MASK 0x00002000

#define USBRSTMSK_OFFSET 12

#define USBRSTMSK_MASK 0x00001000

#define USBSUSPMSK_OFFSET 11

#define USBSUSPMSK_MASK 0x00000800

#define ERLYSUSPMSK_OFFSET 10

#define ERLYSUSPMSK_MASK 0x00000400

#define I2CINTMSK_OFFSET 9

#define I2CINTMSK_MASK 0x00000200

#define ULPICKINTMSK_OFFSET 8

#define ULPICKINTMSK_MASK 0x00000100

#define GOUTNAKEFFMSK_OFFSET 7

#define GOUTNAKEFFMSK_MASK 0x00000080

#define GINNAKEFFMSK_OFFSET 6

#define GINNAKEFFMSK_MASK 0x00000040

#define NPTXFEMPMSK_OFFSET 5

#define NPTXFEMPMSK_MASK 0x00000020

#define RXFLVLMSK_OFFSET 4

#define RXFLVLMSK_MASK 0x00000010

#define SOFMSK_OFFSET 3

#define SOFMSK_MASK 0x00000008

#define OTGINTMSK_OFFSET 2

#define OTGINTMSK_MASK 0x00000004

#define MODEMISMSK_OFFSET 1

#define MODEMISMSK_MASK 0x00000002

//-----------------------------------

#define CFG_GRXSTSR_ADDR 0x001C

#define FN_OFFSET 21

#define FN_MASK 0x01E00000

#define PKTSTS_OFFSET 17

#define PKTSTS_MASK 0x001E0000

#define DPID_OFFSET 15

#define DPID_MASK 0x00018000

#define BCNT_OFFSET 4

#define BCNT_MASK 0x00007FF0

#define CHNUM_OFFSET 0

#define CHNUM_MASK 0x0000000F

//-----------------------------------

#define CFG_GRXSTSP_ADDR 0x0020

#define FN_POP_OFFSET 21

#define FN_POP_MASK 0x01E00000

#define PKTSTS_POP_OFFSET 17

#define PKTSTS_POP_MASK 0x001E0000

#define DPID_POP_OFFSET 15

#define DPID_POP_MASK 0x00018000

#define BCNT_POP_OFFSET 4

#define BCNT_POP_MASK 0x00007FF0

#define CHNUM_POP_OFFSET 0

#define CHNUM_POP_MASK 0x0000000F

//-----------------------------------

#define CFG_GRXFSIZ_ADDR 0x0024

#define RXFDEP_OFFSET 0

#define RXFDEP_MASK 0x000007FF

//-----------------------------------

#define CFG_GNPTXFSIZ_ADDR 0x0028

#define NPTXFDEP_OFFSET 16

#define NPTXFDEP_MASK 0x07FF0000

#define NPTXFSTADDR_OFFSET 0

#define NPTXFSTADDR_MASK 0x000007FF

//-----------------------------------

#define CFG_GNPTXSTS_ADDR 0x002c

#define NPTXFTOP_OFFSET 24

#define NPTXFTOP_MASK 0x7F000000

#define NPTXQSPCAVAIL_OFFSET 16

#define NPTXQSPCAVAIL_MASK 0x00FF0000

#define NPTXFSPCAVAIL_OFFSET 0

#define NPTXFSPCAVAIL_MASK 0x0000FFFF

//-----------------------------------

#define CFG_GPVNDCTL_ADDR 0x0034

#define DISULPIDRV_OFFSET 31

#define DISULPIDRV_MASK 0x80000000

#define VSTSDONE_OFFSET 27

#define VSTSDONE_MASK 0x08000000

#define VSTSBSY_OFFSET 26

#define VSTSBSY_MASK 0x04000000

#define NEWREGREQ_OFFSET 25

#define NEWREGREQ_MASK 0x02000000

#define REGWR_OFFSET 22

#define REGWR_MASK 0x00400000

#define REGADDR_OFFSET 16

#define REGADDR_MASK 0x003F0000

#define VCTRL_OFFSET 8

#define VCTRL_MASK 0x0000FF00

#define REGDATA_OFFSET 0

#define REGDATA_MASK 0x000000FF

//-----------------------------------

#define CFG_GHWCFG1_ADDR 0x0044

#define EPDIR_OFFSET 0

#define EPDIR_MASK 0xFFFFFFFF

//-----------------------------------

#define CFG_GHWCFG2_ADDR 0x0048

#define OTG_ENABLE_IC_USB_OFFSET 31

#define OTG_ENABLE_IC_USB_MASK 0x80000000

#define TKNQDEPTH_OFFSET 26

#define TKNQDEPTH_MASK 0x7C000000

#define PTXQDEPTH_OFFSET 24

#define PTXQDEPTH_MASK 0x03000000

#define NPTXQDEPTH_OFFSET 22

#define NPTXQDEPTH_MASK 0x00C00000

#define MULTIPROCINTRPT_OFFSET 20

#define MULTIPROCINTRPT_MASK 0x00100000

#define DYNFIFOSIZING_OFFSET 19

#define DYNFIFOSIZING_MASK 0x00080000

#define PERIOSUPPORT_OFFSET 18

#define PERIOSUPPORT_MASK 0x00040000

#define NUMHSTCHNL_OFFSET 14

#define NUMHSTCHNL_MASK 0x0003C000

#define NUMDEVEPS_OFFSET 10

#define NUMDEVEPS_MASK 0x00003C00

#define FSPHYTYPE_OFFSET 8

#define FSPHYTYPE_MASK 0x00000300

#define HSPHYTYPE_OFFSET 6

#define HSPHYTYPE_MASK 0x000000C0

#define SINGPNT_OFFSET 5

#define SINGPNT_MASK 0x00000020

#define OTGARCH_OFFSET 3

#define OTGARCH_MASK 0x00000018

#define OTGMODE_OFFSET 0

#define OTGMODE_MASK 0x00000007

//-----------------------------------

#define CFG_GHWCFG3_ADDR 0x004c

#define DFIFODEPTH_OFFSET 16

#define DFIFODEPTH_MASK 0xFFFF0000

#define LPMMODE_OFFSET 15

#define LPMMODE_MASK 0x00008000

#define BCSUPPORT_OFFSET 14

#define BCSUPPORT_MASK 0x00004000

#define HSICMODE_OFFSET 13

#define HSICMODE_MASK 0x00002000

#define ADPSUPPORT_OFFSET 12

#define ADPSUPPORT_MASK 0x00001000

#define RSTTYPE_OFFSET 11

#define RSTTYPE_MASK 0x00000800

#define OPTFEATURE_OFFSET 10

#define OPTFEATURE_MASK 0x00000400

#define VNDCTLSUPT_OFFSET 9

#define VNDCTLSUPT_MASK 0x00000200

#define I2CINTSEL_OFFSET 8

#define I2CINTSEL_MASK 0x00000100

#define OTGEN_OFFSET 7

#define OTGEN_MASK 0x00000080

#define PKTSIZEWIDTH_OFFSET 4

#define PKTSIZEWIDTH_MASK 0x00000070

#define XFERSIZEWIDTH_OFFSET 0

#define XFERSIZEWIDTH_MASK 0x0000000F

//-----------------------------------

#define CFG_GHWCFG4_ADDR 0x0050

#define DESCDMA_OFFSET 31

#define DESCDMA_MASK 0x80000000

#define DESCDMAENABLE_OFFSET 30

#define DESCDMAENABLE_MASK 0x40000000

#define INEPS_OFFSET 26

#define INEPS_MASK 0x3C000000

#define DEDFIFOMODE_OFFSET 25

#define DEDFIFOMODE_MASK 0x02000000

#define SESSENDFLTR_OFFSET 24

#define SESSENDFLTR_MASK 0x01000000

#define BVALIDFLTR_OFFSET 23

#define BVALIDFLTR_MASK 0x00800000

#define AVALIDFLTR_OFFSET 22

#define AVALIDFLTR_MASK 0x00400000

#define VBUSVALIDFLTR_OFFSET 21

#define VBUSVALIDFLTR_MASK 0x00200000

#define IDDGFLTR_OFFSET 20

#define IDDGFLTR_MASK 0x00100000

#define NUMCTLEPS_OFFSET 16

#define NUMCTLEPS_MASK 0x000F0000

#define PHYDATAWIDTH_OFFSET 14

#define PHYDATAWIDTH_MASK 0x0000C000

#define ENHANCEDLPMSUPT_OFFSET 13

#define ENHANCEDLPMSUPT_MASK 0x00002000

#define ACGSUPT_OFFSET 12

#define ACGSUPT_MASK 0x00001000

#define IPGISOCSUPT_OFFSET 11

#define IPGISOCSUPT_MASK 0x00000800

#define SERVINTFLOW_OFFSET 10

#define SERVINTFLOW_MASK 0x00000400

#define ENHANCEDLPMSUPT1_OFFSET 9

#define ENHANCEDLPMSUPT1_MASK 0x00000200

#define EXTENDEDHIBERNATION_OFFSET 7

#define EXTENDEDHIBERNATION_MASK 0x00000080

#define HIBERNATION_OFFSET 6

#define HIBERNATION_MASK 0x00000040

#define AHBFREQ_OFFSET 5

#define AHBFREQ_MASK 0x00000020

#define PARTIALPWRDN_OFFSET 4

#define PARTIALPWRDN_MASK 0x00000010

#define NUMDEVPERIOEPS_OFFSET 0

#define NUMDEVPERIOEPS_MASK 0x0000000F

//-----------------------------------

#define CFG_GDFIFOCFG_ADDR 0x005c

#define EPINFOBASEADDR_OFFSET 16

#define EPINFOBASEADDR_MASK 0xFFFF0000

#define GDFIFOCFG_OFFSET 0

#define GDFIFOCFG_MASK 0x0000FFFF

//-----------------------------------

#define CFG_GREFCLK_ADDR 0x0064

#define REFCLKPER_OFFSET 15

#define REFCLKPER_MASK 0xFFFF8000

#define REFCLKMODE_OFFSET 14

#define REFCLKMODE_MASK 0x00004000

#define SOF_CNT_WKUP_ALERT_OFFSET 0

#define SOF_CNT_WKUP_ALERT_MASK 0x000003FF

//-----------------------------------

#define CFG_HPTXFSIZ_ADDR 0x0100

#define PTXFSIZE_OFFSET 16

#define PTXFSIZE_MASK 0x0FFF0000

#define PTXFSTADDR_OFFSET 0

#define PTXFSTADDR_MASK 0x00000FFF

//-----------------------------------

#define CFG_DIEPTXF1_ADDR 0x0104

#define INEPNTXFDEP_OFFSET 16

#define INEPNTXFDEP_MASK 0x01FF0000

#define INEPNTXFSTADDR_OFFSET 0

#define INEPNTXFSTADDR_MASK 0x000007FF

//-----------------------------------

#define CFG_DCFG_ADDR 0x0800

#define RESVALID_OFFSET 26

#define RESVALID_MASK 0xFC000000

#define PERSCHINTVL_OFFSET 24

#define PERSCHINTVL_MASK 0x03000000

#define DESCDMA_DEV_OFFSET 23

#define DESCDMA_DEV_MASK 0x00800000

#define EPMISCNT_OFFSET 18

#define EPMISCNT_MASK 0x007C0000

#define IPGISOCSUPT_DEV_OFFSET 17

#define IPGISOCSUPT_DEV_MASK 0x00020000

#define ERRATICINTMSK_OFFSET 15

#define ERRATICINTMSK_MASK 0x00008000

#define XCVRDLY_OFFSET 14

#define XCVRDLY_MASK 0x00004000

#define ENDEVOUTNAK_OFFSET 13

#define ENDEVOUTNAK_MASK 0x00002000

#define PERFRINT_OFFSET 11

#define PERFRINT_MASK 0x00001800

#define DEVADDR_OFFSET 4

#define DEVADDR_MASK 0x000007F0

#define ENA32KHZSUSP_OFFSET 3

#define ENA32KHZSUSP_MASK 0x00000008

#define NZSTSOUTHSHK_OFFSET 2

#define NZSTSOUTHSHK_MASK 0x00000004

#define DEVSPD_OFFSET 0

#define DEVSPD_MASK 0x00000003

//-----------------------------------

#define CFG_DCTL_ADDR 0x0804

#define SERVINT_OFFSET 19

#define SERVINT_MASK 0x00080000

#define DEEPSLEEPBESLREJECT_OFFSET 18

#define DEEPSLEEPBESLREJECT_MASK 0x00040000

#define ENCONTONBNA_OFFSET 17

#define ENCONTONBNA_MASK 0x00020000

#define NAKONBBLE_OFFSET 16

#define NAKONBBLE_MASK 0x00010000

#define IGNRFRMNUM_OFFSET 15

#define IGNRFRMNUM_MASK 0x00008000

#define GMC_OFFSET 13

#define GMC_MASK 0x00006000

#define PWRONPRGDONE_OFFSET 11

#define PWRONPRGDONE_MASK 0x00000800

#define CGOUTNAK_OFFSET 10

#define CGOUTNAK_MASK 0x00000400

#define SGOUTNAK_OFFSET 9

#define SGOUTNAK_MASK 0x00000200

#define CGNPINNAK_OFFSET 8

#define CGNPINNAK_MASK 0x00000100

#define SGNPINNAK_OFFSET 7

#define SGNPINNAK_MASK 0x00000080

#define TSTCTL_OFFSET 4

#define TSTCTL_MASK 0x00000070

#define GOUTNAKSTS_OFFSET 3

#define GOUTNAKSTS_MASK 0x00000008

#define GNPINNAKSTS_OFFSET 2

#define GNPINNAKSTS_MASK 0x00000004

#define SFTDISCON_OFFSET 1

#define SFTDISCON_MASK 0x00000002

#define RMTWKUPSIG_OFFSET 0

#define RMTWKUPSIG_MASK 0x00000001

//-----------------------------------

#define CFG_DSTS_ADDR 0x0808

#define DEVLNSTS_OFFSET 22

#define DEVLNSTS_MASK 0x00C00000

#define SOFFN_OFFSET 8

#define SOFFN_MASK 0x003FFF00

#define ERRTICERR_OFFSET 3

#define ERRTICERR_MASK 0x00000008

#define ENUMSPD_OFFSET 1

#define ENUMSPD_MASK 0x00000006

#define SUSPSTS_OFFSET 0

#define SUSPSTS_MASK 0x00000001

//-----------------------------------

#define CFG_DIEPMSK_ADDR 0x0810

#define NAKMSK_OFFSET 13

#define NAKMSK_MASK 0x00002000

#define BNAININTRMSK_OFFSET 9

#define BNAININTRMSK_MASK 0x00000200

#define TXFIFOUNDRNMSK_OFFSET 8

#define TXFIFOUNDRNMSK_MASK 0x00000100

#define INEPNAKEFFMSK_OFFSET 6

#define INEPNAKEFFMSK_MASK 0x00000040

#define INTKNEPMISMSK_OFFSET 5

#define INTKNEPMISMSK_MASK 0x00000020

#define INTKNTXFEMPMSK_OFFSET 4

#define INTKNTXFEMPMSK_MASK 0x00000010

#define TIMEOUTMSK_OFFSET 3

#define TIMEOUTMSK_MASK 0x00000008

#define AHBERRMSK_IN_OFFSET 2

#define AHBERRMSK_IN_MASK 0x00000004

#define EPDISBLDMSK_IN_OFFSET 1

#define EPDISBLDMSK_IN_MASK 0x00000002

#define XFERCOMPLMSK_IN_OFFSET 0

#define XFERCOMPLMSK_IN_MASK 0x00000001

//-----------------------------------

#define CFG_DOEPMSK_ADDR 0x0814

#define NYETMSK_OFFSET 14

#define NYETMSK_MASK 0x00004000

#define NAKMSK_OFFSET 13

#define NAKMSK_MASK 0x00002000

#define BBLEERRMSK_OFFSET 12

#define BBLEERRMSK_MASK 0x00001000

#define BNAOUTINTRMSK_OFFSET 9

#define BNAOUTINTRMSK_MASK 0x00000200

#define OUTPKTERRMSK_OFFSET 8

#define OUTPKTERRMSK_MASK 0x00000100

#define BACK2BACKSETUP_OFFSET 6

#define BACK2BACKSETUP_MASK 0x00000040

#define STSPHSERCVDMSK_OFFSET 5

#define STSPHSERCVDMSK_MASK 0x00000020

#define OUTTKNEPDISMSK_OFFSET 4

#define OUTTKNEPDISMSK_MASK 0x00000010

#define SETUPMSK_OFFSET 3

#define SETUPMSK_MASK 0x00000008

#define AHBERRMSK_OUT_OFFSET 2

#define AHBERRMSK_OUT_MASK 0x00000004

#define EPDISBLDMSK_OUT_OFFSET 1

#define EPDISBLDMSK_OUT_MASK 0x00000002

#define XFERCOMPLMSK_OUT_OFFSET 0

#define XFERCOMPLMSK_OUT_MASK 0x00000001

//-----------------------------------

#define CFG_DAINT_ADDR 0x0818

#define OUTEPINT15_OFFSET 31

#define OUTEPINT15_MASK 0x80000000

#define OUTEPINT14_OFFSET 30

#define OUTEPINT14_MASK 0x40000000

#define OUTEPINT13_OFFSET 29

#define OUTEPINT13_MASK 0x20000000

#define OUTEPINT12_OFFSET 28

#define OUTEPINT12_MASK 0x10000000

#define OUTEPINT11_OFFSET 27

#define OUTEPINT11_MASK 0x08000000

#define OUTEPINT10_OFFSET 26

#define OUTEPINT10_MASK 0x04000000

#define OUTEPINT9_OFFSET 25

#define OUTEPINT9_MASK 0x02000000

#define OUTEPINT8_OFFSET 24

#define OUTEPINT8_MASK 0x01000000

#define OUTEPINT7_OFFSET 23

#define OUTEPINT7_MASK 0x00800000

#define OUTEPINT6_OFFSET 22

#define OUTEPINT6_MASK 0x00400000

#define OUTEPINT5_OFFSET 21

#define OUTEPINT5_MASK 0x00200000

#define OUTEPINT4_OFFSET 20

#define OUTEPINT4_MASK 0x00100000

#define OUTEPINT3_OFFSET 19

#define OUTEPINT3_MASK 0x00080000

#define OUTEPINT2_OFFSET 18

#define OUTEPINT2_MASK 0x00040000

#define OUTEPINT1_OFFSET 17

#define OUTEPINT1_MASK 0x00020000

#define OUTEPINT0_OFFSET 16

#define OUTEPINT0_MASK 0x00010000

#define INEPINT15_OFFSET 15

#define INEPINT15_MASK 0x00008000

#define INEPINT14_OFFSET 14

#define INEPINT14_MASK 0x00004000

#define INEPINT13_OFFSET 13

#define INEPINT13_MASK 0x00002000

#define INEPINT12_OFFSET 12

#define INEPINT12_MASK 0x00001000

#define INEPINT11_OFFSET 11

#define INEPINT11_MASK 0x00000800

#define INEPINT10_OFFSET 10

#define INEPINT10_MASK 0x00000400

#define INEPINT9_OFFSET 9

#define INEPINT9_MASK 0x00000200

#define INEPINT8_OFFSET 8

#define INEPINT8_MASK 0x00000100

#define INEPINT7_OFFSET 7

#define INEPINT7_MASK 0x00000080

#define INEPINT6_OFFSET 6

#define INEPINT6_MASK 0x00000040

#define INEPINT5_OFFSET 5

#define INEPINT5_MASK 0x00000020

#define INEPINT4_OFFSET 4

#define INEPINT4_MASK 0x00000010

#define INEPINT3_OFFSET 3

#define INEPINT3_MASK 0x00000008

#define INEPINT2_OFFSET 2

#define INEPINT2_MASK 0x00000004

#define INEPINT1_OFFSET 1

#define INEPINT1_MASK 0x00000002

#define INEPINT0_OFFSET 0

#define INEPINT0_MASK 0x00000001

//-----------------------------------

#define CFG_DAINTMSK_ADDR 0x081c

#define OUTEPMSK15_OFFSET 31

#define OUTEPMSK15_MASK 0x80000000

#define OUTEPMSK14_OFFSET 30

#define OUTEPMSK14_MASK 0x40000000

#define OUTEPMSK13_OFFSET 29

#define OUTEPMSK13_MASK 0x20000000

#define OUTEPMSK12_OFFSET 28

#define OUTEPMSK12_MASK 0x10000000

#define OUTEPMSK11_OFFSET 27

#define OUTEPMSK11_MASK 0x08000000

#define OUTEPMSK10_OFFSET 26

#define OUTEPMSK10_MASK 0x04000000

#define OUTEPMSK9_OFFSET 25

#define OUTEPMSK9_MASK 0x02000000

#define OUTEPMSK8_OFFSET 24

#define OUTEPMSK8_MASK 0x01000000

#define OUTEPMSK7_OFFSET 23

#define OUTEPMSK7_MASK 0x00800000

#define OUTEPMSK6_OFFSET 22

#define OUTEPMSK6_MASK 0x00400000

#define OUTEPMSK5_OFFSET 21

#define OUTEPMSK5_MASK 0x00200000

#define OUTEPMSK4_OFFSET 20

#define OUTEPMSK4_MASK 0x00100000

#define OUTEPMSK3_OFFSET 19

#define OUTEPMSK3_MASK 0x00080000

#define OUTEPMSK2_OFFSET 18

#define OUTEPMSK2_MASK 0x00040000

#define OUTEPMSK1_OFFSET 17

#define OUTEPMSK1_MASK 0x00020000

#define OUTEPMSK0_OFFSET 16

#define OUTEPMSK0_MASK 0x00010000

#define INEPMSK15_OFFSET 15

#define INEPMSK15_MASK 0x00008000

#define INEPMSK14_OFFSET 14

#define INEPMSK14_MASK 0x00004000

#define INEPMSK13_OFFSET 13

#define INEPMSK13_MASK 0x00002000

#define INEPMSK12_OFFSET 12

#define INEPMSK12_MASK 0x00001000

#define INEPMSK11_OFFSET 11

#define INEPMSK11_MASK 0x00000800

#define INEPMSK10_OFFSET 10

#define INEPMSK10_MASK 0x00000400

#define INEPMSK9_OFFSET 9

#define INEPMSK9_MASK 0x00000200

#define INEPMSK8_OFFSET 8

#define INEPMSK8_MASK 0x00000100

#define INEPMSK7_OFFSET 7

#define INEPMSK7_MASK 0x00000080

#define INEPMSK6_OFFSET 6

#define INEPMSK6_MASK 0x00000040

#define INEPMSK5_OFFSET 5

#define INEPMSK5_MASK 0x00000020

#define INEPMSK4_OFFSET 4

#define INEPMSK4_MASK 0x00000010

#define INEPMSK3_OFFSET 3

#define INEPMSK3_MASK 0x00000008

#define INEPMSK2_OFFSET 2

#define INEPMSK2_MASK 0x00000004

#define INEPMSK1_OFFSET 1

#define INEPMSK1_MASK 0x00000002

#define INEPMSK0_OFFSET 0

#define INEPMSK0_MASK 0x00000001

//-----------------------------------

#define CFG_DTHRCTL_ADDR 0x0830

#define ARBPRKEN_OFFSET 27

#define ARBPRKEN_MASK 0x08000000

#define RXTHRLEN_OFFSET 17

#define RXTHRLEN_MASK 0x03FE0000

#define RXTHREN_OFFSET 16

#define RXTHREN_MASK 0x00010000

#define AHBTHRRATIO_OFFSET 11

#define AHBTHRRATIO_MASK 0x00001800

#define TXTHRLEN_OFFSET 2

#define TXTHRLEN_MASK 0x000007FC

#define ISOTHREN_OFFSET 1

#define ISOTHREN_MASK 0x00000002

#define NONISOTHREN_OFFSET 0

#define NONISOTHREN_MASK 0x00000001

//-----------------------------------

#define CFG_DEACHINT_ADDR 0x0838

#define EACHOUTEPINT15_OFFSET 31

#define EACHOUTEPINT15_MASK 0x80000000

#define EACHOUTEPINT14_OFFSET 30

#define EACHOUTEPINT14_MASK 0x40000000

#define EACHOUTEPINT13_OFFSET 29

#define EACHOUTEPINT13_MASK 0x20000000

#define EACHOUTEPINT12_OFFSET 28

#define EACHOUTEPINT12_MASK 0x10000000

#define EACHOUTEPINT11_OFFSET 27

#define EACHOUTEPINT11_MASK 0x08000000

#define EACHOUTEPINT10_OFFSET 26

#define EACHOUTEPINT10_MASK 0x04000000

#define EACHOUTEPINT9_OFFSET 25

#define EACHOUTEPINT9_MASK 0x02000000

#define EACHOUTEPINT8_OFFSET 24

#define EACHOUTEPINT8_MASK 0x01000000

#define EACHOUTEPINT7_OFFSET 23

#define EACHOUTEPINT7_MASK 0x00800000

#define EACHOUTEPINT6_OFFSET 22

#define EACHOUTEPINT6_MASK 0x00400000

#define EACHOUTEPINT5_OFFSET 21

#define EACHOUTEPINT5_MASK 0x00200000

#define EACHOUTEPINT4_OFFSET 20

#define EACHOUTEPINT4_MASK 0x00100000

#define EACHOUTEPINT3_OFFSET 19

#define EACHOUTEPINT3_MASK 0x00080000

#define EACHOUTEPINT2_OFFSET 18

#define EACHOUTEPINT2_MASK 0x00040000

#define EACHOUTEPINT1_OFFSET 17

#define EACHOUTEPINT1_MASK 0x00020000

#define EACHOUTEPINT0_OFFSET 16

#define EACHOUTEPINT0_MASK 0x00010000

#define EACHINEPINT15_OFFSET 15

#define EACHINEPINT15_MASK 0x00008000

#define EACHINEPINT14_OFFSET 14

#define EACHINEPINT14_MASK 0x00004000

#define EACHINEPINT13_OFFSET 13

#define EACHINEPINT13_MASK 0x00002000

#define EACHINEPINT12_OFFSET 12

#define EACHINEPINT12_MASK 0x00001000

#define EACHINEPINT11_OFFSET 11

#define EACHINEPINT11_MASK 0x00000800

#define EACHINEPINT10_OFFSET 10

#define EACHINEPINT10_MASK 0x00000400

#define EACHINEPINT9_OFFSET 9

#define EACHINEPINT9_MASK 0x00000200

#define EACHINEPINT8_OFFSET 8

#define EACHINEPINT8_MASK 0x00000100

#define EACHINEPINT7_OFFSET 7

#define EACHINEPINT7_MASK 0x00000080

#define EACHINEPINT6_OFFSET 6

#define EACHINEPINT6_MASK 0x00000040

#define EACHINEPINT5_OFFSET 5

#define EACHINEPINT5_MASK 0x00000020

#define EACHINEPINT4_OFFSET 4

#define EACHINEPINT4_MASK 0x00000010

#define EACHINEPINT3_OFFSET 3

#define EACHINEPINT3_MASK 0x00000008

#define EACHINEPINT2_OFFSET 2

#define EACHINEPINT2_MASK 0x00000004

#define EACHINEPINT1_OFFSET 1

#define EACHINEPINT1_MASK 0x00000002

#define EACHINEPINT0_OFFSET 0

#define EACHINEPINT0_MASK 0x00000001

//-----------------------------------

#define CFG_DEACHINTMSK_ADDR 0x083c

#define EACHOUTEPMSK15_OFFSET 31

#define EACHOUTEPMSK15_MASK 0x80000000

#define EACHOUTEPMSK14_OFFSET 30

#define EACHOUTEPMSK14_MASK 0x40000000

#define EACHOUTEPMSK13_OFFSET 29

#define EACHOUTEPMSK13_MASK 0x20000000

#define EACHOUTEPMSK12_OFFSET 28

#define EACHOUTEPMSK12_MASK 0x10000000

#define EACHOUTEPMSK11_OFFSET 27

#define EACHOUTEPMSK11_MASK 0x08000000

#define EACHOUTEPMSK10_OFFSET 26

#define EACHOUTEPMSK10_MASK 0x04000000

#define EACHOUTEPMSK9_OFFSET 25

#define EACHOUTEPMSK9_MASK 0x02000000

#define EACHOUTEPMSK8_OFFSET 24

#define EACHOUTEPMSK8_MASK 0x01000000

#define EACHOUTEPMSK7_OFFSET 23

#define EACHOUTEPMSK7_MASK 0x00800000

#define EACHOUTEPMSK6_OFFSET 22

#define EACHOUTEPMSK6_MASK 0x00400000

#define EACHOUTEPMSK5_OFFSET 21

#define EACHOUTEPMSK5_MASK 0x00200000

#define EACHOUTEPMSK4_OFFSET 20

#define EACHOUTEPMSK4_MASK 0x00100000

#define EACHOUTEPMSK3_OFFSET 19

#define EACHOUTEPMSK3_MASK 0x00080000

#define EACHOUTEPMSK2_OFFSET 18

#define EACHOUTEPMSK2_MASK 0x00040000

#define EACHOUTEPMSK1_OFFSET 17

#define EACHOUTEPMSK1_MASK 0x00020000

#define EACHOUTEPMSK0_OFFSET 16

#define EACHOUTEPMSK0_MASK 0x00010000

#define EACHINEPMSK15_OFFSET 15

#define EACHINEPMSK15_MASK 0x00008000

#define EACHINEPMSK14_OFFSET 14

#define EACHINEPMSK14_MASK 0x00004000

#define EACHINEPMSK13_OFFSET 13

#define EACHINEPMSK13_MASK 0x00002000

#define EACHINEPMSK12_OFFSET 12

#define EACHINEPMSK12_MASK 0x00001000

#define EACHINEPMSK11_OFFSET 11

#define EACHINEPMSK11_MASK 0x00000800

#define EACHINEPMSK10_OFFSET 10

#define EACHINEPMSK10_MASK 0x00000400

#define EACHINEPMSK9_OFFSET 9

#define EACHINEPMSK9_MASK 0x00000200

#define EACHINEPMSK8_OFFSET 8

#define EACHINEPMSK8_MASK 0x00000100

#define EACHINEPMSK7_OFFSET 7

#define EACHINEPMSK7_MASK 0x00000080

#define EACHINEPMSK6_OFFSET 6

#define EACHINEPMSK6_MASK 0x00000040

#define EACHINEPMSK5_OFFSET 5

#define EACHINEPMSK5_MASK 0x00000020

#define EACHINEPMSK4_OFFSET 4

#define EACHINEPMSK4_MASK 0x00000010

#define EACHINEPMSK3_OFFSET 3

#define EACHINEPMSK3_MASK 0x00000008

#define EACHINEPMSK2_OFFSET 2

#define EACHINEPMSK2_MASK 0x00000004

#define EACHINEPMSK1_OFFSET 1

#define EACHINEPMSK1_MASK 0x00000002

#define EACHINEPMSK0_OFFSET 0

#define EACHINEPMSK0_MASK 0x00000001

//-----------------------------------

#define CFG_DIEPEACHMSK0_ADDR 0x0840

#define EACHIN_NAKMSK_OFFSET 13

#define EACHIN_NAKMSK_MASK 0x00002000

#define EACHIN_BNAININTRMSK_OFFSET 9

#define EACHIN_BNAININTRMSK_MASK 0x00000200

#define EACHIN_TXFIFOUNDRNMSK_OFFSET 8

#define EACHIN_TXFIFOUNDRNMSK_MASK 0x00000100

#define EACHIN_INEPNAKEFFMSK_OFFSET 6

#define EACHIN_INEPNAKEFFMSK_MASK 0x00000040

#define EACHIN_INTKNEPMISMSK_OFFSET 5

#define EACHIN_INTKNEPMISMSK_MASK 0x00000020

#define EACHIN_INTKNTXFEMPMSK_OFFSET 4

#define EACHIN_INTKNTXFEMPMSK_MASK 0x00000010

#define EACHIN_TIMEOUTMSK_OFFSET 3

#define EACHIN_TIMEOUTMSK_MASK 0x00000008

#define EACHIN_AHBERRMSK_OFFSET 2

#define EACHIN_AHBERRMSK_MASK 0x00000004

#define EACHIN_EPDISBLDMSK_OFFSET 1

#define EACHIN_EPDISBLDMSK_MASK 0x00000002

#define EACHIN_XFERCOMPLMSK_OFFSET 0

#define EACHIN_XFERCOMPLMSK_MASK 0x00000001

//-----------------------------------

#define CFG_DOEPEACHMSK0_ADDR 0x0880

#define EACHOUT_NYETMSK_OFFSET 14

#define EACHOUT_NYETMSK_MASK 0x00004000

#define EACHOUT_NAKMSK_OFFSET 13

#define EACHOUT_NAKMSK_MASK 0x00002000

#define EACHOUT_BBLEERRMSK_OFFSET 12

#define EACHOUT_BBLEERRMSK_MASK 0x00001000

#define EACHOUT_BNAOUTINTRMSK_OFFSET 9

#define EACHOUT_BNAOUTINTRMSK_MASK 0x00000200

#define EACHOUT_OUTPKTERRMSK_OFFSET 8

#define EACHOUT_OUTPKTERRMSK_MASK 0x00000100

#define EACHOUT_BACK2BACKSETUP_OFFSET 6

#define EACHOUT_BACK2BACKSETUP_MASK 0x00000040

#define EACHOUT_STSPHSRCVDMSK_OFFSET 5

#define EACHOUT_STSPHSRCVDMSK_MASK 0x00000020

#define EACHOUT_OUTTKNEPDISMSK_OFFSET 4

#define EACHOUT_OUTTKNEPDISMSK_MASK 0x00000010

#define EACHOUT_SETUPMSK_OFFSET 3

#define EACHOUT_SETUPMSK_MASK 0x00000008

#define EACHOUT_AHBERRMSK_OFFSET 2

#define EACHOUT_AHBERRMSK_MASK 0x00000004

#define EACHOUT_EPDISBLDMSK_OFFSET 1

#define EACHOUT_EPDISBLDMSK_MASK 0x00000002

#define EACHOUT_XFERCOMPLMSK_OFFSET 0

#define EACHOUT_XFERCOMPLMSK_MASK 0x00000001

//-----------------------------------

#define CFG_DIEPCTL0_ADDR 0x0900

#define EPENA_IN_OFFSET 31

#define EPENA_IN_MASK 0x80000000

#define EPDIS_IN_OFFSET 30

#define EPDIS_IN_MASK 0x40000000

#define SNAK_IN_OFFSET 27

#define SNAK_IN_MASK 0x08000000

#define CNAK_IN_OFFSET 26

#define CNAK_IN_MASK 0x04000000

#define TXFNUM_IN_OFFSET 22

#define TXFNUM_IN_MASK 0x03C00000

#define STALL_IN_OFFSET 21

#define STALL_IN_MASK 0x00200000

#define EPTYPE_IN_OFFSET 18

#define EPTYPE_IN_MASK 0x000C0000

#define NAKSTS_IN_OFFSET 17

#define NAKSTS_IN_MASK 0x00020000

#define USBACTEP_IN_OFFSET 15

#define USBACTEP_IN_MASK 0x00008000

#define NEXTEP_IN_OFFSET 11

#define NEXTEP_IN_MASK 0x00007800

#define MPS_IN_OFFSET 0

#define MPS_IN_MASK 0x00000003

//-----------------------------------

#define CFG_DIEPINT0_ADDR 0x0908

#define NYETINTRPT_IN_OFFSET 14

#define NYETINTRPT_IN_MASK 0x00004000

#define NAKINTRPT_IN_OFFSET 13

#define NAKINTRPT_IN_MASK 0x00002000

#define BBLEERR_IN_OFFSET 12

#define BBLEERR_IN_MASK 0x00001000

#define PKTDRPSTS_IN_OFFSET 11

#define PKTDRPSTS_IN_MASK 0x00000800

#define BNAINTR_IN_OFFSET 9

#define BNAINTR_IN_MASK 0x00000200

#define TXFIFOUNDRN_IN_OFFSET 8

#define TXFIFOUNDRN_IN_MASK 0x00000100

#define TXFEMP_IN_OFFSET 7

#define TXFEMP_IN_MASK 0x00000080

#define INEPNAKEFF_IN_OFFSET 6

#define INEPNAKEFF_IN_MASK 0x00000040

#define INTKNEPMIS_IN_OFFSET 5

#define INTKNEPMIS_IN_MASK 0x00000020

#define INTKNTXFEMP_IN_OFFSET 4

#define INTKNTXFEMP_IN_MASK 0x00000010

#define TIMEOUT_IN_OFFSET 3

#define TIMEOUT_IN_MASK 0x00000008

#define AHBERR_IN_OFFSET 2

#define AHBERR_IN_MASK 0x00000004

#define EPDISBLD_IN_OFFSET 1

#define EPDISBLD_IN_MASK 0x00000002

#define XFERCOMPL_IN_OFFSET 0

#define XFERCOMPL_IN_MASK 0x00000001

//-----------------------------------

#define CFG_DIEPTSIZ0_ADDR 0x0910

#define PKTCNT_IN_OFFSET 19

#define PKTCNT_IN_MASK 0x00180000

#define XFERSIZE_IN_OFFSET 0

#define XFERSIZE_IN_MASK 0x0000007F

//-----------------------------------

#define CFG_DIEPDMA0_ADDR 0x0914

#define DMAADDR0_IN_OFFSET 0

#define DMAADDR0_IN_MASK 0xFFFFFFFF

//-----------------------------------

#define CFG_DTXFSTS0_ADDR 0x0918

#define INEPTXFSPCAVAIL_OFFSET 0

#define INEPTXFSPCAVAIL_MASK 0x0000FFFF

//-----------------------------------

#define CFG_DIEPDMAB0_ADDR 0x091c

#define DMABUFFADDR0_IN_OFFSET 0

#define DMABUFFADDR0_IN_MASK 0xFFFFFFFF

//-----------------------------------

#define CFG_DIEPCTL1_ADDR 0x0920

#define EPENA_IN1_OFFSET 31

#define EPENA_IN1_MASK 0x80000000

#define EPDIS_IN1_OFFSET 30

#define EPDIS_IN1_MASK 0x40000000

#define SETD1PID_IN1_OFFSET 29

#define SETD1PID_IN1_MASK 0x20000000

#define SETD0PID_IN1_OFFSET 28

#define SETD0PID_IN1_MASK 0x10000000

#define SNAK_IN1_OFFSET 27

#define SNAK_IN1_MASK 0x08000000

#define CNAK_IN1_OFFSET 26

#define CNAK_IN1_MASK 0x04000000

#define TXFNUM_IN1_OFFSET 22

#define TXFNUM_IN1_MASK 0x03C00000

#define STALL_IN1_OFFSET 21

#define STALL_IN1_MASK 0x00200000

#define EPTYPE_IN1_OFFSET 18

#define EPTYPE_IN1_MASK 0x000C0000

#define NAKSTS_IN1_OFFSET 17

#define NAKSTS_IN1_MASK 0x00020000

#define DPID_IN1_OFFSET 16

#define DPID_IN1_MASK 0x00010000

#define USBACTEP_IN1_OFFSET 15

#define USBACTEP_IN1_MASK 0x00008000

#define NEXTEP_IN1_OFFSET 11

#define NEXTEP_IN1_MASK 0x00007800

#define MPS_IN1_OFFSET 0

#define MPS_IN1_MASK 0x000007FF

//-----------------------------------

#define CFG_DOEPCTL0_ADDR 0x0B00

#define EPENA_OUT_OFFSET 31

#define EPENA_OUT_MASK 0x80000000

#define EPDIS_OUT_OFFSET 30

#define EPDIS_OUT_MASK 0x40000000

#define SNAK_OUT_OFFSET 27

#define SNAK_OUT_MASK 0x08000000

#define CNAK_OUT_OFFSET 26

#define CNAK_OUT_MASK 0x04000000

#define STALL_OUT_OFFSET 21

#define STALL_OUT_MASK 0x00200000

#define SNP_OUT_OFFSET 20

#define SNP_OUT_MASK 0x00100000

#define EPTYPE_OUT_OFFSET 18

#define EPTYPE_OUT_MASK 0x000C0000

#define NAKSTS_OUT_OFFSET 17

#define NAKSTS_OUT_MASK 0x00020000

#define USBACTEP_OUT_OFFSET 15

#define USBACTEP_OUT_MASK 0x00008000

#define MPS_OUT_OFFSET 0

#define MPS_OUT_MASK 0x00000003

//-----------------------------------

#define CFG_DOEPINT0_ADDR 0x0B08

#define STUPPKTRCVD_OUT_OFFSET 15

#define STUPPKTRCVD_OUT_MASK 0x00008000

#define NYETINTRPT_OUT_OFFSET 14

#define NYETINTRPT_OUT_MASK 0x00004000

#define NAKINTRPT_OUT_OFFSET 13

#define NAKINTRPT_OUT_MASK 0x00002000

#define BBLEERR_OUT_OFFSET 12

#define BBLEERR_OUT_MASK 0x00001000

#define PKTDRPSTS_OUT_OFFSET 11

#define PKTDRPSTS_OUT_MASK 0x00000800

#define BNAINTR_OUT_OFFSET 9

#define BNAINTR_OUT_MASK 0x00000200

#define OUTPKTERR_OFFSET 8

#define OUTPKTERR_MASK 0x00000100

#define BACK2BACKSETUP_OFFSET 6

#define BACK2BACKSETUP_MASK 0x00000040

#define STSPHSERCVD_OFFSET 5

#define STSPHSERCVD_MASK 0x00000020

#define OUTTKNEPDIS_OFFSET 4

#define OUTTKNEPDIS_MASK 0x00000010

#define SETUP_OUT_OFFSET 3

#define SETUP_OUT_MASK 0x00000008

#define AHBERR_OUT_OFFSET 2

#define AHBERR_OUT_MASK 0x00000004

#define EPDISBLD_OUT_OFFSET 1

#define EPDISBLD_OUT_MASK 0x00000002

#define XFERCOMPL_OUT_OFFSET 0

#define XFERCOMPL_OUT_MASK 0x00000001

//-----------------------------------

#define CFG_DOEPTSIZ0_ADDR 0x0B10

#define SUPCNT_OFFSET 29

#define SUPCNT_MASK 0x60000000

#define PKTCNT_OFFSET 19

#define PKTCNT_MASK 0x00080000

#define XFERSIZE_OFFSET 0

#define XFERSIZE_MASK 0x0000007F

//-----------------------------------

#define CFG_DOEPDMA0_ADDR 0x0B14

#define DMAADDR0_OUT_OFFSET 0

#define DMAADDR0_OUT_MASK 0xFFFFFFFF

//-----------------------------------

#define CFG_DOEPDMAB0_ADDR 0x0B1c

#define DMABUFFADDR0_OUT_OFFSET 0

#define DMABUFFADDR0_OUT_MASK 0xFFFFFFFF

//-----------------------------------

#define CFG_DOEPCTL1_ADDR 0x0B20

#define EPENA_OUT1_OFFSET 31

#define EPENA_OUT1_MASK 0x80000000

#define EPDIS_OUT1_OFFSET 30

#define EPDIS_OUT1_MASK 0x40000000

#define SETD1PID_OUT1_OFFSET 29

#define SETD1PID_OUT1_MASK 0x20000000

#define SETD0PID_OUT1_OFFSET 28

#define SETD0PID_OUT1_MASK 0x10000000

#define SNAK_OUT1_OFFSET 27

#define SNAK_OUT1_MASK 0x08000000

#define CNAK_OUT1_OFFSET 26

#define CNAK_OUT1_MASK 0x04000000