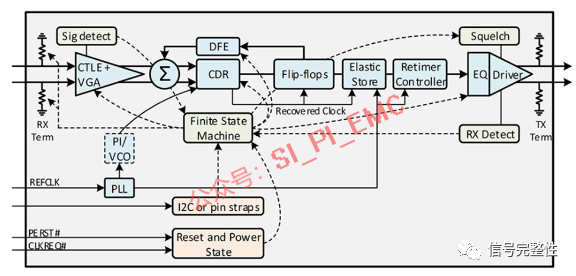

下面是Retimer的结构框图,其中包含了均衡、CDR等模块。

从框图中可以看到Retimer就类似于一颗PHY芯片,信号在经过Retimer的之后,通过内部均衡之后再通过CDR重构信号,使信号传输能力增加,再进行下一阶段的传递。所以信号经过了Retimer之后,降低了信号的抖动、恢复了驱动力能力,这样就传递的更远。以达到更好的信号完整性。但是,复杂的ReTimer会增加更多的潜伏时间。对于一些低传输延时的系统,要慎重使用。

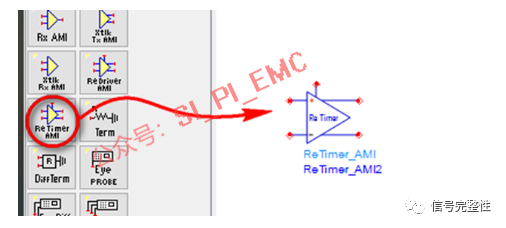

下面我们来看看如何在ADS中添加Retimer进行仿真分析。在ADS中有一个专门的Retimer模型元件ReTimer_AMI,如下图所示:

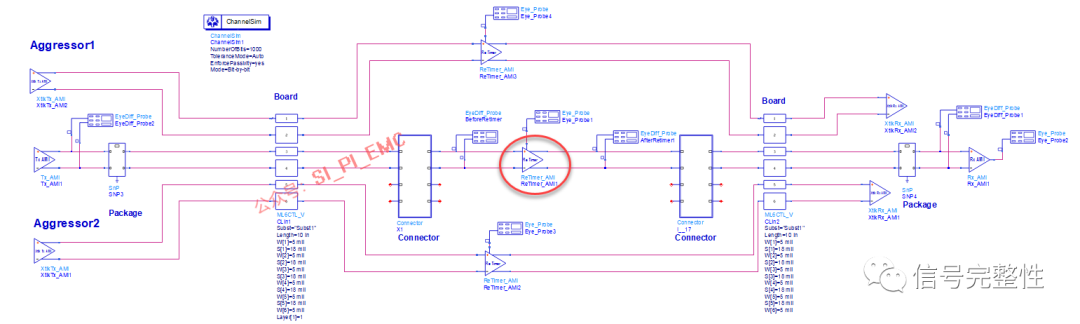

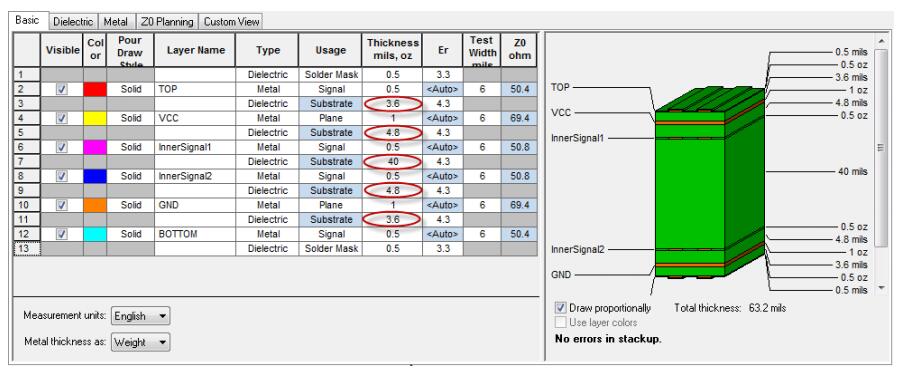

本文以PCIe3.0的仿真为例,由于在PCIe3.0的通道中损耗比较大,且有串扰的影响,所以导致信号不能满足信号完整性的要求,所以在链路中间添加了Retimer。建立带有Retimer元件的仿真原理图如下图所示(红色圈中为Retimer模型),在Retimer前后分别放置了两个Eye_Probe。

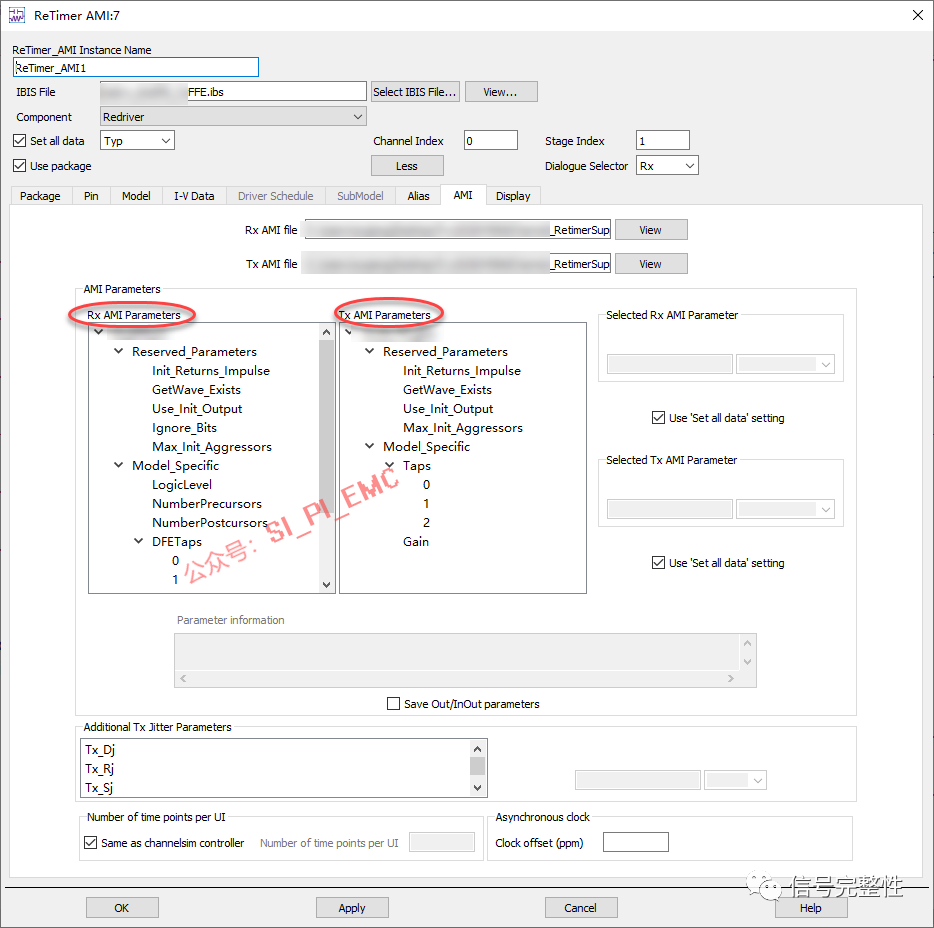

双击ReTimer_AMI导入Retimer的IBIS-AMI模型。在设置Retimer模型时,需要配置好AMI模型,如下图所示:

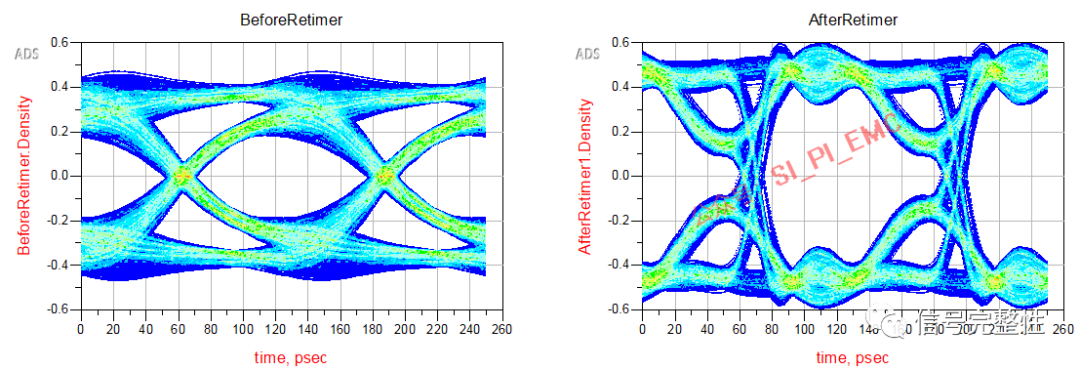

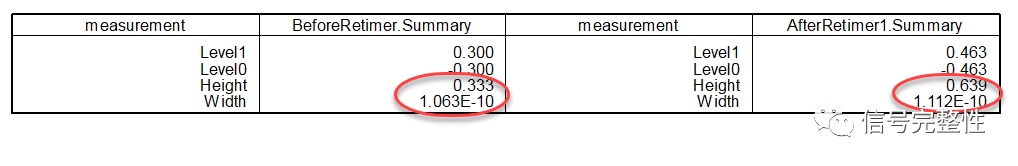

仿真后,分别观察Retimer前后的眼图,眼图如下图所示:

分别读取眼图的眼高和眼宽,如下图所示:

从结果上可以看到,在Retimer前后的眼图差异非常大,眼高和眼宽都改善了很多。

审核编辑:刘清

-

信号完整性

+关注

关注

68文章

1473浏览量

97765 -

PHY

+关注

关注

2文章

331浏览量

53787 -

cdr

+关注

关注

1文章

53浏览量

18602 -

Retimer

+关注

关注

2文章

10浏览量

8096

原文标题:如何在ADS中使用Retimer

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

信号完整性仿真应用

信号完整性与电源完整性的仿真分析与设计

如何在考虑信号完整性的情况下进行高速的PCB设计

如何在通道中添加Retimer进行信号完整性仿真分析?

如何在通道中添加Retimer进行信号完整性仿真分析?

评论