在整车电源管理中,IC 需要将多轨降压、升压和 LDO 稳压功能与每个电轨的参数,以及与其他电轨间交互的复杂可配置能力整合在一起。对于智驾系统设计人员而言,都需要清楚,稳定、准确、高效的直流 (DC) 供电轨是实现系统可靠、一致运行的必要条件。通常由 DC/DC 开关稳压器(转换器)和低压降稳压器 (LDO) 组合提供各种电压,每一个稳压器都与其所支持电轨的特定电压、电流、精度、噪声、瞬态响应以及其他需求相匹配。

前文对智驾系统的整个电源设计进行了详细说明,但是考虑到电源设计在实际应用中还需要充分考虑这个电源管理的状态设计,以及从状态设计中衍生出的功能安全设计。首先,整个电源管理的状态是需要根据对应用芯片的供电能力进行适配的;其次,在电源适配过程中,还需要在防错、纠呆上做出合理的设计。因此,本文将接续前文对电源管理设计中的功能安全和状态机进行详细说明。

电源管理模块中的功能安全设计

通常情况,对于电源管理的整个模块而言,其功能安全设计等级一般需要达到ASIL-B以上。这一过程需要充分考虑到电源管理模块(主要是PMIC、LDO等)是如何进行电源输出流分配、过压监测、低压预警以及电压供给模块失效后的处理策略等。

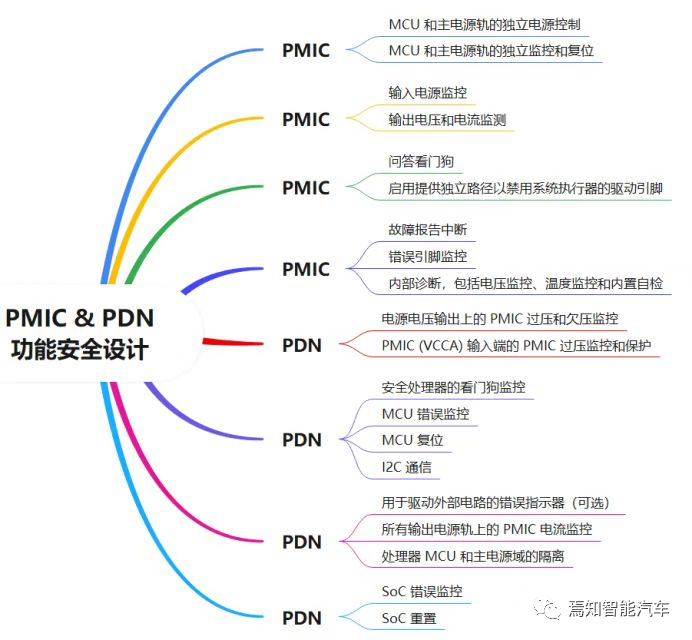

如下表示了PMIC在智驾系统架构设计的要素说明,以及对应的电源分布式网络设计能力要求。

PMIC 内部过压和欠压监控及其各自的监控阈值水平是默认启用的,整车启动后可通过 I2C 更新。PMIC 电源轨直接连接到默认状态下的监视处理器,而不是直接监控通过负载开关供电的轨道。在为处理器的MCU I/O 供电的负载开关输出电压时,建议将POK 监视器内置于处理器的 VDDSHV0_MCU 电压域中来使用。TPS65941212-Q1 中未使用的反馈引脚 BUCK3 的FB_B3可用于监控外部降压稳压器。用于监控为主 I/O 供电的负载开关电压,TPS65941111-Q1中另一个未使用的反馈的引脚(FB_B3 或 FB_B4)可通过 I2C 配置并连接到负载开关来启用监控模块。

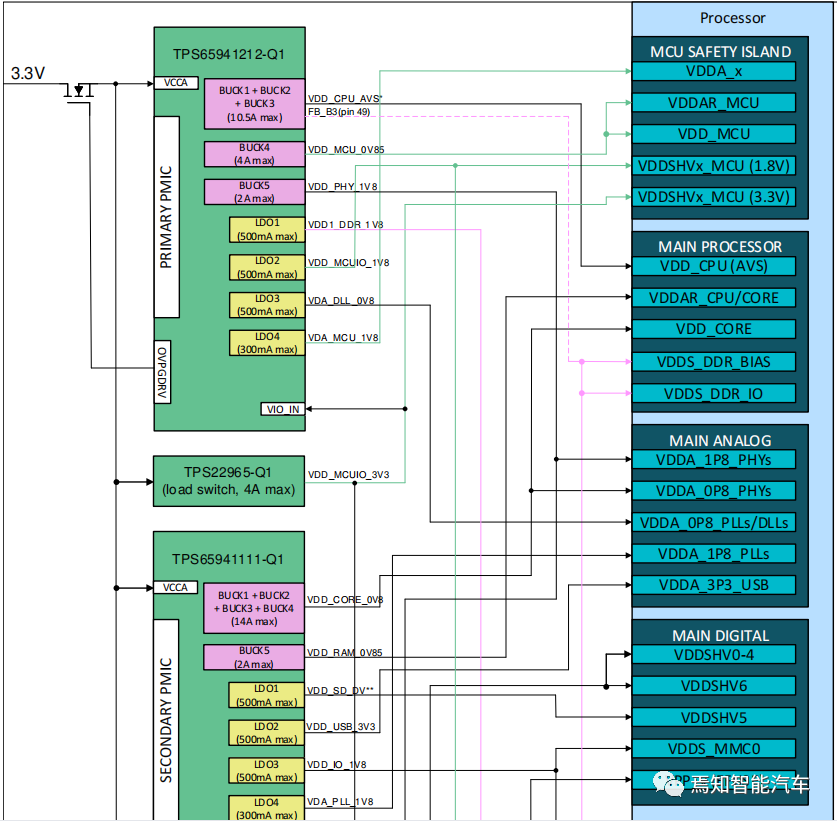

如下图,还是以双PMIC电源管理模块举例。PDN 在输入电源和 PMIC 之间有一个串联的外部功率模块FET。FET前后的电压由PMIC监控,PMIC通过OVPGDRV管脚控制FET。前文所示的MCU 和主 I/O 域供电的负载开关、DDR 供电的分立式降压以及为 EFUSE 供电的分立式 LDO 都连接在 FET 之后,这样可以延长对这些处理器域和分立电源过电压保护的能力。当在输入电源上检测到大于6V 的过压这一事件时,连接外部处理器的端口FET 可以将其串联的设备与PMIC进行快速隔离,以便保护包括来自FET输出的所有电源轨系统免受损坏。当然,在FET上游连接的任何电源也都不受过压事件的保护。

PMIC 内部过压和欠压监控及其各自的监控阈值水平是默认启用的,并且可在启动后通过 I2C 更新相应的监控阈值。默认情况下,该监控控制是直接连接到处理器的 PMIC 电源轨上的,且可不直接通过负载开关供电的轨道来做监控。同时,整个I2C控制线可以为处理器的MCU I/O 供电的负载开关输出电压,一个未使用的反馈TPS65941111-Q1 的引脚(FB_B3 或 FB_B4)可通过 I2C 配置并连接到负载开关来启用整个监控。建议使用供电源FB_B3来监控外部降压稳压器LDO,也可用于为主 I/O 供电的负载开关电压做监控。

内部看门狗在主 TPS6594-Q1 设备上是默认启用的。一旦设备处于活动状态,就可以通过设备中的辅助 I2C 配置触发器或 Q&A 设置看门狗。默认情况下可以不启用主从I2C CRC,但必须采用 I2C_2 触发器来启用PMIC芯片。一旦启用,从片I2C 将被直接禁用 2ms,因为启用 I2C CRC 通常需要等待至少 2ms,然后再启动 Q&A 看门狗。如果在初始开发期间需要暂停看门狗功能或系统不需要此功能,则将主 TPS6594-Q1 的GPIO_8 上的取消设置 DISABLE_WDOG 信号设置为高电平,即可禁用看门狗定时器。

主TPS6594-Q1的PMIC 中的GPIO_7端口被配置为 MCU错误信号监视器,且必须启用通过 ESM_MCU_EN 寄存器位。MCU复位是通过初级DCDC之间的连接来支持PMIC nRSTOUT 引脚和处理器的 MCU_PORz。最后,在两个 I2C 端口之间设置了TPS6594-Q1 和处理器。第一个用于所有非看门狗通信,例如电压电平控制;第二个允许看门狗在独立的通信通道上进行有效监控。

最后,为了达到安全的电源状态状态SAFE,预设置状态机PFSM需要自动跳转到可进行安全自修复SAFE_RECOVERY的硬件有限状态机中。在技术校验过程中,从SAFE_RECOVERY 状态开始,计数器会恢复递增并与恢复计数阈值进行比较。如果达到恢复计数阈值,则 PMIC 会停止恢复尝试并需要重启电源。

关于电源分配和管理的有限状态机分配

数字信号的连接允许系统功能,包括MCU Only下仅使用 MCU 安全岛和挂起至 RAM 低功耗模式,功能安全性高达 ASIL-D,兼容双电压 SD 卡操作和LPDDR4x 集成。处理器和 PMIC 器件之间需要有相应的数字控制信号映射。对于两个PMIC设备一起工作时,主 PMIC 和辅助 PMIC 必须建立 SPMI 通信渠道。这允许两个 TPS6594-Q1 同步其内部预配置状态机(PFSM)以便它们作为一个 PFSM 在所有电源和数字资源中运行,TPS6594-Q1上的GPIO_5 和 GPIO_6 引脚分配可以用于此功能。此外,主 PMIC LDOVINT 引脚需要连接到二次 PMIC ENABLE 输入就可以正确启动该预置的有限状态机 PFSM。

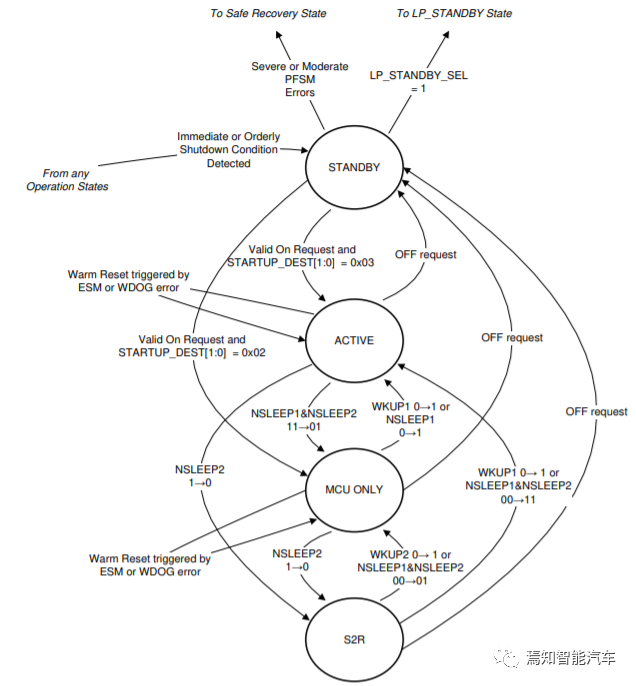

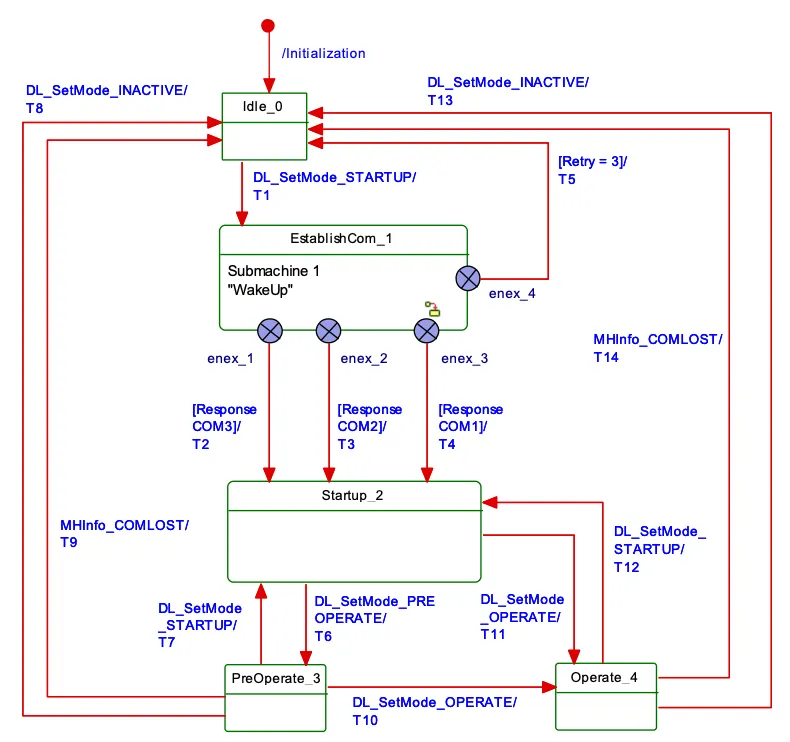

在下图中,显示了已配置的 PDN 电源状态,以及在两者之间移动的转换条件。此外,还显示了到硬件状态的转换,例如 SAFE RECOVERY 和 LP_STANDBY(Low Power Standby),硬件状态是固定设备电源有限状态机 (FSM) 的一部分。

当 PMIC 从 FSM 转换到 PFSM 时,会执行多个初始化指令。比如禁用看门狗(BUCK)功能,以及对LDO 稳压器上的剩余电压进行检查,然后设置 FIRST_STARTUP_DONE 位。执行这些指令后,PMIC 在进入 ACTIVE 状态之前等待有效的 ON 触发请求(SU_ACTIVE 触发器)。

在电源配置网络PDN 中,PMIC 设备具有四种配置的电源状态。主要包含以下基础的状态设置外,在电源管理模块中还设置了如何从其他硬件状态中跳转到对应的PMIC主状态中。

每个电源状态的定义如下所述。

• Standby(待机):

此时电源管理系统PMIC 由系统电源轨 (VCCA > VCCA_UV) 上的有效电源供电,所有设备资源都在 STANDBY 状态下断电。EN_DRV 在此状态下被强制置位为低电平,处理器处于关闭状态,没有电压域通电。可以选择使用主TPS6594-Q1 EN_DRV引脚来指示已检测到错误,确保系统正在进入SAFE状态。如果系统具有一些需要由错误事件驱动的附加外部电路,则可以利用该信号。

任何其他运行状态均可以通过立即或间歇性的关闭条件(OFF Request)进入Standby状态。而如果出现严重或者中等错误时,电源管理系统将从Standby状态跳到安全回收状态和低功耗的待机状态LP_Standby。

• Active(激活):

在激活状态下,PMIC可以直接对相应的ECU进行有源供电。此状态下PMIC 功能最为齐全,可为所有分布式电源网络中的节点负载供电。此时,各处理器已按照推荐的上电顺序完成对应模块的上电操作。从智驾系统看,其对应所有的电压域在MCU和主处理器SOC部分均已通电。

激活期间可能出现由于ESM故障或看门狗故障导致的热重启,该重启过程不会改变整个电源管理控制状态,热重启后仍然保持在Active状态。

如果该激活状态下接收到外部发送得请求进入轻睡眠指令后,系统将跳转至MCU Only状态,该状态下系统只启动对应的MCU模块来进行相应的指令运算。

• MCU Only(仅MCU模式):

MCU Only模式是狭义上针对诸如TDA4这一类超异构芯片所单独开发的低功耗模式,顾名思义,在该模式下,智驾系统中央域控只启动MCU模块进行相应的运算控制。广义上,纯异构芯片架构组成的智驾域控系统也存在MCU Only模式。只是相对于超异构芯片这种模式的架构来说,纯异构芯片架构在电源控制这一块上,相对更加简单可控。因为各个芯片本身的构造在电源树上就是完全解耦的。

当然,从供电逻辑上讲,整个MCU Only模块也需要电源管理模块PMIC 直接进行有源供电。此时,分配给处理器 MCU Only工作模块的导轨电源资源将被动开启。

此外,MCU ONLY 模式的另一种特殊情况是由于SOC电源错误而进入该状态。在这种情况下,PMIC 无法转换到活动状态或其他状态,直到处理器有意将 PMIC专门用于 MCU ONLY 状态控制。在触发TO_MCU 这一启动时序并“重新进入”MCU ONLY 状态后,PMIC 可以转换回 ACTIVE 状态。

对于MCU Only模式下,仍然可以在ESM故障或看门狗故障导致的热重启后保持在MCU Only状态。同时,MCU Only 状态也可以被重新唤醒进入到正常激活状态Active。

• Suspend-to-RAM (悬置存储):

这种状态是专门考虑到智驾系统在很多情况下只在对运算的中间数据和结果数据进行存储的过程中的情况。这种情况更多的是系统挂起后进入简单的读写操作,占用的系统资源也主要是逻辑CPU运算资源。此阶段也要求PMIC 直接进行有源供电,只有3个SoC的三个存储电压域保持通电即可,而所有其他域都关闭以最大限度地降低系统总功耗。EN_DRV 在此状态下强制为低电平。

悬置存储状态可以在用户重新触发激活指令(即WKUP 0—>1)时,将重新控制电源输入从而进入正常的电源供电状态。

PMIC有限状态机转化条件说明

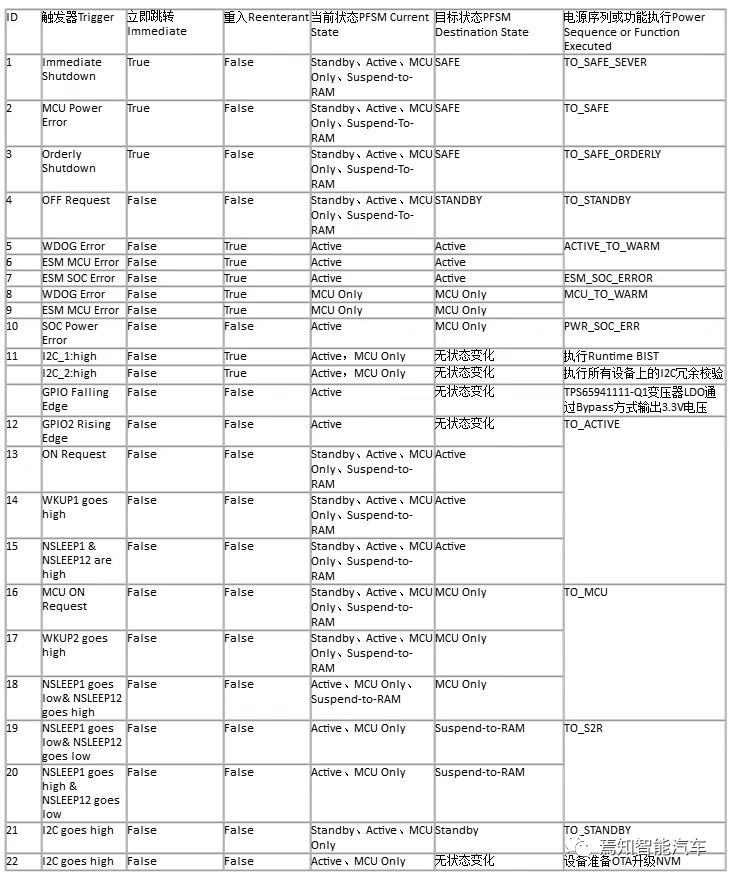

如下表描述了每个触发器说明,其从最高优先级(立即关断)的相关状态转换到最低优先级、的整个跳转过程。同时,还表示了较高优先级的活动触发器到较低优先级的块触发器的触发顺序。

这里需要注意的是如果设置了 LP_STANDBY_SEL 位,则 PFSM 转换为 LP_STANDBY 的硬件 FSM 状态。当 LP_STANDBY 作为输入时,需要使用适当的机制来唤醒外围设备。I2C_0、I2C_1、I2C_2 和 I2C_3 是自清除触发器。启用I2C CRC,同时启用I2C1和I2C2 上的 CRC,但是,启用 CRC 后 I2C2 被禁用 2ms。

对于设置电源管理的有限状态机而言,有多种触发器可以启用已配置状态之间的状态转换。主PMIC的NSLEEP1和NSLEEP2两种进入轻睡眠的指令是通过GPIO引脚或寄存器Register位来进行有效访问的。如果寄存器位或GPIO引脚被拉高,则NSLEEP x值将被读取为逻辑高电平。OTA更新完成后,需要重启PMIC 整个状态机才能应用新的网络报文管理 NVM 设置。

实际上PMIC(TPS6594-Q1)器件电源管理模块是由固定寄存器和从NVM加载的可配置寄存器组成。对于所有NVM 寄存器,需要提供加载到寄存器中的初始NVM 设置,但是,这些初始 NVM 设置可以在状态转换期间更改,例如从STANDBY 模式移动到 ACTIVE 模式时,寄存器映射会从固定寄存器的默认值跳转到其他状态值。在 TPS6594-Q1 数据表中,有七种基于应用的配置可供每个 BUCK 在其中运行。七种配置还具有最佳输出电感值,可在这些不同条件下优化每个降压器的性能。

写在最后

本文从智驾系统电源管理设计的角度详细分析了整个系统的电源设计方式。通过实例阐述主要分为几个主要的部分:智驾系统架构电源管理Profile、智能驾驶系统基础电源树设计、基于实例的电源网络管理、电源管理模块中的功能安全设计、电源分配和管理的有限状态机分配。以上几个电源设计方面都是围绕智驾系统架构而言,在充分考虑了使用端SOC、MCU的连接方式以及需求电压值。本文主要介绍了PMIC的电源管理设计方法,为满足当今智驾系统更复杂的需求,PMIC 还必须加大其输出范围,提升其原始 DC 性能,改进其附加功能,并提高用户定义的灵活性。此外,它们必须将这些增强与更高级别的功能集成整合在一起,以减少电源管理功能的总占用面积,从而确保所设计的智驾域控不会超出更大的体积范围。

审核编辑:刘清

-

转换器

+关注

关注

27文章

9365浏览量

155124 -

电源管理

+关注

关注

117文章

6548浏览量

147536 -

PMIC

+关注

关注

15文章

446浏览量

112847 -

LDO稳压器

+关注

关注

0文章

172浏览量

17731 -

状态机

+关注

关注

2文章

497浏览量

28851

原文标题:智驾系统的设计瓶颈之:电源管理设计中的功能安全和状态机

文章出处:【微信号:阿宝1990,微信公众号:阿宝1990】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

睿远研究院丨IO-Link规范解读(十一):ISDU状态机与EVENT事件

什么是状态机?

嵌入式开发为何经常用到状态机架构

睿远研究院丨IO-Link规范解读(六):主从站状态机解析

对电源管理设计中的功能安全和状态机进行详细说明

对电源管理设计中的功能安全和状态机进行详细说明

评论