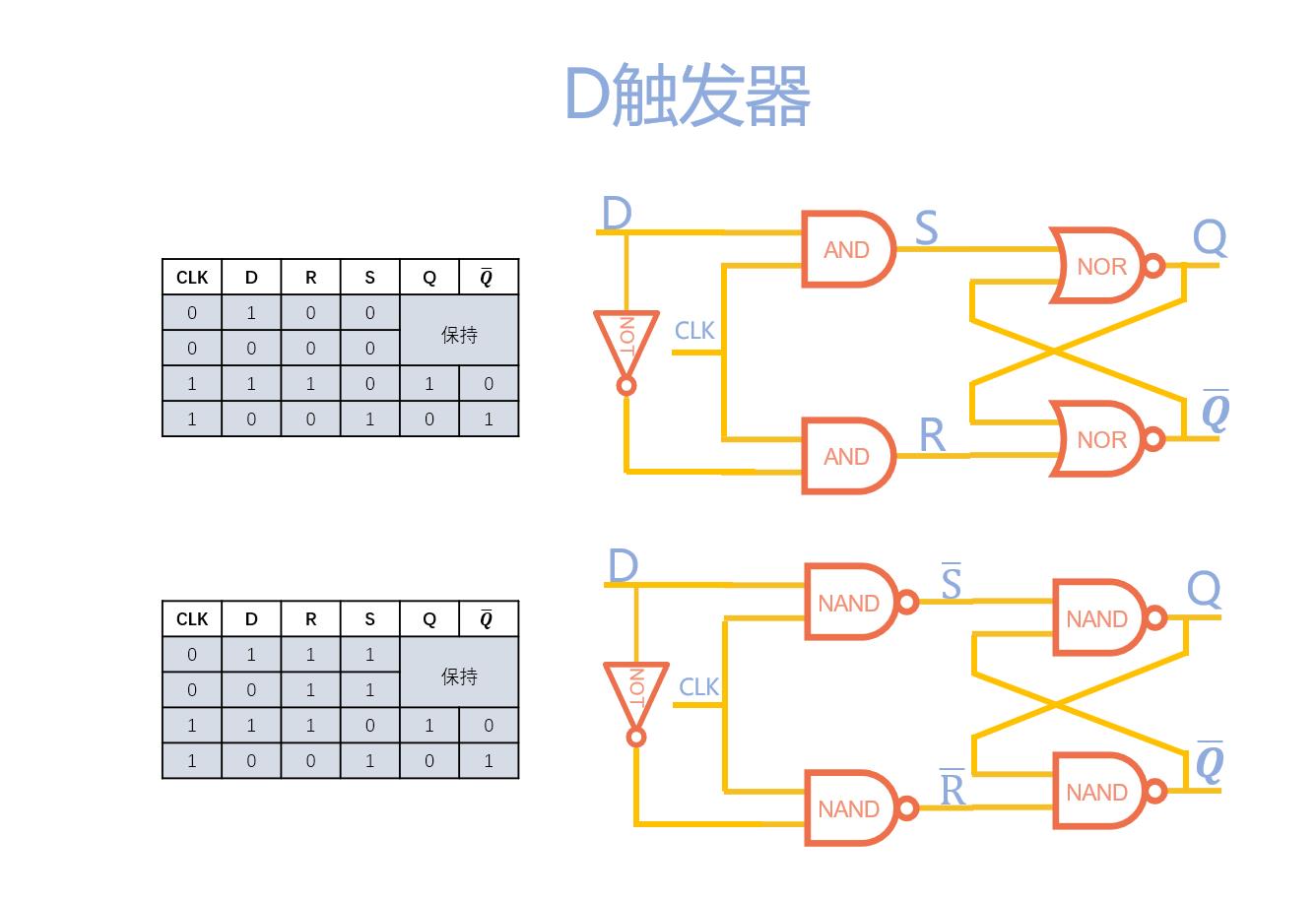

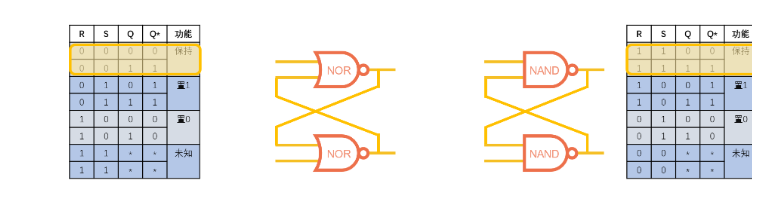

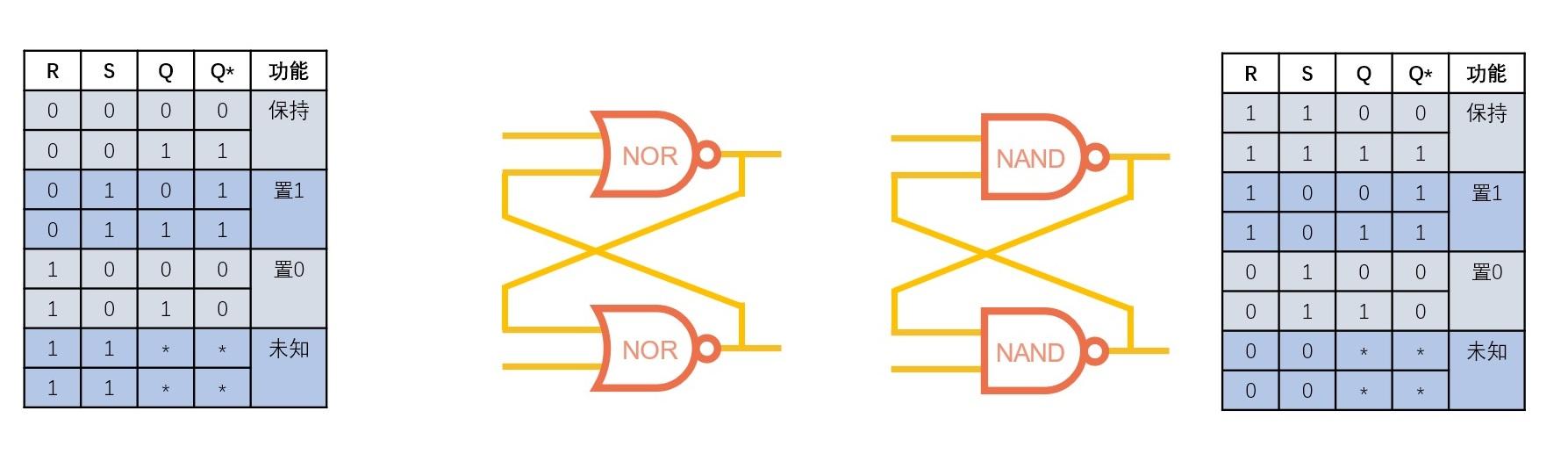

大家好,上次我们研究了D触发器,今天我们继续研究。在开始之前,先来做一点删减,之前我们讨论了用或非门或者与非门实现触发器的方法,在功能上两种实现方法完全相同,在输入输出和实现上略微有些差异。

D触发器

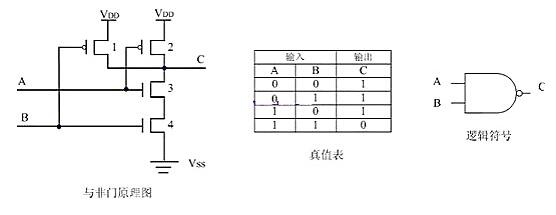

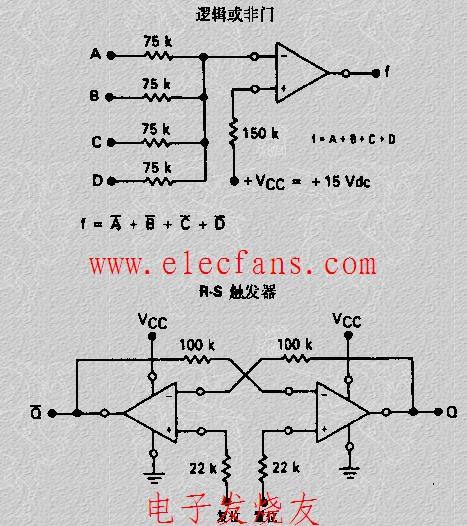

二输入与非门或或非门用CMOS电路实现需要2个NMOS和2个PMOS,总共4个MOS管,用NMOS电路实现需要2个NMOS。

而二输入与门用CMOS电路实现需要3个NMOS和3个PMOS,总共6个MOS管,用NMOS电路实现需要3个NMOS。

这样一套下来,选择与非门电路,可以只使用一种逻辑门,电路实现更加一致,还可以减少MOS管使用的数量。

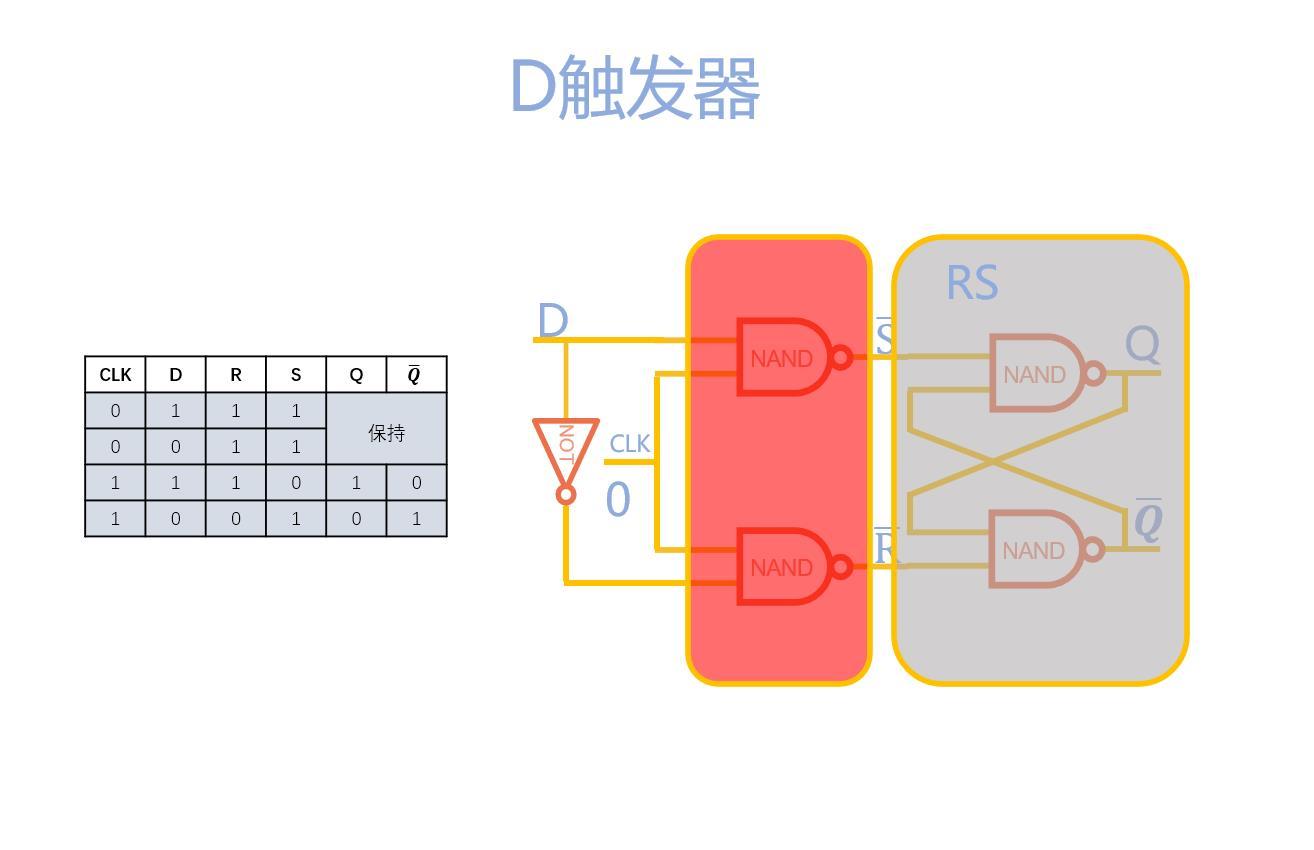

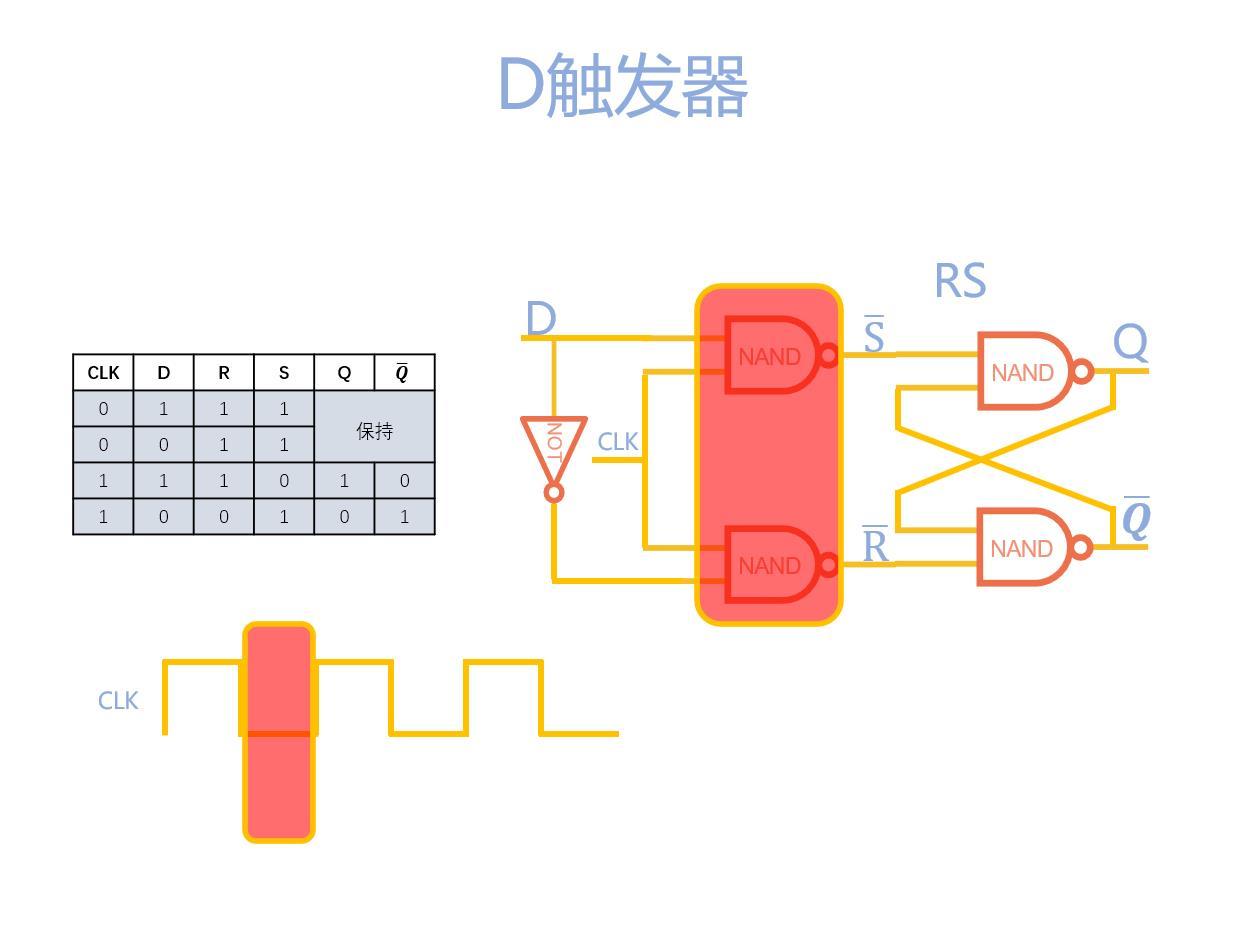

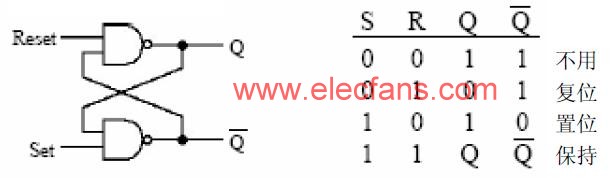

现在我们来看这个触发器和他的真值表

我们可以看到,当CLK控制信号输入为0时,D的信号是无法通过两个(与非门)组成的屏障,因此屏障之后的RS触发器的状态不会发生改变

输入信号D就被忽视掉了。

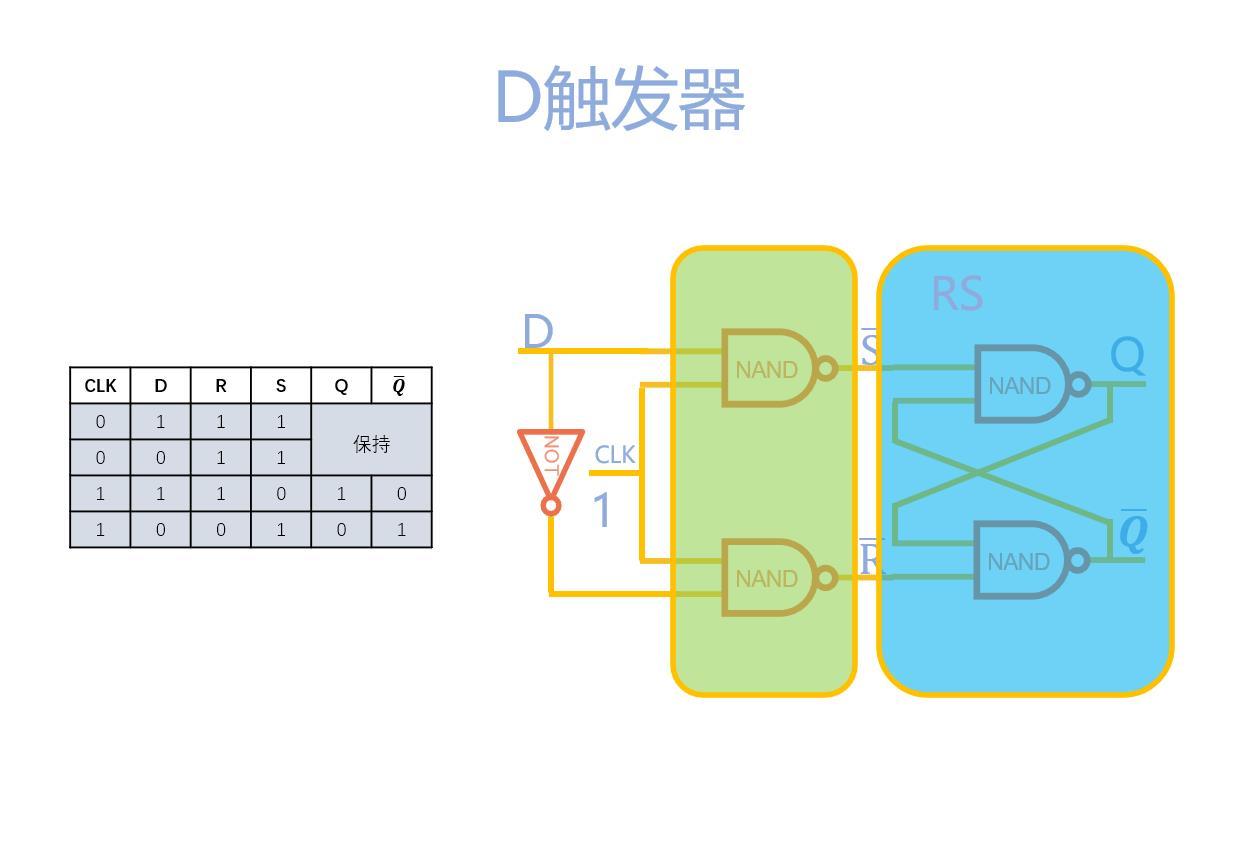

再来看,当CLK控制信号输入为1时,(与非门)屏障被打开了,输入信号D可以通过屏障直接改变RS触发器的状态

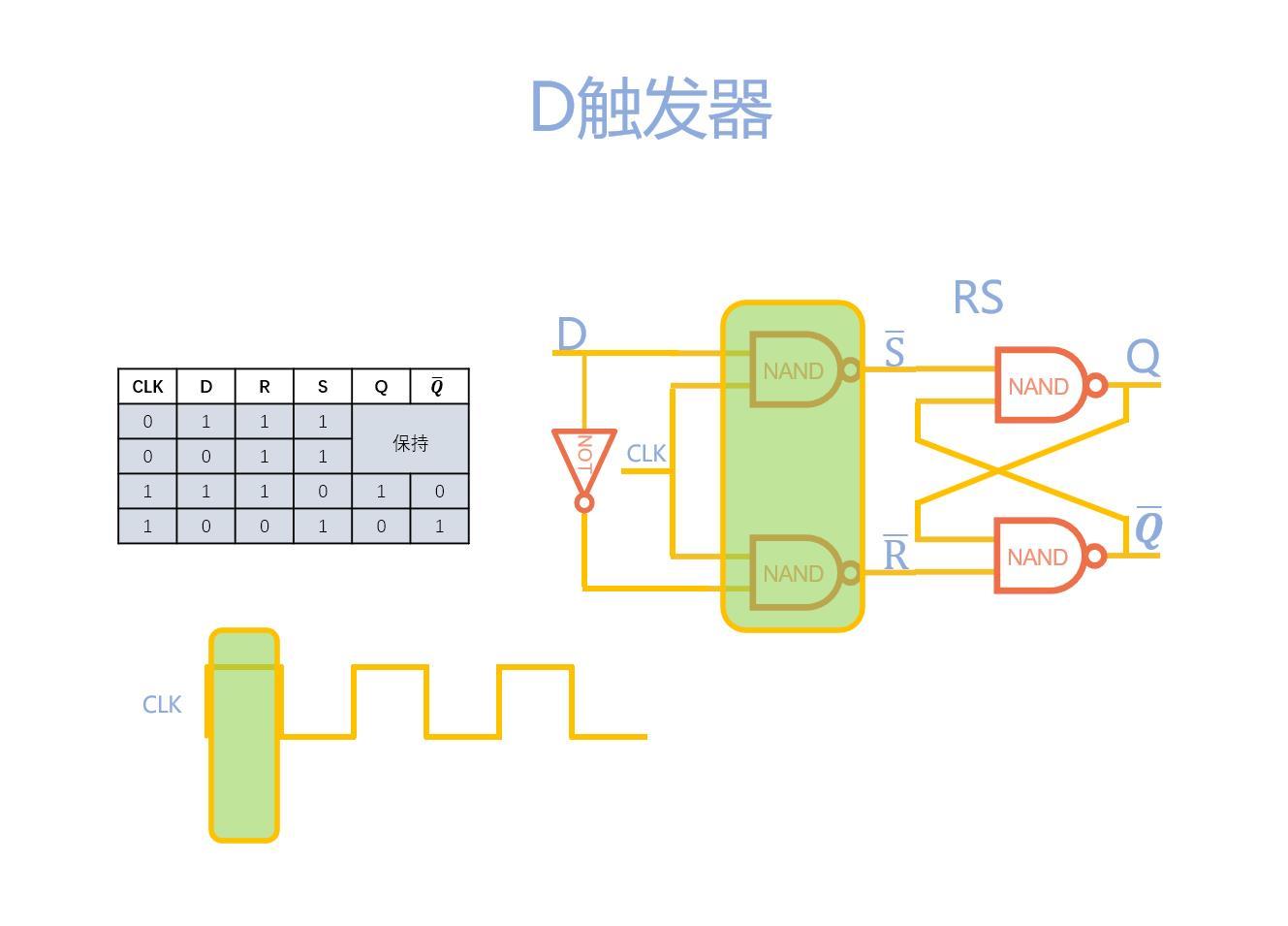

我们把一个时钟信号作为CLK的输入

那么,D的输入信号,在时钟处于高电平是有效的,低电平时,D的输入则被无视。

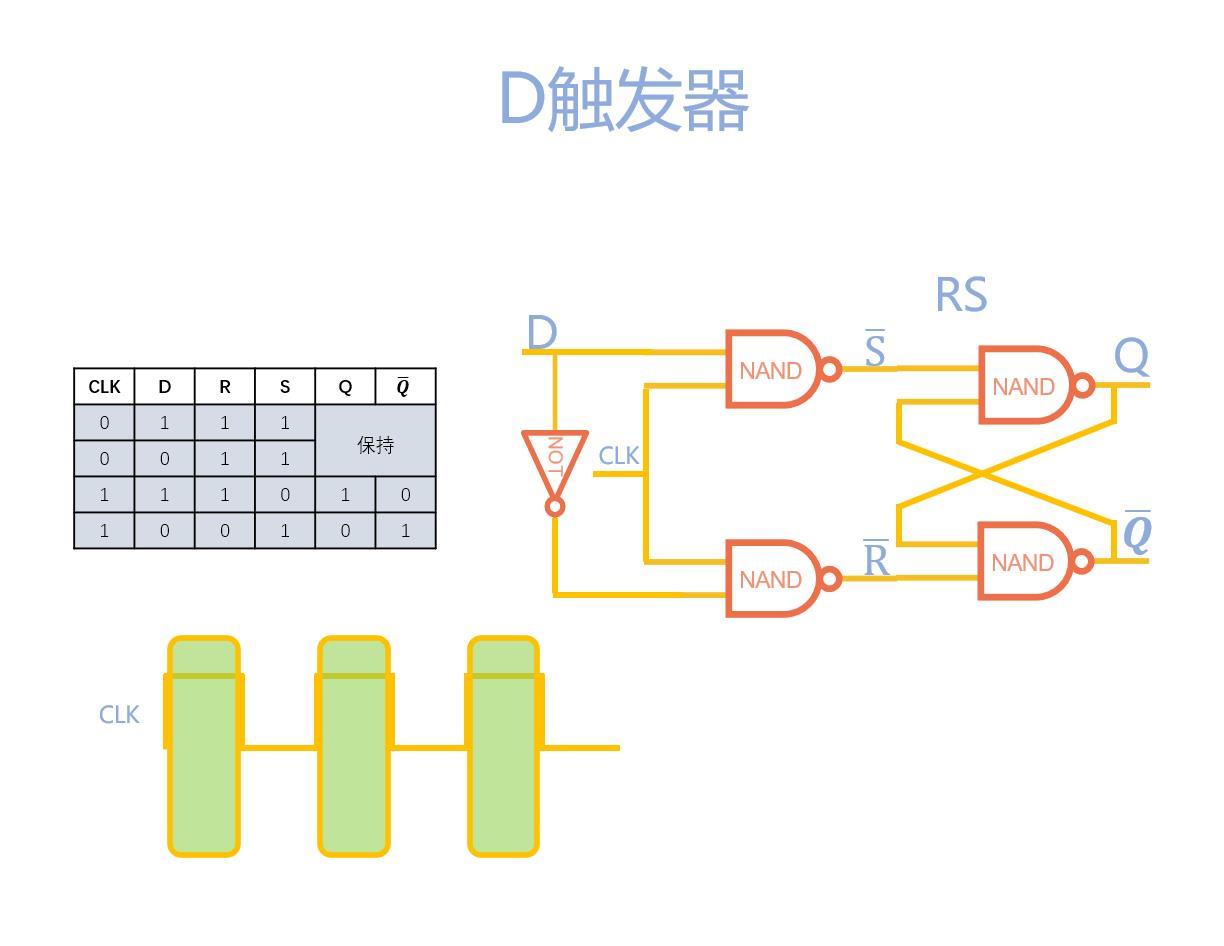

我们把这种在一种电平状态中持续有效或无效的触发器叫做(电平触发D触发器。)

对一个电平触发D触发器来说,当CLK为高电平时,D的输入会忠实的反馈在输出Q和Q!上,即便是D信号上的噪声也一样会被输出到Q。大门打开的时间太长了,房子里的RS触发器很没有安全感。

接下来就回到我们今天的主题,怎么让大门开的时间短一点,减少坏人进来的风险。

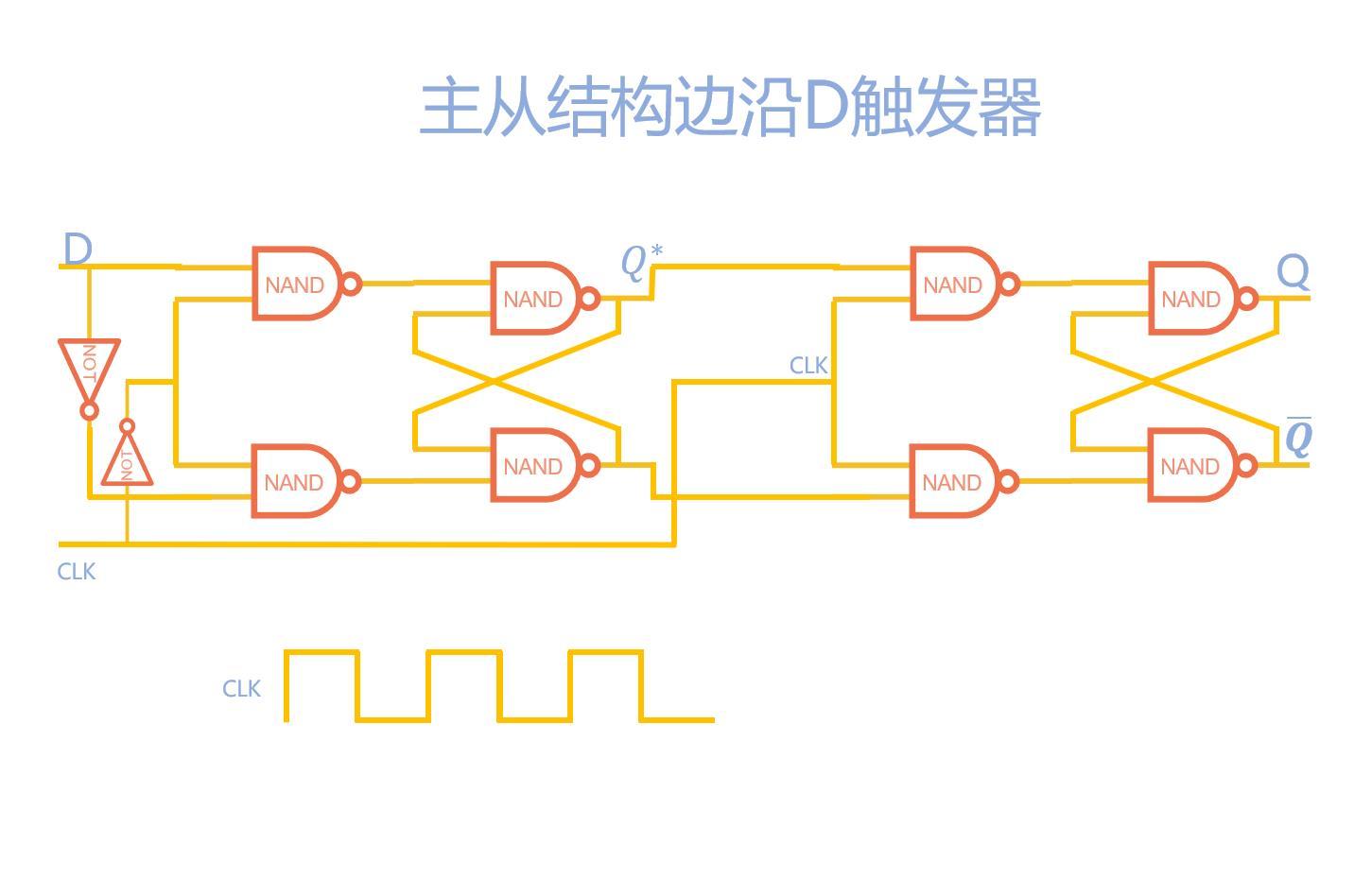

真值表和非门先拿走,再复制一个触发器出来。

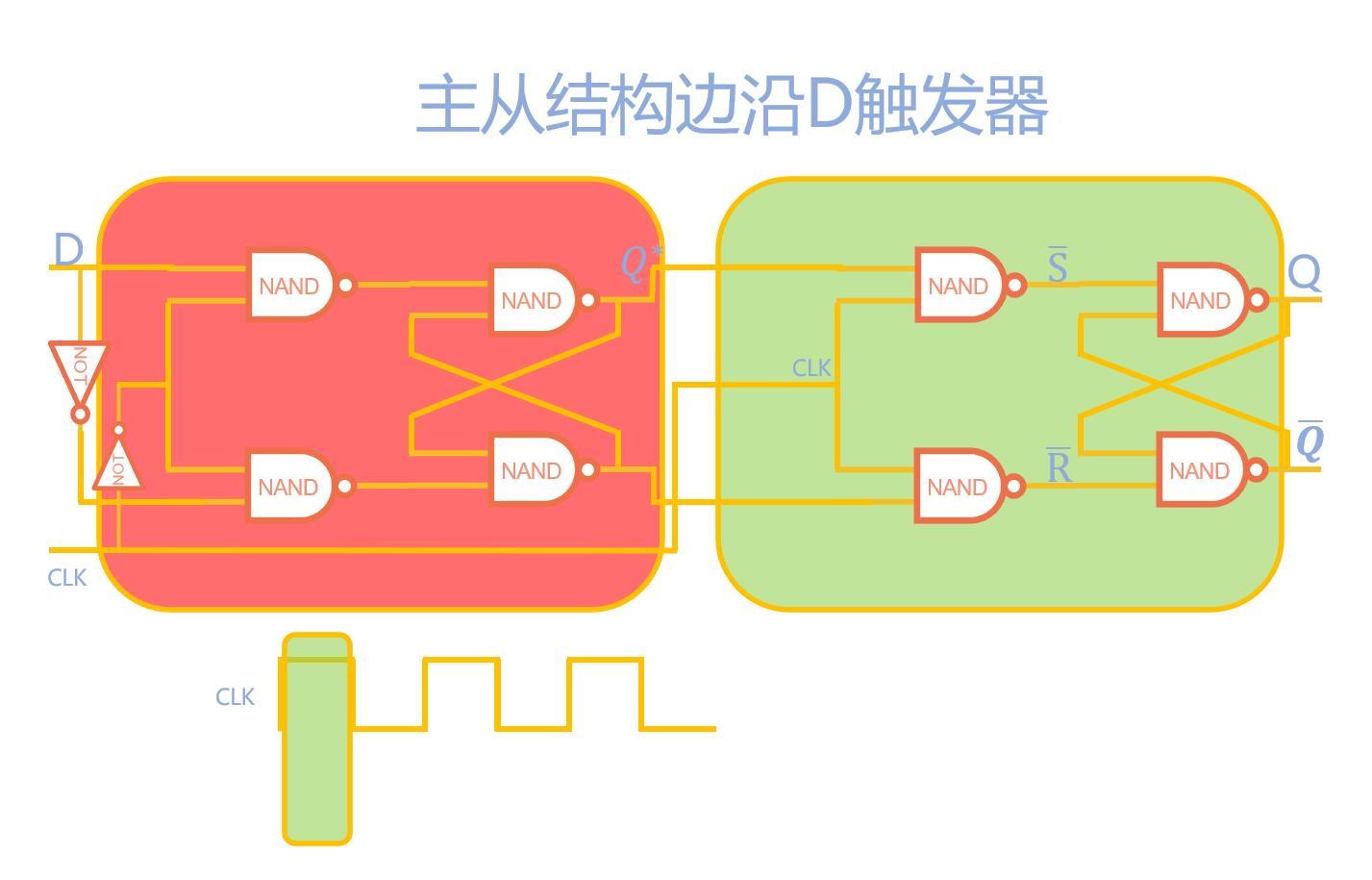

把左边触发器的输出和右边触发器的输入相连,再在两个触发器的CLK之间接入一个非门。再把原先触发器D上的非门还回来。

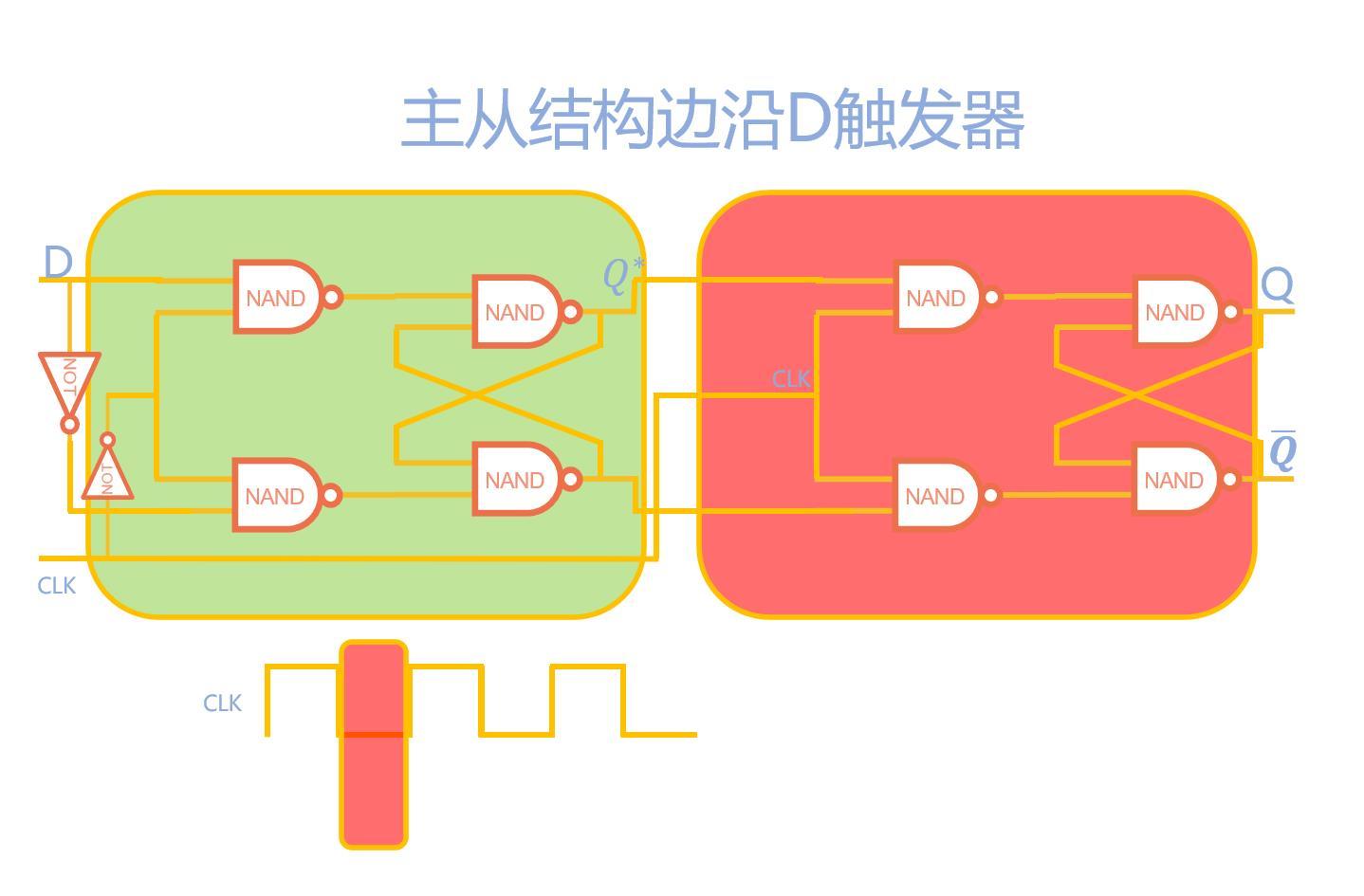

这样,一个主从结构的D触发器就做好了。我们叫这个触发器为 (主从边沿D触发器)

我们来看一下这个触发器的工作状态。

我们把左边的触发器叫主触发器,右边的触发器叫从触发器

首先当第一个时钟高电平周期到来的时候,主触发器是关闭的,输入D进入主触发器,然而这时的触发器输出Q*的值,可能是0,也可能是1。这个值由主触发器的初始值决定。

这个不确定的主Q*值会被传递到从触发器,因为这时的从触发器大门是打开的。

Q的输出也不确定

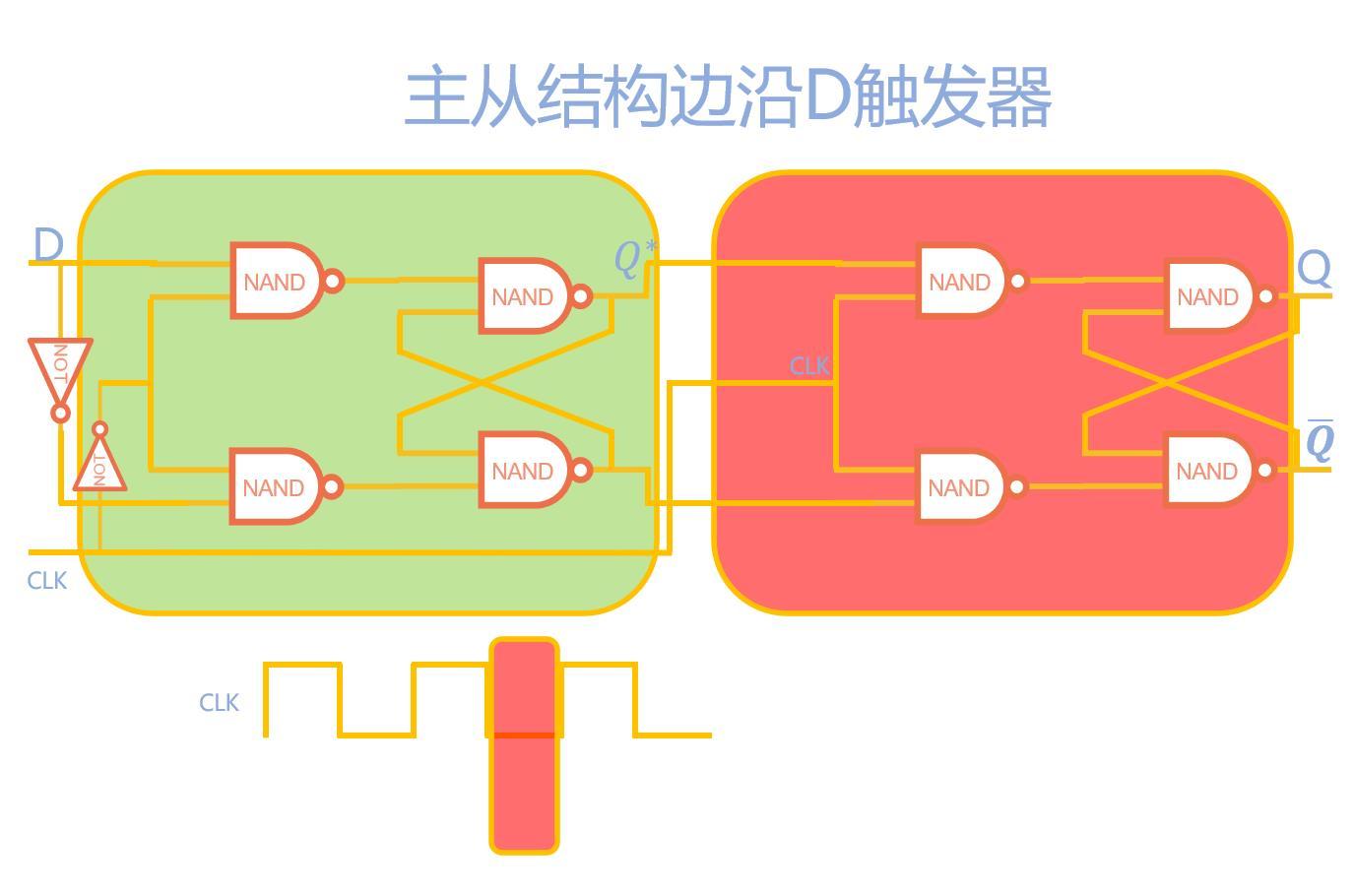

接下来,时钟进入底电平周期,主触发器大门打开,从触发器大门关闭,D传递到Q*,但此时Q输出没有变化,因为从触发器处于关闭状态。

又到了下一个高电平周期,这里要注意,当CLK信号从低电平向高电平反转的这一刻,输出Q的状态变成Q*的状态,而且由于主触发器此时处于关闭状态,D的任何变化都影响不到Q的输出。并且从这一刻开始Q的输出是稳定的输出。

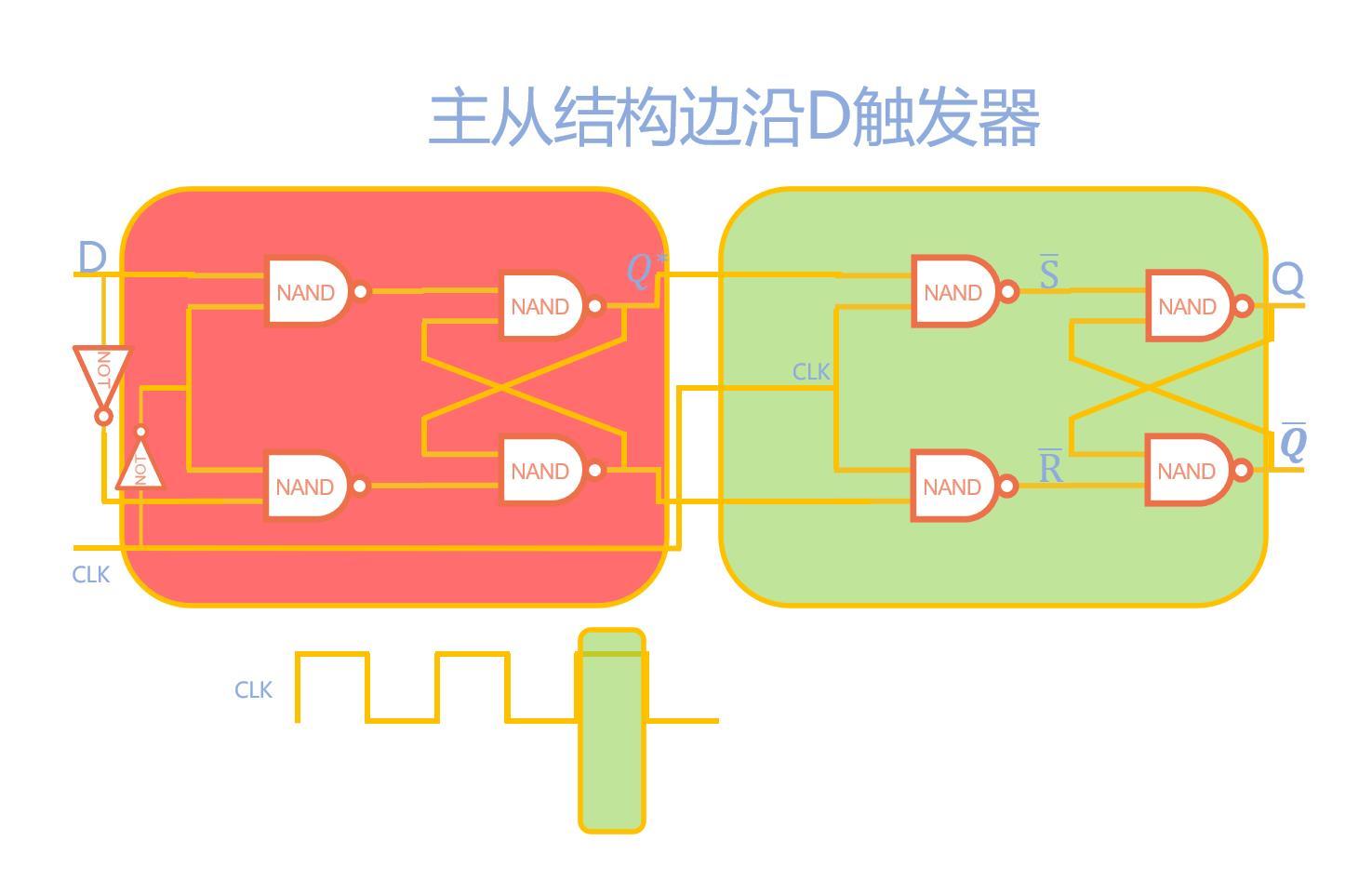

继续往下走,主改变,从不改变,Q输出不变

好,再往下,主不变,从改变。

通过上面的分析,我们可以得出2个结论

第一个、主从触发器输出状态的改变,只发生在控制信号发生转变的时刻,在我们这个图里,是发生在时钟上升沿的时候。我们也可以移动两个触发器CLK之间的非门,让他变成只在下降沿响应。

第二个、主从结构的边沿触发器,启动有一个时钟周期的延迟。从第二个时钟周期才开始有稳定的输出。

-

CMOS

+关注

关注

58文章

6186浏览量

241582 -

或非门

+关注

关注

0文章

37浏览量

15805 -

D触发器

+关注

关注

3文章

181浏览量

49532 -

触发器

+关注

关注

14文章

2050浏览量

63043 -

与非门

+关注

关注

1文章

140浏览量

13328

发布评论请先 登录

求助,关于D触发器SN74LVC1G374与与非门SN74AUP1G00组合问题求解

搭D触发器时,反相器与后面的与非门相接点问题

MOS与非门或非门构成原理

RS触发器是什么?解读rs触发器的作用和数字电路中的rs触发器的作用

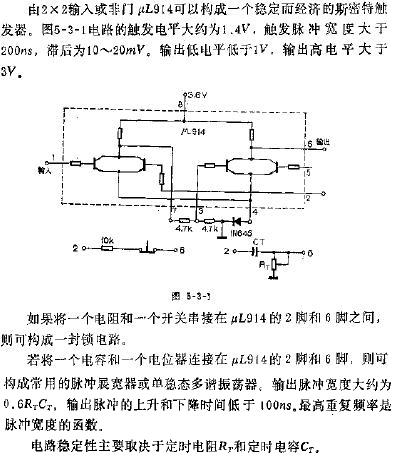

使用或非门和与非门实现触发器

使用或非门和与非门实现触发器

评论