1

引言

需求

MM32F5 系列微控制器具备 QSPI 接口,可以外接 QSPI Flash,扩大可使用的 Flash 空间,从而满足那些需要大 Flash 空间应用的需求,让 Flash 空间的大小不再成为限制应用开发的瓶颈。

但使用 QSPI Flash 之前,还需要对 QSPI 接口进行配置,然后才能执行存储在 QSPI Flash 上的代码,这让应用程序的开发变得复杂。

因此,需要一些解决方案,能够让用户尽可能无感地使用 QSPI Flash 存储应用程序。

案例

以 MM32F5277E9PV 微控制器为例,这个微控制器搭载着 ArmChina STAR-MC1 内核,主频可达 120MHz,拥有 256KB Flash 和 128KB SRAM,使用这块芯片,可以实现一些 “复杂的应用”,例如,运行一个带有 GUI 功能的应用。

在编译这个 “复杂的应用” 时,编译器可能会报错,显示缺少足够 Flash 空间;这个应用可能包含了图片,字库,好几个协议栈,所需要的 Flash 空间非常大,一般微控制器不会拥有这么大的片内 Flash。因此,需要外接一个 QSPI Flash 来解决这个问题。

MM32F5270 系列微控制器带有 QSPI 接口,可以使用 QSPI Flash 来扩展微控制器可使用的 Flash 空间;如果担心外接 QSPI Flash 占据 PCB 空间,则可使用 MM32F5280 系列微控制器,该微控制器合封有一块 1MB ~ 2MB 的 QSPI Flash,无需考虑 QSPI Flash 的电路,节省 PCB 面积。

通过外接 QSPI Flash,就可以拥有足够的空间来实现这个 “复杂的应用”。但开发应用时,仍希望像使用片内 Flash 那样使用 QSPI Flash:下载程序的时候,直接点击 IDE 的下载按钮,就能下载程序;调试代码的时候,直接点击调试按钮,就能进行软件调试;只需少量修改代码,就能让应用程序保存在 QSPI Flash 中,让微控制器直接执行。

为了让 IDE 下载程序到 QSPI Flash 中,需要有一个合适的下载算法。为了让编译器知道应用程序要保存在 QSPI Flash 中,需要修改 Linker 文件,让编译器知道 QSPI Flash 的地址范围。为了让微控制器执行存储在 QSPI Flash 中的程序,还需要实现合适的 2nd Bootloader ,引导微控制器去执行 QSPI Flash 中的程序。

目标

在 MDK 平台上实现定制化的下载算法,可将应用程序下载到 QSPI Flash 中。

尽可能少地改动应用程序代码,使其能够存储在 QSPI Flash 中。

实现简单的 2nd Bootloader,使其能够引导微控制器执行存储在 QSPI Flash 中的应用程序。

在上述的 2nd Bootloader 的基础上,实现量产下载,更新应用程序等特殊功能。

2

配置硬件环境

硬件环境

QSPI Flash

工欲善其事,必先利其器,想在 QSPI Flash 上存储应用程序,就需要选择一款合适的 QSPI Flash 芯片。

选型时,需要重点关注工作电压的范围,部分 QSPI Flash 的工作电压在 1.8V 左右,如果使用 3.3V 供电,是没办法正常工作的,反之亦然。

除了电压范围外,部分 QSPI Flash 芯片在默认情况下,是不允许使用四线模式的,原本 QSPI 的 D2 & D3 引脚会被用于写保护使能(WP)和 HOLD 使能。让 QSPI Flash 允许使用四线模式的方法,需参照使用的 QSPI Flash 芯片手册进行操作。建议使用默认处于四线模式的 QSPI Flash,或者在设计 2nd Bootloader 时,能在跳转到应用程序之前,将四线模式打开。

MM32F5 系列的微控制器支持大多数常见的 QSPI Flash,表1中列举的 QSPI Flash 芯片为经过实际测试可用的 QSPI Flash 芯片:

表1 测试可用的 QSPI Flash 列表

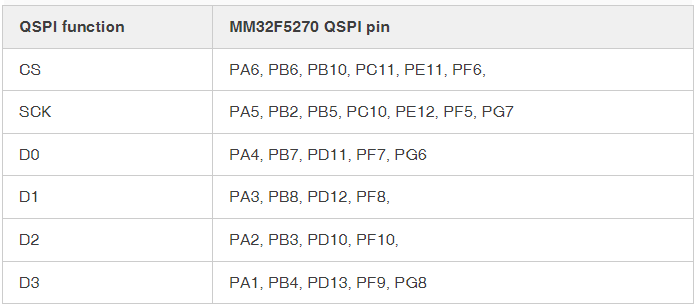

硬件电路设计时,需要了解微控制器的哪些引脚可作为 QSPI 接口,表2 是 MM32F5270 系列微控制器的 QSPI 接口引脚:

表2 MM32F5270 系列微控制器 QSPI 接口引脚

其引脚配置如下:

引脚模式:复用推挽输出。

引脚速度:高速模式,QSPI 的 SCK 时钟最快可达 60MHz,因此应配置成高速模式。

引脚复用功能号:巧合的是,当引脚作为 QSPI 接口时,复用功能号均为 AF10。

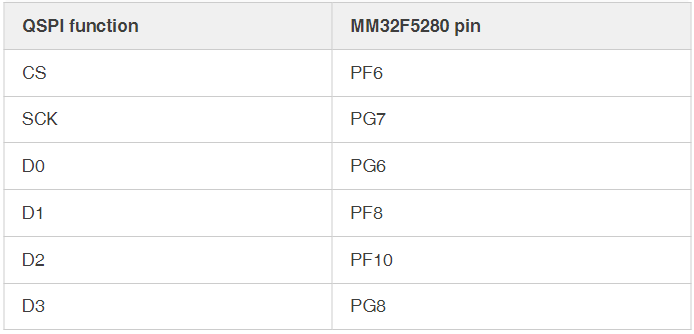

表3 为MM32F5280 系列微控制器的引脚:

表3 MM32F5280的QSPI引脚

可以发现,MM32F5280 系列微控制器只有一组引脚可作为 QSPI 接口,并且这些引脚并没有引出到芯片外部,这是由于 MM32F5280 系列微控制器内部合封了 QSPI Flash,其引脚已经在芯片内部与 QSPI Flash 相连,不需要再引出至芯片外部。

虽然 MM32F5280 片内合封了 QSPI Flash,对应的引脚也直接与其相连,但在使用这块 QSPI Flash 时,仍需配置相应的引脚,其配置方法与 MM32F5270 完全一致。

由于 MM32F5280 系列微控制器将其 QSPI Flash 合封在了芯片内部,因此在 PCB 设计时,可减少外围元件的数量,降低了产品成本。

当使用 MM32F5270 + QSPI Flash 的方案时,由于 QSPI 信号线暴露在微控制器外部,易受到外部电磁环境的干扰,可能无法以最快的速度(SCK 的频率为 60MHz)访问 QSPI Flash,但这个问题在 MM32F5280 上就不会出现。

当然,也正是由于 MM32F5280 系列微控制器的 QSPI Flash 合封在了芯片内部,如果想用使用更大的 Flash 时,还是需要使用 MM32F5270 + QSPI Flash 的方案。

Board

PLUS-F5270开发板

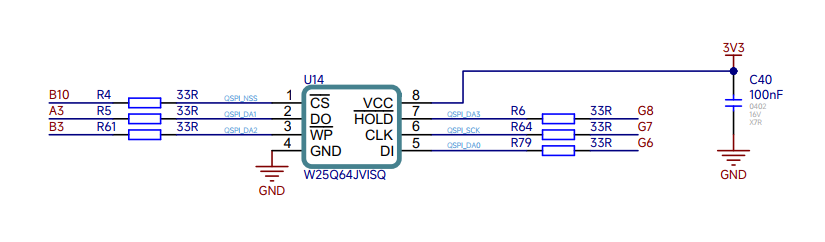

PLUS-F5270 板载华邦的 W25Q64JVSIQ,Flash 大小为 8MB (64Mb),3.3V 供电,默认情况下,四线模式处于打开状态。

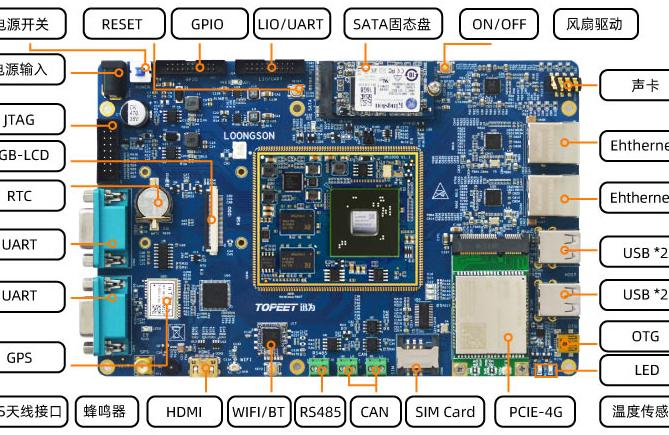

MM32F5270 连接该 QSPI Flash 所使用的引脚号如图2所示:

图2 MM32F5270连接的QSPI Flash引脚

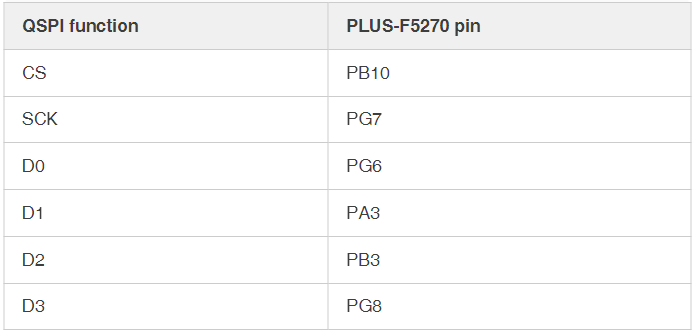

在PLUS-F5270开发板上,MM32F5270芯片与QSPI Flash W25Q64的引脚对应关系如表4所示。

表4 PLUS-F5270开发板上MM32F5270与QSPI Flash W25Q64的引脚对应关系

在设计 MM32F5270 + QSPI Flash 的应用时,建议优先采用 PF6(QSPI_CS)、PG7(QSPI_SCK)、PG6(QSPI_D0)、PF8(QSPI_D1)、PF10(QSPI_D2)、PG8(QSPI_D3) 引脚,从而可使用 MM32F5280 MCU 无缝替换 MM32F5270。

软件工具

在开发调试 MM32F5270 + QSPI Flash 这个 “复杂的应用” 时,需要一些软件工具:

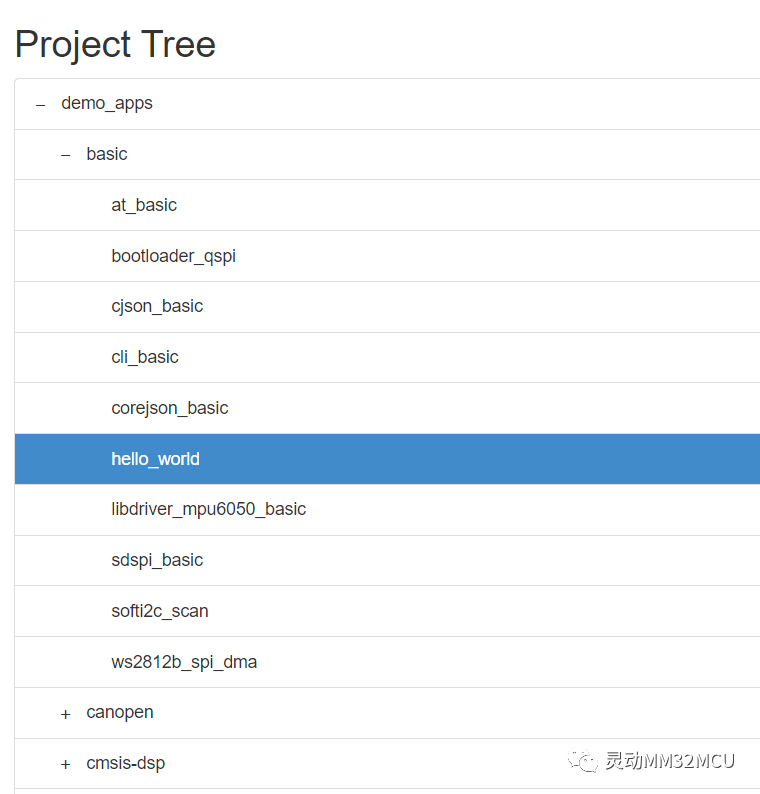

开发平台

嵌入式软件的开发需要一个软件平台,这个软件平台可以是 MDK,IAR,ARMGCC 等,本文将以 MDK 为例,开发并调试所需要的软件。在官网(https://www.keil.com/download/product)页面上,可下载MDK-ARM的安装包并启动安装,使用 MDK 进行工程的调试与下载。

需要注意,MDK 的软件版本最低为 5.37,且需使用 AC6 编译器,旧版本 AC5 编译器不支持编译 STAR-MC1 平台的软件。

下载算法

不同于 SRAM,修改 Flash 中的内容时,需要先将 Flash 中的数据整块擦除,再通过特殊的方法将数据写入到 Flash 中,而不是直接往指定地址进行写操作。因此,需要有一段中间程序,能够帮助调试器将指定位置的数据,写入到 Flash 中。

这段中间程序就叫做下载算法,它运行在 SRAM 中,在修改 Flash 中的内容前,调试器会先将下载算法通过 SWD 或其他调试接口加载到 SRAM 中并执行,然后再加载存放到 Flash 中的数据,让存储在 SRAM 中的下载算法将数据写入到 Flash 中。

获取下载算法有三种方式:

1

从 MCU 厂商的官网中下载相应 MCU 的 PACK 包中获取。

2

从 MDK 的 Pack Installer 中获取。

3

使用开发平台提供的模板文件自行制作。

2nd Bootloader

2nd Bootloader 将会引导微控制器执行存放在 QSPI Flash 中的应用程序,之所以称为 2nd Bootloader,是为了区分固化在微控制器内部的 1st Bootloader。当然,2nd Bootloader 也可以固化到微控制器中,作为 1st Bootloader 来使用,但那样就失去了可定制化的意义。

2nd Bootloader 执行存储在 QSPI Flash 上的应用程序之前,会先初始化 QSPI 外设,以及所用到的 GPIO 引脚,让微控制器能够通过访问地址的形式访问 QSPI Flash,就像访问片内 Flash 那样。当然,这只是 2nd Bootloader 最基本的功能,在此基础上,还可以增加一些定制化的功能,例如为量产而准备的串口 + Ymodem 下载固件功能,或者增加 OTA 升级的方案。

审核编辑:刘清

-

微控制器

+关注

关注

48文章

8249浏览量

162284 -

FlaSh

+关注

关注

10文章

1715浏览量

154672 -

GUI

+关注

关注

3文章

693浏览量

42835 -

SRAM芯片

+关注

关注

0文章

66浏览量

12724 -

QSPI接口

+关注

关注

0文章

14浏览量

3616

原文标题:灵动微课堂 (第245讲)|mm32-2nd-bootloader技术白皮书(1)——配置软硬件环境

文章出处:【微信号:MindMotion-MMCU,微信公众号:灵动MM32MCU】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

mm32-2nd-bootloader技术白皮书——配置软硬件环境

支持过程级动态软硬件划分的RSoC设计与实现

基于SoPC的状态监测装置的嵌入式软硬件协同设计

基于EDA 的嵌入式系统软硬件划分方法

基于FPGA的软硬件协同测试设计影响因素分析与设计实现

软硬件协同设计机遇与挑战分析

为什么要从“软硬件协同”走向“软硬件融合”?

mm32-2nd-bootloader技术进阶设计:实现Ymodem更新代码

软硬件融合的概念和内涵

mm32-2nd-bootloader配置软硬件环境

mm32-2nd-bootloader配置软硬件环境

评论