本文介绍用于单 I/O 电压和双内核电压的双跟踪控制器。它描述了如何将电路施加到一个或多个内核电压。涵盖的原则包括:跟踪需求、实用电路、控制器功能、跟踪电压电平选择、元件值选择、整体电路精度、电路稳定性、一些市售 DC/DC 转换器的特性以及级联电源和并联电源操作。电路提供选项和跟踪波形。

电压跟踪要求

重要的是,微处理器的输入/输出(I/O)和内核电压在上电和关断时不得偏离制造商的规格。典型的现代微处理器的I/O部分通常工作在3.3V或2.5V,而内核可能工作在1.8V、1.5V或1.3V。典型要求是内核和I/O电压在上电/断电期间彼此之间的差异不超过规定的小幅,并且在上电或断电期间电压超出容差不超过几十毫秒。例如,PowerPC™的指南对上电/断电时的超容差I/O和内核电压设置了20ms的限制,对内核电压的规格设置了±50mV的规格。顺便提一下,后一种规格表明,在2.8V时,电源精度(包括任何串联跟踪电路压降)优于±1.8%。

电压跟踪方法

有几种方法可以满足上电/下电跟踪要求:肖特基二极管矩阵电路、多通道串联跟踪电路和并联跟踪电路。虽然串联跟踪表现出串联电压/功率损耗,二极管矩阵需要复杂的二极管选择,并且二极管在短路条件下可能会熔断,但并联跟踪也没有缺点。MAX5039和MAX5040并联跟踪控制器不仅消除了串联电压/功率损耗,而且最大限度地减少了跟踪电路元件的数量,有助于实现成本最低的解决方案。只需一个 MOSFET(每个内核电压)即可跟踪 I/O 和内核电压,并且该 MOSFET 在上电/关断期间仅工作几毫秒。

基本电路说明

图1所示的基本双通道分流电压跟踪控制器电路采用单个MAX5039跟踪控制器和单个NMOS器件,用于系统中的每个内核电压。每个 NMOS 都经过控制,以连接 I/O 和核心电压线路 (VI/O和 V核心) 在通电/关机期间一起。每个控制器和MOSFET仅在上电/断电的跟踪阶段短暂充当串联稳压器,因此功耗最小,每个电源周期仅发生几毫秒。正常工作时不会发生串联电路压降或功耗。

图1.基本的双电压跟踪控制。

当 VI/O出现在 V 之前核心/ 5核心源自更高的 VI/O控制器和 MOSFET 作为串联稳压器的电压。当 V核心出现在 V 之前I/O、VI/O连接到 V核心控制器和 MOSFET 作为串联开关工作的电压。可能最好是 VI/O供应略高于 V核心供应,但这不是必需的(取决于供应特性)。

详细电路

具有所有选项的完整单通道电压跟踪电路如图2所示。本电路包含全功能MAX5040,提供电源就绪或POK输出。当I/O检测电压《1.230V且跟踪阶段完成时,漏极开路POK输出释放至高电平。

组件函数如下:

MAX5040 - 跟踪控制器

Q1, NMOS - 并联开关或稳压器

C1、C2 和 R3 - 稳压器控制环路补偿

R1 & R2 - 反馈电压控制衰减器组 V核心跟踪电压

R9 和 C3 - 反馈线索网络

R5/R6 - 电源就绪检测设定点衰减器

D1 和 CIN - 能量存储允许控制器在电源关闭时继续运行

R7 & R8 - 启动电压设定点衰减器。

图2.用于单核电压的完整电压跟踪电路。

详细的双跟踪控制电路

单V核心图2的跟踪控制器扩展到多个V核心系统只需为每个额外的 V 包含一个额外的控制器/MOSFET 电路核心这需要跟踪。完整的双跟踪电路如图3所示。

图3.用于两个内核电压的双跟踪控制器电路。

请注意,仅使用单个UVLO电阻分压器。第一个控制器的 /SDO 输出以菊花链方式连接到下一个控制器的 UVLO 输入,串联中最终控制器的 /SDO 用于使能所有低压稳压器。每个R1/R2分压器都针对所需的跟踪内核电压进行调整。如果使用MAX5040控制器,每个POK输出可以独立使用,也可以根据需要通过集电极OR提供单个复合POK。否则,可以使用单个MAX5040,其余控制器为MAX5039。

控制器开启操作

MAX5039/MAX5040跟踪控制器由VCC从5V控制电源线供电。以下解释假设VI/O使能信号先于VCORE使能信号。[当两个使能信号重合或VCORE使能先于VI/O使能时,会注意到差异。

当应用 Vcc 时启动启动操作(从零斜坡或升压)。请参阅图 4。

当Vcc达到0.9V时,IC变为活动状态,此时/稳压器关断线路/SDO被驱动为低电平,以确保VI/O和VCORE电源稳压器被禁用。

当VCC达到2.5V时,NDRV被驱动至VCC,接通低阈值MOSFET,将VI/O和VCORE线路连接在一起。电源稳压器仍处于关闭状态,因为 /SDO 保持低电平。

当VCC达到4.5V时(设置R7/R8欠压控制衰减器,使UVLO引脚此时达到1.230V),/SDO被驱动为高电平以使能VI/O和VCORE电源稳压器。VI/O 和 VCORE 电源稳压器输出通过 MOSFET 保持连接在一起,因为 NDRV 仍位于 VCC。

VI/O 先于 VCORE,并开始以 I/O 稳压器特性决定的速率上升。注意:VI/O 和 VCORE 都不应以超过 6.6V/μs 的速率上升。VCORE 随 VI/O 上升,因为两条稳压器输出线通过 MOSFET 连接。在此阶段,I/O稳压器输出同时提供I/O和内核负载,并反向驱动CORE稳压器输出;两个电压相等。[如果VCORE先于VI/O,则VCORE反向驱动VI/O电源;两个电压相等。请参阅图 5。

图4.启动/关断操作,VI/O启用前面的 V核心使。

图5.启动操作,V核心启用前面的 VI/O使。

当 VCORE (=VI/O) 达到编程的 VCORE 设定点时,NDRV 会根据需要从 VCC 下降到较低的值,以将 VCORE 调节到略低于其正常值的预选设定点。[如果 VCORE 在 VI/O 之前,则忽略设定点,VCORE 上升到其正常的稳压器控制电平,VI/O 等于 VCORE,直到 I/O 稳压器输出可用且 VI/O 超过 VCORE。此时,NDRV被驱动为低电平以关闭MOSFET,两个电压变得独立,VI/O上升到正常水平,POK被释放到高电平,控制器导通序列被终止。

控制器和 MOSFET 充当串联调整稳压器,直到 V核心当 V 可用时核心上升到其正常的稳压器控制电平,NDRV 被驱动为低电平以关闭 MOSFET,两个电压变得独立,VI/O上升到正常水平,控制器接通序列终止。

如果导通序列延迟,因为 VI/O或 V核心在释放 /SDO 后,在内部定时 15 毫秒内不会启动,/SDO 将被驱动为低电平以中止开启序列。此故障条件被锁定以防止自动重新启动尝试。

控制器关断操作

在正常运行期间,控制器持续监控内核、I/O 和CORE_FB电压。如果 V核心降至R1/R2设定的内核调节电压(可能是由于意外的高电流负载或短路),NDRV将被驱动为高电平以重新置位调节模式。请参阅图 4。

如果这种情况持续超过10-20ms故障时间,或者如果UVLO引脚上的电压降至其阈值电压以下,则/SDO将被驱动为低电平以开始关断操作。

VUVLO降至UVLO阈值以下,或者故障持续时间超过10-20ms。

/SDO 被驱动为低电平以禁用 VI/O 和 VCORE 电源。

VCORE 和地之间的内部 20W MOSFET 泄放器导通以释放输出负载。

VCORE 开始下降。

VCORE 下降到 VCORE 设定点,而 VI/O 仍高于 VCORE,只要 VI/O 保持大于 VCORE,NDRV 就会根据需要驱动到中间点,以在设定点调节 VCORE。

VI/O 降至 VCORE,NDRV 驱动至 VCC,打开 MOSFET 以将 VI/O 和 VCORE 线路短接在一起。注意: 在断电阶段,Vcc 必须保持在工作范围内,以便控制器可以继续控制 NDRV,直到负载放电[1]。

选择磁芯电压跟踪电平

内核电压跟踪电平[2] VCT(由图2中的反馈衰减器R1/R2设置)是控制器处于跟踪模式时VCORE保持的电压。当VI/O电源在VCORE电源之前出现时,就会发生这种情况。内核电压跟踪电平的选择是一个重要的考虑因素,主要取决于VCORE和VI/O电源精度。约束如下:

VCT 必须低于 VCORE 的容差限制值,

VCT 必须高于 VI/O 减去 VI/O 和 VCORE 之间允许的差异,

VCT 不能高于 VI/O,或

VCT 必须高于允许的最低 VCORE。

我们必须提前知道V的限制I/O和 V核心用品。

例如,我们设置了以下限制:

VI/O 电源 = 3.3V±5%, 或 3.135-3.465V,

VCORE 电源 = 1.5V±50mV (±3.33%),或 1.45-1.55V,

VCORE 最小电压 = 1.5V-10%,或 1.35V,以及

VCT必须在1.35-1.45V范围内,包括所有设置误差。

选择衰减器R1/R2比,使得在跟踪阶段CORE_FB引脚上出现0.8V电压。我们将在示例中使用 VCT = 1.40V。

选择衰减器R1/R2比,使得在跟踪阶段CORE_FB引脚上出现0.8V电压。我们将使用 V电脑断层扫描示例中为 1.40V。

内核电压和电压电脑断层扫描所有来源的误差限值如图 6 所示。五世电脑断层扫描必须保持在 1.35V 以上(最小值)核心允许且低于 1.45V 最小 V核心供应范围。

图6.V 的表示电脑断层扫描误差限制和实现值。

确定错误

将电压设置为CORE_FB时有几个错误。它们是:

比较CORE_FB电压的800mV基准在整个温度范围内的容差为±2%。

电阻器本身具有公差;建议电阻容差为 ±0.1%。

电阻器的温度系数为 25.0% 和 1.0% 电阻器的温度系数为 ±5ppm/°C,100% 电阻器的温度系数为 ±1ppm。

电阻器选择只能以 1-2% 的增量进行。

如果R1和R2的值非常高,则偏置电流可能会产生影响CORE_FB。

内部控制放大器的增益有限,因此R1/R2比值的计算包括有限放大器开环增益的影响。在选择R1/R2时可以忽略复杂的计算,并且可以导出误差项。

但是,不要惊慌

我们可以为您简化所有这些,并使选择 R1/R2 值的过程机械化。实际上,误差的主要贡献是参考本身的±2%。因此,让我们检查每个项目,一次检查一个,看看每个项目对总误差的贡献程度。所有电阻值相关误差均受R1/R2比值的影响,因此随所选V而变化电脑断层扫描。

以任何允许的R1/R2比率执行所有误差计算;它还使 UVLO 和 I/O 检测电阻衰减器的选择机械化(参见图 2)。

许多读者可能更喜欢跳过以下部分,因为它主要是为了帮助理解组件选择电子表格是如何机械化的。

参考错误

这是一个真正的±2%,不能减少。

电阻容差

电阻容差误差不是独立于R1/R2比值的固定值,而是该比值的函数。不建议使用 ±1% 电阻。使用±_%电阻器的成本与使用±0.1%电阻器的成本相似,因此建议使用±0.1%电阻器。VCT=1.40V ( = 0.57143) 时计算出的最差情况容差误差为 ±0.0857%。

电阻器TCR

TCR表示为±,并显示为典型的蝶形曲线,因此最坏的情况是当一个电阻表现出正TCR而另一个电阻表现出负TCR时。事实上,相同值的电阻器应表现出几乎相同的TCR;R1 和 R2 的值相差小于 2:1。假设类似值的电阻将跟踪±10ppm,则在-40至+85°C温度范围内计算出的±25ppm电阻的最差情况TCR误差在VCT=1.40V时为±0.056%。然而,电子表格接受 ±25ppm 作为 0.1% 电阻的实际值(在 1.40V 时,整个温度范围内为 ±0.1398%)。电阻 TCR 误差可根据以下公式计算:

![]()

TCR 以百万分之一表示,但在等式中应写为小数(例如; 25ppm = 0.000025)。T 是与 25°C 的最大差值的绝对值(例如;-40 至 +85°C 产生两个值:-65° 和 +60°)。

当 (+) 和 (-) 在上述商中反转时,类似的值适用。

电阻器选择

虽然可用的电阻值以2%为增量,但通过将R2分成两部分,可以使实际R1/R2比值接近计算值。一个部分 R2a 是计算值以下最接近的可用值;另一部分 R2b 是一个非常低的值。以这种方式处理时,如果电阻在E96序列中,选择误差通常为《±0.01%,如果在E24序列中,则选择误差通常为《±0.05%。

CORE_FB 偏置电流

选择数据手册中在整个温度范围内最大电流为300nA,以允许较短的测试时间,并且不代表实际漏电流,在85°C时小于30nA。 流入R1(10K)的一到三十纳安(参见图7)将导致10-300μV的误差(+0.0007至+0.021%的VCT),因此在误差计算中可以忽略。在此计算中不可能出现负误差。

图7.跟踪电压控制环路。

图8.基准电压测量电路。

控制放大器开环增益限制

在这种情况下,闭环增益误差计算有些难以捉摸,因为给定的基准电压误差包括其自身的环路增益误差,这是由于在单位闭环增益下设置为运算放大器输出时测量的。运算放大器本身的实际开环增益通常为 4000,但范围为 1000 至 10,000[4]。由于NMOS gfs极高,MOSFET源极跟随器增益为》0.99,因此整体环路增益几乎没有变化。通常,图7所示电路的闭环增益计算公式为:

可以应用适当的数学操作来证明,由于 V裁判图8中使用的测量和规格方法,其中V裁判测量为 VR,但建议位于 VR0,校正后的增益公式为:

误差可以通过形成实际与理想比率,减去 1 并将 x100 乘以百分比来计算。当Avol=时,上述VCT方程的最终形式坍缩为1/,因此最小增益下的误差为:

![]()

VCT=1.40V时,实际计算的最差情况开环增益误差为-0.00075至-0.0749%。在此计算中不可能出现正误差。

误差线性和

VCT=+1.40V时,使用0.1%电阻(包括300μV CORE_FB偏置误差、25ppm TCR和0.01%电阻选择误差)计算的最差情况误差总和为-2.316/+2.257%。MAX5039/MAX5040元件选择电子表格计算包括除CORE_FB偏置电流误差外的所有可能误差。

电路稳定性注意事项

图1中的元件C2、C3和R2控制跟踪稳压放大器的稳定性,MAX5039/MAX5040数据资料中有详细描述。建议选择反馈电阻R1作为常值(通过R2的变化进行调整)。这允许 C2 和 R3 保持固定值,而不考虑 V电脑断层扫描所选值[5]。元件选择电子表格针对任何选定的 R1 值计算这些值。

引线网络 C3/R9 提高了跟踪环路速度,以消除 V电脑断层扫描跟踪阶段的过冲和下冲。图 9 和图 10 说明了引入领先网络后的改进情况。注意NDRV在没有超前网络的情况下响应缓慢和过冲,以及由此产生的V电脑断层扫描图9中的过冲和下冲(两个图中的垂直刻度不同)。元件选择电子表格针对任何选定的 R1 值计算这些值。

图9.无引线网络的启动波形。

图 10.带引线网络的启动波形。

电阻R4可以保持固定,而不考虑C的值抄送当领先网络就位时。R4=39适用于 C抄送值为 1500μF 或更高。对于非常大的 C 值抄送,可以考虑降低R4,以略微提高跟踪阶段的环路稳定性。

双跟踪控制启动和关断波形如图11和12所示。

图 11.双跟踪启动波形。

图 12.双跟踪关断波形。

特殊注意事项 - 电源系统电源配置

各个系统设计将具有不同的电源和电源调节器/转换器配置。一个电源系统可能只有一个5V电源,可用于为系统所需的所有低压转换器供电,而另一个电源系统可能只有一个3.3V电源。还有一些可能具有多个I/O和CORE电压,可从单个多电压源获得,而无需使能控制线。每个都将受益于跟踪电路配置的变化。

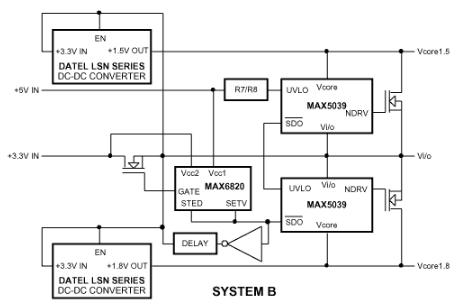

我们将研究 3 种基本配置,分别描述为 A、B 和 C,图 13 中绘制了图表,其变体将在后面描述。

图 13.三种基本的电源系统电源配置。

如何处理跟踪控制电路的主要区别在于转换器的关断控制信号输入的可用性以及转换器本身的特性。系统A具有关断控制信号输入,而系统B没有关断控制,用于+3.3V V。I/O,并且系统 C 在任一 V 上都没有可用的关断控制I/O或 V核心用品。

系统B和C必须包括一个串联开关,用于中断和控制一个或多个电压源。前面已经提到,6.6V/μs是MAX5039/MAX5040跟踪控制器可接受的最大电压上升速率。系统处理器规格也可能限制其 V 的最大上升速率I/O和 V核心电压。在这些情况下,串联开关必须具有控制输出电压上升速率的能力。当跟踪控制器通过单个MAX6820电源排序器IC增强,加上一个串联MOSFET(用于每个非使能电源)时,很容易实现这一点。

此外,我们还需要了解 DC-DC 转换器使能控制的上升和过冲电压速率、使能控制的极性以及任何使能排序要求。如果转换器/稳压器的输出在启动时从另一个电压源反向馈电时行为不正常,或者第一个上来的转换器无法支持整个系统的启动电流,包括电容充电,则可能会产生使能时序要求。在大多数情况下,需要延迟 V核心使能信号在 V 后 _-2msI/O启用信号。

使用MAX1842可以轻松构建功率转换器,以满足所需的电压上升速率和过冲特性,也可以购买现成的模块化转换器。一些模块化功率转换器(如 Power Trends PT6600 系列)可能需要串联 MOSFET 开关来控制电压上升速率,因为显会出现过大的使能控制输出电压上升和过冲率。其他产品如 DATEL LSN 系列表现出良好控制的电压上升速率,无过冲,但可能需要交错使能信号以确保正确的启动操作。PT6600 系列具有正逻辑使能控制,而 LSN 系列具有负逻辑使能控制。表 1 列出了一些选项。

表 1.一些模块化和内置转换器特性

| 转换器类型和系列 | 禁用信号极性 | 启用所需的排序 | 使能控制的输出电压上升率 | 使能控制的输出电压过冲 |

| MAX1842分立器件 | 阴性 | 建议使用单 R/C 延迟 | 控制 | 控制 |

| 达特尔 LSN 系列 | 阳性 | 建议使用单 R/C 延迟 | 控制 | 控制 |

| 电源趋势 PT6600 系列 | 阴性 |

不适用,因为 |

不受控制的。硬线使能导通,并控制输入电压转换率 | 不受控制的。硬线使能导通,并控制输入电压转换率 |

A型系统配置

A型系统可以以并联配置运行,其中所有转换器均由单个电源驱动,如图14所示。所引用的 DATEL LSN 系列转换器对 ENABLE 信号表现出友好的行为,但需要在 ENABLE 线路中使用逆变器。它们还可能受益于内核电压转换器的延迟,以便I/O电压先于内核电压上升。简单实用的延迟和反转电路详见使能部分。

图 14.并联 A 型系统还说明了延迟和反向启用。

采用MAX1842构建的分立式转换器工作在图15所示,使能线路中没有反相器。

图 15.带分立转换器的并联 A 型系统。

B型系统配置

如果稳压器在使能信号上表现不佳,则B型系统最好在级联配置中工作,如图16所示。在级联系统中,外部+3.3V电源由MAX6820 IC控制的串联MOSFET中断;低压转换器由串联 MOSFET 的输出侧供电。从串联MOSFET栅极到地放置一个电容,以控制中断+3.3V的上升速率。电源趋势 PT6600 转换器在使能输入连接到其 V 时表现良好在行当 V在上升速率由MOSFET系列控制。如果使用的稳压器在使能时表现良好,则图17中的非级联B型系统是合适的,不会对3.3V串联MOSFET开关施加额外的应力。

图 16.级联 B 型系统。

图 17.并联B型系统。

C型系统配置

Type-C 系统需要为每个受控电压线提供一个串联的 MOSFET,因为所有电压始终存在,并且没有可用的 ENABLE 控制线。所有线路均由MAX6820电源时序控制器IC中断和斜坡上升,如图18所示。从栅极到地连接的电容器控制电压斜坡速率。MAX5039 /SDO输出在适当的时间使能MAX6820,由+5V输入控制线控制。

图 18.C型系统。

使能延迟和反转电路

MAX5039/MAX5040提供使能输出,标有/SDO,用于使能/禁用外部电源转换器或稳压器。此输出为负真禁用或正真启用。它将吸收1.5mA或源出1mA电流,因此多个MAX5039的输出可能不会一起进行集电极或连接。因此,图3所示的菊花链连接适用于使用多个MAX5039的系统。

人们认识到,这种类型的使能输出并不符合所有稳压器/转换器使能控制信号要求。一些转换器具有正真使能输入,而其他转换器具有正真禁用输入。有些,如电源趋势PT6600系列,需要一个集电极开路电流吸收禁用驱动器,而另一些,如DATEL LSN系列,需要一个电流源极禁用驱动器。采用MAX1842控制器芯片构建的转换器由MAX5039 /SDO灌电流/拉电流输出直接供电。

表2列出了一些商用模块化转换器的启用/禁用要求。

表 2 使能电路要求

| 产品 | 必须使能信号 | 禁用信号必须 | 最大施加电压 |

| 达特尔 LSN 系列 | 开路或低电平 | 源 3mA @>2.25V | 转换器输入+电压 |

| 电源趋势 PT6600 系列 | 开路或高电平 | 灌电流 0.5mA @<0.35V | +5V |

| MAX1842 | 高源电流 1μA @>2.0V | 灌电流 1μA @<0.8V | 转换器输入+电压 |

图19显示了满足几乎所有要求的一些实用的使能/禁用接口电路。包括可选的延迟导通电路。第三个电路提供专门用于Datel LSN系列转换器的功能,其中控制输入为正真禁用或负真使能。使用此转换器,如果输入开路或接地,则使能该装置;并且输入不应超过电源输入电压电平。由于MAX5039/MAX5040 /SDO输出在其输出为高电平时会源出电流,因此当转换器由+3.3V供电时,最好在该接口使用接口PNP晶体管。转换器采用+5V供电时不需要该电路。电路包括R2,用于确保转换器DISABLED引脚在MAX5039不上电期间被驱动为高电平(禁用)。

图 19.启用信号接口 ciruit 选项,包括延迟选项。

完整的A型电路

A型系统电路已经在图2和图3中进行了处理。图20所示为完整的A型并联系统电路,采用分立式MAX1842转换器构成。这些转换器包含内部串联和同步整流器 MOS 开关,可实现最少的组件数量,并且可以提供 1A 连续或高达 2.8A 的峰值输出。提供2A和3A连续输出的类似器件有MAX1644和MAX1623。两个内核电压转换器上较大的软启动电容提供从I/O电压斜坡上升延迟的内核电压斜坡上升,因此不需要额外的延迟。

图20。完整的A型系统电路,采用MAX1842降压控制器IC。

完整的 B 型级联和并联电路

级联B型双跟踪系统的完整电路如图21所示。输出电压上升速率由C21控制。使用此配置,其中启动控制是通过应用 V 进行的在(+5V),重要的是1.5V和1.8V转换器输出在施加V后10ms内达到最终值在(+5V) 电源。

图 21.完整的级联B型系统电路。

并联B型双跟踪系统的完整电路如图22所示。+3.3V输出电压上升速率由C21控制,+1.5V和+1.8V上升速率由转换器本身的使能特性控制。该电路可与Datel LSN系列转换器配合使用。使用此配置,其中启动控制是通过应用 V 进行的在(+5V),重要的是1.5V和1.8V转换器输出在施加V后10ms内达到最终值在(+5V) 电源。

图 22.完整的并联B型系统电路。

完整的C型并联电路

并联C型双跟踪系统电路如图23所示。所有三种电压的输出电压上升速率均由C21控制。使用此配置,其中启动控制是通过应用 V 进行的在(+5V),重要的是所有三个处理器系统电压在施加V后10ms内达到最终值在(+5V) 电源。

图 23.完整的C型系统电路。

总结

MAX5039/MAX5040为处理器I/O和CORE电压提供简单、高性价比的分流电压跟踪功能,但在电源可电子禁用/使能的应用中不会引入串联电压/功率损耗。

当电源电压源不能单独使能/禁用时,增加串联MOSFET开关和单个MAX6820(SOT23)电压排序器IC即可满足额外的控制要求。

几乎任何电力系统电压跟踪要求都可以通过所提出的一个完全详细的电路或其简单变体直接满足,并且几乎任何使能/禁用接口都可以通过提出的使能接口电路之一进行适当的机械化。

元件选择电子表格简化了跟踪电路设计的过程。适当时可提供定制评估板和技术援助。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18986浏览量

264563 -

转换器

+关注

关注

27文章

9449浏览量

156984 -

控制器

+关注

关注

114文章

17881浏览量

195168

发布评论请先 登录

通用4位 VID I/F Kepler DSP AVS内核电源设计

请问TS201的核电压、I/O电压、DRAM电压、时钟电压上电顺序怎么管理?

便携式微处理器内核电源电压的改进

便携式微处理器内核电源电压的改进

用于I/O、微处理器和DSP内核电压的双电压跟踪电路

用于I/O、微处理器和DSP内核电压的双电压跟踪电路

评论