在具有一个主站和多个从站的典型SPI系统中,专用的片选信号用于寻址单个从站。随着从站数量的增加,芯片选择线路的数量也会增加。在这种情况下,系统的电路板布局可能会成为一个相当大的挑战。

一种布局替代方案是菊花链。本文解释了菊花链SPI系统的细节,并展示了如何使用软件通过一串从站传播命令。

标准SPI™/QSPI/™ MICROWIRE™兼容微控制器通过3线或4线串行接口与其从器件通信。典型接口包括片选信号(/CS)、串行时钟(SCLK)、数据输入信号(DIN),偶尔还包括数据输出信号(DOUT)。与I2C系统中通常一样,可单独寻址的设备与总线上的单个设备轻松通信。

基本串行通信接口

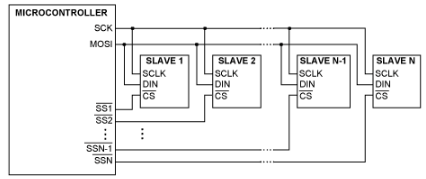

许多SPI器件无法单独寻址。因此,这些设备与总线上的单个设备之间的通信需要额外的硬件或软件组织。图1显示了一个微控制器与多个从设备通信的系统。

图1.具有独立芯片的微控制器为多个从设备选择。

在上述系统中,微控制器使用一个串行时钟输出(SCK)和一个主输出/从输入线路(MOSI)来命令所有从机。微控制器为每个从设备分配一个独立的从机选择信号(/SS_),以便可以单独对它们进行寻址。由于所有从机共享单个时钟和数据线,因此只有/CS输入置位为低电平的从机才会确认并响应串行时钟和数据线上的活动。当系统中的从设备很少时,该系统易于实现。在具有许多从器件的系统中,微控制器需要的/SS_输出与从器件数量一样多。此体系结构增加了硬件和布局的复杂性。

菊花链替代品

硬件约束会使图 1 中的方法变得不切实际且难以实现。串行接口应用的另一种方法是菊花链,它通过串联的设备传播命令。图 2 显示了采用菊花链配置的 N 器件系统。

图2.具有多个菊花链从器件的微控制器。

单个/SS(或/CS)信号控制所有从机的/CS输入;所有从站接收相同的时钟信号。只有链中的第一个从站(SLAVE 1)直接从微控制器接收命令数据。网络中每隔一个从站从链中前一个从站的DOUT输出接收其DIN数据。

为了使菊花链成功工作,从机必须能够在给定的命令周期内在DIN上输入命令(由一个命令中时钟所需的时钟脉冲数定义),并在随后的命令周期内在DOUT上输出相同的命令。简单地说,有一个命令周期的 DIN 到 DOUT 延迟。此外,从机必须只执行在/CS的上升沿写入它的命令。这意味着只要/CS保持低电平,从机就会忽略该命令,并在下一个命令周期的DOUT上输出该命令。如果/CS在给定的命令周期后变为高电平,则所有从站执行刚刚写入其各自DIN输入的命令。如果/CS变为高电平,则数据不会在DOUT输出。此过程使链中的每个从站都可以执行不同的命令。只要满足这些菊花链要求,微控制器只需要三个信号(/SS、SCK和MOSI)来控制网络中的所有从站。

菊花链是如何实现的

在菊花链系统中(图 2),SLAVE 1 直接从微控制器接收数据。该数据被时钟输入SLAVE 1的内部移位寄存器。只要/CS(或/SS)保持低电平,该数据就会传播到SLAVE 1的DOUT输出。SLAVE 1 的 DOUT 进入 SLAVE 2 的 DIN,因此当数据出现在 SLAVE 2 的 DOUT 输出上时,数据将时钟输入 SLAVE 1 的内部移位寄存器。正如SLAVE 2从SLAVE 1接收数据一样,微控制器可以同时向SLAVE 1发送另一个命令。此新命令将覆盖 SLAVE 1 的移位寄存器中的先前数据。只要/CS保持低电平,数据就会在整个菊花链中传播,直到每个从设备收到适当的命令。加载到每个从站移位寄存器的命令在/CS的上升沿执行。以下示例使用MAX5233和MAX5290演示菊花链。

示例电路 #1

图3所示为三个MAX5233 IC,采用菊花链结构连接。MAX5233为双通道、10位DAC(包含两个DAC通道A和B)。RSTV 连接到 VDD,模拟输出功率可达中间电平。

图3.菊花链电路 #1。

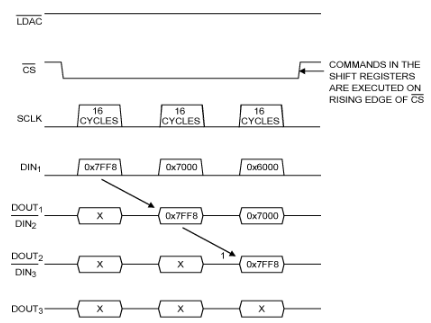

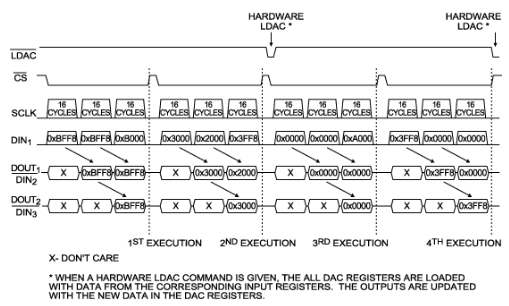

图4显示了将IC1(A1和B1)、IC2(A2和B2)和IC3(A3和B3)输出分别设置为零、中和满量程的命令序列。对于此示例,使用以下命令:

0x7FF8—用满量程数据加载IC3 DAC寄存器,并将两个输出(A3、B3)设置为满量程

0x7000—用中间电平数据加载IC2 DAC寄存器,并将两个输出(A2、B2)设置为中间电平

0x6000—用零电平数据加载IC1 DAC寄存器,并将两个输出(A1、B1)设置为零电平

图4.电路 #1 — 命令序列 A。

在第一个命令周期(一组16个SCLK脉冲)中,0x7FF8被加载到IC1的移位寄存器中。当/CS保持低电平时,该数据通过IC1传播,并在DOUT输出1在下一个命令周期中。在第二个命令周期中,来自 DOUT 的数据1直接移动到 DIN2,0x7FF8被加载到IC2的移位寄存器中。同时,一个新命令0x7000被加载到IC1的移位寄存器中,从而覆盖其先前的命令。

在第三个命令周期中,第一个命令0x7FF8加载到IC3的移位寄存器中。第二个命令 0x7000 加载到 IC2 中,IC1 接收新命令 0x6000。所有三个IC现在都有一个命令,它们通过移位寄存器中的菊花链接收该命令。当/CS变为高电平时,加载的命令将执行;A1 和 B1 设置为零电平,A2 和 B2 设置为中间电平,A3 和 B3 设置为满量程。

图 5 演示了一个更复杂的命令序列。使用以下命令(更多信息参见MAX5233数据资料):

0x3FF8—加载输入寄存器A,满量程数据,DAC寄存器和输出保持不变

0x3000—加载具有中间量程数据的输入寄存器A,DAC寄存器和输出保持不变

0x2000—加载输入寄存器A,具有零电平数据,DAC寄存器和输出保持不变

0xBFF8—加载输入寄存器B,满量程数据,DAC寄存器和输出保持不变

0xB000—加载输入寄存器B,其中量程数据、DAC寄存器和输出保持不变

0xA000—用零电平数据加载输入寄存器B,DAC寄存器和输出保持不变

0x0000 - 无操作

图5.电路 #1 — 命令序列 B。

在前三个命令周期中,菊花链中的三个IC中的每一个都在其移位寄存器中接收一个命令。IC1、IC2 和 IC3 的命令分别为0xB000、0xBFF8和0xBFF8。这些命令在/CS的上升沿执行(第一次执行)。首次执行后,IC1、IC2和IC3的输入寄存器B分别加载中间量程、满量程和满量程数据。此时,B1、B2、B3保持不变,因为每个IC的DAC寄存器B保持不变。

在接下来的三个命令周期中,仅加载输入寄存器A的命令将写入每个IC的移位寄存器。DAC寄存器A及其输出保持不变。在/CS的上升沿,IC1、IC2和IC3的输入寄存器A分别加载满量程、零电平和中间电平数据。此时,A1、A2和A3保持不变,因为仅更新了输入寄存器A,而不是DAC寄存器A。

第二次执行后的硬件/LDAC命令(驱动/LDAC低电平有效)加载所有DAC寄存器及其各自输入寄存器中的数据。DAC输出使用来自其相应DAC寄存器的数据进行更新。A1、B2 和 B3 进入满量程。A2 降至零电平,A3 保持在中电平。

在第三系列命令周期中,IC2和IC3被赋予NO-OP命令(0x0000),而IC1接收0xA000命令,以加载其输入寄存器B的零电平数据。第三次执行后,所有输出保持不变。

在第四个命令周期系列中,IC1和IC2接收NO-OP命令,而IC3接收0x3FF8。第四次执行后,IC3的输入寄存器A加载满量程数据。另一个硬件/LDAC命令使用输入寄存器中的数据加载DAC寄存器。这会导致 B1 从中间量程变为零电平,A3 从中间量程变为满量程。所有其他输出保持不变。

| 模拟输出名称 | 输出状态 | |||

| 上电后(RSTV = VDD) | 首款硬件低电平有效LDAC | 第二个硬件低电平有效LDAC | ||

| IC1 | A1 | 中档 | 满量程 | 满量程 |

| B1 | 中档 | 中档 | 零刻度 | |

| IC2 | A2 | 中档 | 零刻度 | 零刻度 |

| B2 | 中档 | 满量程 | 满量程 | |

| IC3 | A3 | 中档 | 中档 | 满量程 |

| B3 | 中档 | 满量程 | 满量程 | |

示例电路 #2

图6所示为三个采用菊花链配置的MAX5290双通道、12位DAC。PU 连接到 DVDD,模拟输出通电至满量程。MAX5290没有用于菊花链的专用数字输出。相反,两个UPIO(用户可编程输入/输出)引脚中的一个必须由串行接口编程才能DOUTDC_模式。详见MAX5290数据资料。

图6.菊花链电路 #2。

图7给出了命令序列示例,使用了以下命令(更多信息参见MAX5290数据资料)。

0xDFFF—用满量程数据加载所有输入和DAC寄存器,DAC A和B输出更新

0xD800—使用中间量程数据加载所有输入和DAC寄存器,DAC A和B输出更新

0xD000—用零电平数据加载所有输入和DAC寄存器,DAC A和B输出更新

0xE400 — 将 DAC A 和 DAC B 置于关断模式

0xE40F—使DAC A和DAC B退出关断模式

0xFFFF - 无操作

图7.电路 #2 示例命令序列。

加载到每个器件移位寄存器的命令在/CS的上升沿执行。在第一次执行时,所有DAC输出都会更新。IC1的DAC输出变为零电平,IC2的DAC输出变为中间电平,IC3的DAC输出变为满量程。

在第二个命令周期中,IC2的DAC A和B都处于关断模式,命令0xE400。无操作命令使IC1和IC3不受影响。在第三个命令周期之后,IC1的输出变为满量程,IC3的输出变为零电平。当IC2的输出保持关断状态时,数据在内部输入和DAC寄存器中更新。IC2在最后一个命令周期内恢复到正常工作模式,输出进入满量程。

| 模拟输出名称 | 输出状态 | |||||

| 上电后(PU = VDD) | 首次执行后 | 第二次执行后 | 第三次执行后 | 第四次执行后 | ||

| IC1 | A1 | 满量程 | 零刻度 | 零刻度 | 满量程 | 满量程 |

| B1 | 满量程 | 零刻度 | 零刻度 | 满量程 | 满量程 | |

| IC2 | A2 | 满量程 | 中量程 | 关闭 | 关闭 | 满量程 |

| B2 | 满量程 | 中量程 | 关闭 | 关闭 | 满量程 | |

| IC3 | A3 | 满量程 | 满量程 | 满量程 | 零刻度 | 零刻度 |

| B3 | 满量程 | 满量程 | 满量程 | 零刻度 | 零刻度 | |

-

微控制器

+关注

关注

48文章

8249浏览量

162271 -

寄存器

+关注

关注

31文章

5588浏览量

129035 -

SPI

+关注

关注

17文章

1866浏览量

99734

发布评论请先 登录

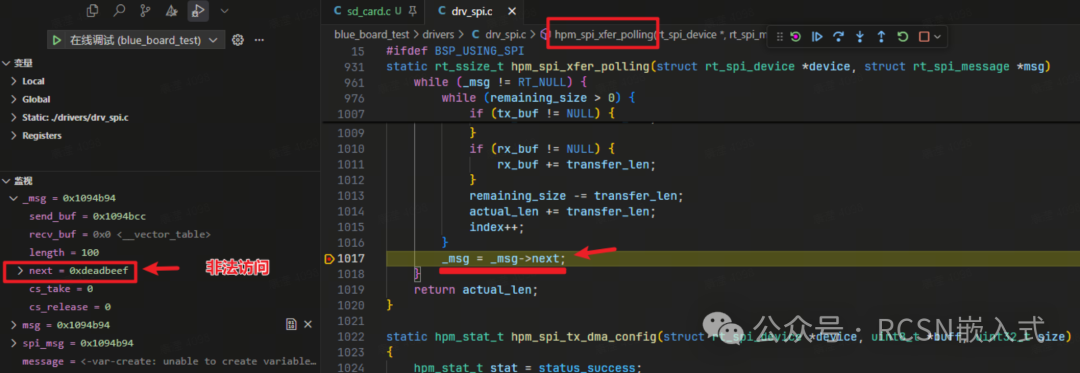

RT-Thread SPI链式传输非法访问?揭秘致命陷阱!

【分享】EasyGo 链式SVG系统的实时仿真应用

如何用ADS1271的SPI接口模式与STM32进行通信?

如何让SPI额外发出一个时钟?

请问如何让SPI额外发出一个时钟?

STM32 与ads1271的SPI通信问题

可实现工业级精度和分辨率菊花链温度传感器包括BOM及原理图

解决了合并单元对前端需求的模拟前端 (AFE)设计

FPGA菊花链下载时initialize chain识别不到器件

8片菊花链式WS2812B 8x8 RGB LED矩阵开源

TIDA-010076-通过单对以太网 (T1) 实现菊花链式电源和数据传输的PCB layout 设计

BQ79600(UART/SPI至菊花链网桥IC)的安全手册

菊花链式SPI器件

菊花链式SPI器件

评论