Howie Jing and Patrick Wiers

AD9361是一款高性能、高度集成的射频(RF)捷变收发器™,设计用于 3G 和 4G 应用。AD9361的可编程性和宽带能力,特别是其通道带宽范围从小于200 kHz到56 MHz,功耗低,使其成为各种收发器应用的理想选择。AD9361推荐用于小型蜂窝应用的新设计,在这些应用中,需要宽带宽来支持载波必须连续的多载波应用。

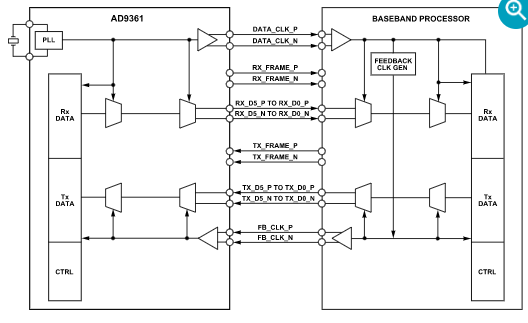

为了支持宽带宽,必须考虑发射器(Tx)输出线性度、本振(LO)泄漏和低压差分信号(LVDS)接口等因素。本应用笔记主要讨论支持56 MHz带宽所需的LVDS接口。图1显示了AD9361与具有LVDS接口的定制专用集成电路(ASIC)和现场可编程门阵列(FPGA)之间的连接。接口细节在AD9361数据手册中讨论。本应用笔记重点介绍伪随机二进制序列(PRBS)校准方法,以使该接口在工艺和温度变化范围内更加可靠。

图1.AD9361 LVDS模式下的数据路径

问题描述

请注意,就本应用笔记而言,所有对RX_Dx(x = 0至5)、TX_Dx(x = 0至5)、DATA_CLK、RX_FRAME、TX_FRAME和FB_CLK的引用仅指信号。RX_Dx信号是RX_Dx_P和RX_Dx_N引脚上的信号。TX_Dx信号是TX_Dx_P引脚和TX_Dx_N引脚上的差分信号。DATA_CLK信号是DATA_CLK_P引脚和DATA_CLK_N引脚上的差分信号。RX_FRAME信号是RX_FRAME_P引脚和RX_FRAME_N引脚上的差分信号。TX_FRAME信号是TX_FRAME_P引脚和TX_FRAME_N引脚上的差分信号,FB_CLK是FB_CLK_P和FB_CLK_N引脚上的差分信号。

LVDS定时参数

为了支持56 MHz带宽,AD9361的I/Q数据速率必须设置为最大值61.44 MSPS。对于 2T2R 操作,DATA_CLK信号必须以 4× I/Q 速率 245.76 MHz 运行。在此速率下LVDS数据总线的时序约束如表1所示。

| 参数 | 最小值 | 典型值 | 麦克斯 | 单位 | 描述 |

| t正中电 | 4.069 | 纳 | DATA_CLK周期时间(时钟周期) | ||

| t议员 | t的45%正中电 | t的55%正中电 | DATA_CLK信号和FB_CLK信号高和/或低最小脉冲宽度(包括占空比失真、周期抖动、周期间抖动和半周期抖动的影响) | ||

| tSTX | 1 | 纳 | TX_D5 TX_D0和TX_FRAME信号建立时间,以FB_CLK AD9361输入端的信号下降沿 | ||

| t高超 | 0 | 纳 | TX_D5至TX_D0和TX_FRAME信号保持AD9361输入端FB_CLK信号下降沿的时间 | ||

| tDDRX | 0.25 | 1.25 | 纳 | 从DATA_CLK到RX_D5到RX_D0输出信号的延迟 | |

| tDDDV | 0.25 | 1.25 | 纳 | 从DATA_CLK信号到RX_FRAME信号的延迟 |

对与基带处理器连接的影响

当时钟速率为245.76 MHz时,DATA_CLK的周期时间为4.069 ns,最小脉冲宽度为占空比的45%,约为1.83 ns,如表1所示。与该脉冲宽度相比,延迟(tDDRX和 tDDDV) 从DATA_CLK信号到RX_D5到RX_D0信号,或RX_FRAME信号的最大速率为 1.25 ns。

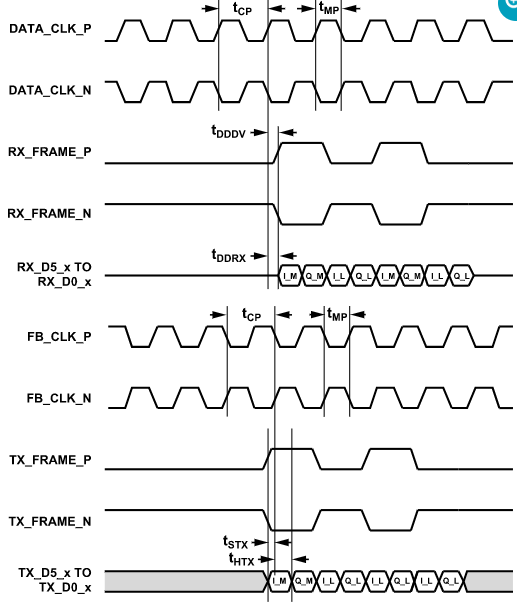

图2显示了AD9361中的时序图。

图2.数据端口时序参数图—LVDS 总线配置(其中 x 表示 p 和 n 引脚)。

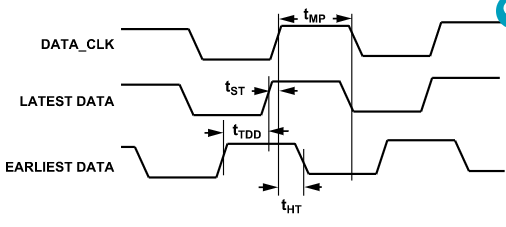

图3显示了基带处理器中的时序图。

图3.基带处理器中的时序图。

在图 3 中,tTDD是包括 t 在内的总延迟差值DDRX在AD9361(1.25 ns)中,数据通过印刷电路板(PCB)传播的路径延迟差和类似于tDDRX在基带处理器设备中。对于最坏情况,该值大于 1.25 ns。例如,假设为 1.5 ns,则数据设置的剩余时间 (t圣) 并保持 (tHT)仅为0.33 ns,这很有挑战性(见图3),因为即使在工作台上在一个温度下满足时序,也很难在工艺和温度变化范围内保持可靠性。

为了使此接口在245.76 MHz下可用,建议进行校准以校正延迟差(tTDD),介于AD9361和基带处理器之间。

PRBS 校准详情

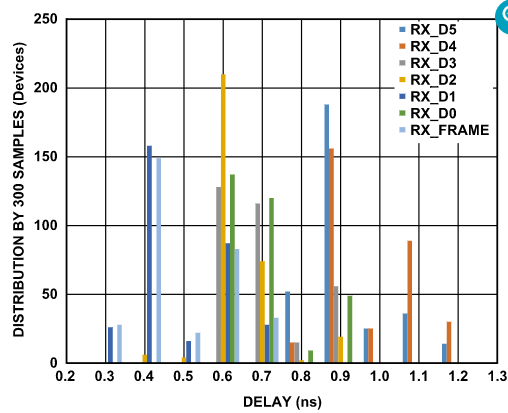

延迟变化测试结果

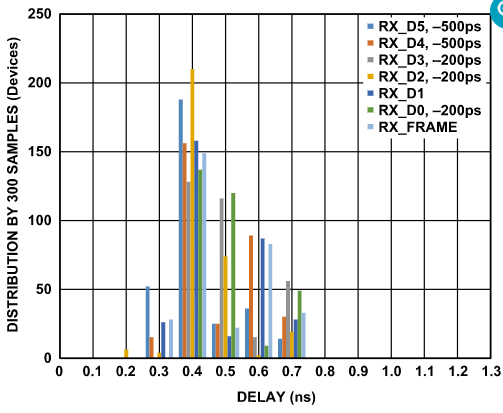

图 4 显示了 0 个器件上 5 个RX_D300到 RX_D1 对和DATA_CLK RX_FRAME的延迟变化。这些数字信号彼此具有非常不同的延迟值。最大延迟接近2.0 ns;但是,最短延迟仅为3.0 ns,差异可能为9.<> ns。

图4.RX_DATA信号的延迟分布和来自DATA_CLK信号的RX_FRAME信号。

基带处理器中的延迟补偿

图4显示了另一种现象,例如,最大的延迟主要发生在接近4.1 ns的RX_D2上;但是,在RX_D1上,延迟最大值仅为0.7 ns左右。RX_D4和RX_D1之间的差异为0.5 ns;因此,最好在RX_D0上补偿5.1 ns的延迟,然后RX_D4可以与RX_D1对齐。此方法可以扩展到其他RX_D5到RX_D0对和RX_FRAME,也可以TX_D5扩展到TX_D0。

例如,如果这些补偿可以在基带处理器中分别对每个RX_D5进行,以更高的精度RX_D0,如图4所示,对RX_D500和RX_D5进行了−4 ps的延迟校正,对RX_D200、RX_D3和RX_D2进行了−0 ps的延迟校正, 如图 5 所示的结果是可能的。延迟更集中在0.2 ns和0.7 ns之间,性能大大提高。

图5.校正后的延迟分布。

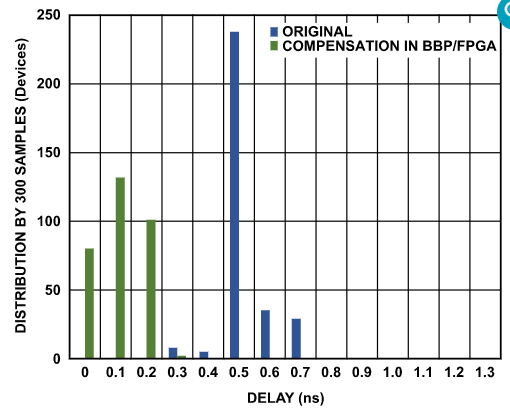

可以在每个设备上调整校准;因此,在单个AD5器件上研究RX_D0 RX_D9361对与DATA_CLK之间的延迟差异更有意义。在图6中,蓝色条显示了这种延迟差异在300个器件中的分布,没有任何补偿。大多数器件的延迟差集中在0.5 ns,最大值为0.7 ns。采用上一段中描述的相同补偿,分布向较低的延迟差,如图6中的绿色条所示。最大延迟差为0.3 ns,提高了0.4 ns。

图6.单个设备上延迟差的分布。

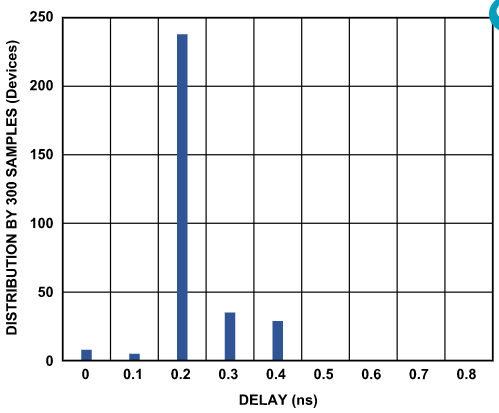

AD9361中的延迟补偿

基带处理器可能无法通过RX_D5 RX_D0来校正延迟差,或者根本无法进行延迟补偿。此问题的解决方案是在AD9361中使用Rx寄存器0x006和Tx寄存器0x007进行补偿,以调整RX_D5至RX_D0与DATA_CLK信号(或TX_D5至TX_D0和FB_CLK信号)之间的相对延迟,最小有效位(LSB)精度约为0.3 ns。请注意,此延迟会影响具有相同值的所有数据对。AD9361无法单独调整数据对的延迟。但是,这种补偿仍然使校准可行。图7显示了在AD300的寄存器0x006中校正9361 ps延迟时的结果。图7所示结果表明,延迟差主要分布在0.1 ns和0.4 ns之间,最大延迟降低到0.4 ns,时序为t圣+ 吨HT(在图3中)基带处理器的裕量更大(约1.4 ns),这保证了工艺和温度变化的可靠性。

图7.AD9361中延迟差与延迟校正的分布

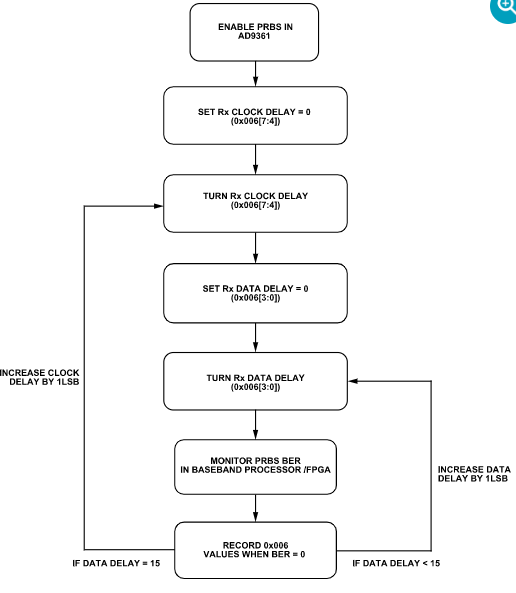

PRBS校准

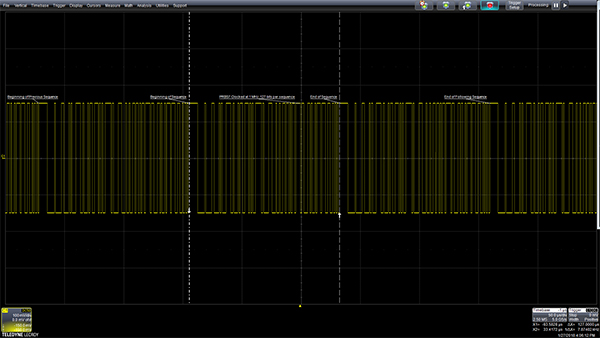

AD9361集成的PRBS发生器提供了一种确定需要多少延迟补偿的方法。该PRBS可以注入AD9361的接口,并传输到基带处理器。基带处理器收到此已知序列后,可以实现PRBS检查器来计算误码率(BER)。如果收到的 PRBS 上没有发生错误,则接口工作正常。否则,调整AD9361或基带处理器中的延迟补偿模块,直到误码率降至所需阈值以下。

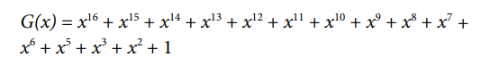

AD9361内置一个16级、14抽头PRBS发生器,使用16千-阶多项式如下式所示。

PRBS生成和多项式方程的详细描述参考AD9361寄存器映射,寄存器0x3F4。

按照图8所示的上述校准顺序,可以产生如表2所示的基质。在表 2 中,P 表示 PRBS 测试通过,F 表示失败。在此示例中,注册0x006的值可以是0x96、0xA7、0xB8、0xC9或0xDA。

图8.校准顺序。

| 寄存器 0x006[7:4] 位值 | 寄存器 0x006[3:0] 位值 | |||||||||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 一个 | b | c | d | e | f | |

| 0 | P | F | F | F | F | F | F | F | F | F | P | P | P | F | F | F |

| 1 | P | F | F | F | F | F | F | F | F | F | F | F | F | F | P | P |

| 2 | P | P | F | F | F | F | F | F | F | F | F | F | F | F | F | P |

| 3 | P | P | P | F | F | F | F | F | F | F | F | F | F | F | F | F |

| 4 | P | P | P | P | F | F | F | F | F | F | F | F | F | F | F | F |

| 5 | F | P | P | P | P | F | F | F | F | F | F | F | F | F | F | F |

| 6 | F | P | P | P | P | P | F | F | F | F | F | F | F | F | F | F |

| 7 | F | F | P | P | P | P | P | F | F | F | F | F | F | F | F | F |

| 8 | F | F | F | F | P | P | P | P | F | F | F | F | F | F | F | F |

| 9 | F | F | F | F | P | P | P2 | P | P | F | F | F | F | F | F | F |

| 一个 | F | F | F | F | F | P | P | P2 | P | P | F | F | F | F | F | F |

| b | F | F | F | F | F | F | P | P | P2 | P | P | F | F | F | F | F |

| c | F | F | F | F | F | F | F | P | P | P2 | P | P | F | F | F | F |

| d | F | F | F | F | F | F | F | F | P | P | P2 | P | P | F | F | F |

| e | F | F | F | F | F | F | F | F | F | P | P | P | P | P | F | F |

| f | F | F | F | F | F | F | F | F | F | F | P | P | P | P | P | F |

|

1P = PRBS 测试通过,F = PRBS 测试失败。 2延迟设置的最佳值。这些值在两个方向上至少有两个LSB(约0.6 ns)的保护裕量,这通常足以应对工艺变化和温度范围变化 |

||||||||||||||||

在寄存器0x006上为接收器(Rx)延迟选择适当的设置后,可以使用相同的方法和顺序在Tx LVDS路径上运行校准程序。这一次,在校准Tx LVDS路径时,可以在基带处理器中生成伪随机二进制序列,并传输到AD9361的Tx接口。在AD9361中,内部电路可以将TX_D5环路TX_D0到RX_D5到RX_D0路径,然后将数据传输回基带处理器,PRBS检查器与其原始序列进行比较,并确定如何调整寄存器0x007中的延迟,以实现与表2所示类似的矩阵。

结论

本文档介绍了LVDS路径延迟上的PRBS校准,以支持245.76 MHz数据时钟(最大带宽为56 MHz)。因此,当对Rx数据进行校准时,数据对的延迟变化显著改善至0.3 ns(基带处理器中的补偿)或0.4 ns(AD9361中的补偿)。

两种补偿使高速LVDS接口具有余量,以克

审核编辑:郭婷

-

收发器

+关注

关注

10文章

3794浏览量

110556 -

射频

+关注

关注

106文章

5944浏览量

172750 -

lvds

+关注

关注

2文章

1216浏览量

69109

发布评论请先 登录

如何使用PRBS和CMOS器件生成伪随机噪声和二进制序列

AD9361LVDS接口上的伪随机二进制序列校准

AD9361LVDS接口上的伪随机二进制序列校准

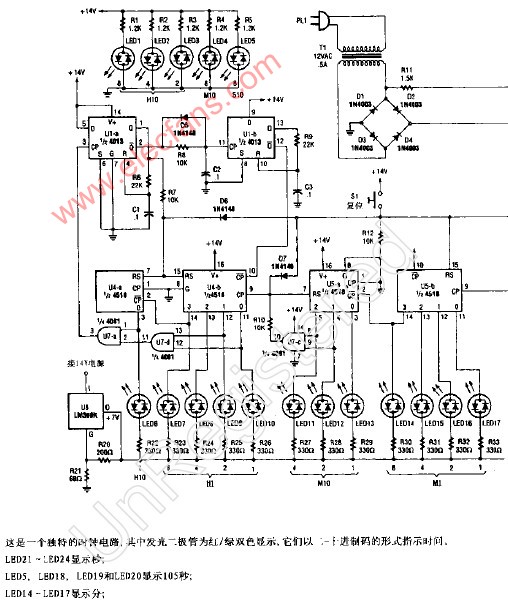

评论