基于硬件的安全性提供了针对网络攻击的强大保护,当实现加密功能的芯片使用时,物理不可克隆功能(PUF)技术可以进一步增强该级别的保护。本应用笔记讨论了一种新的PUF半导体解决方案,称为ChipDNA技术,该解决方案利用了MOSFET晶体管的随机模拟特性,MOSFET晶体管是CMOS IC的基本构建模块。在芯片层面,基于ChipDNA的PUF解决方案由一系列模拟电路元件构成,具有I-V特性固有的随机性,并根据实现芯片加密要求所需的位数进行调整。需要时,ChipDNA PUF 用于导出每个芯片的随机、唯一且可重复的二进制值,该值只能通过芯片加密块访问。一旦不再需要它,PUF 派生的密钥值就会立即擦除,并且不会以数字形式存在。这种 ChipDNA PUF 解决方案已证明具有高可靠性和适当的加密质量——这两个标准都使 PUF 输出能够用作加密密钥值。本应用笔记的类似版本最初发表在《嵌入式世界2018年会议论文集》中。

介绍

密码学提供了灵活有效的工具来应对嵌入式电子系统面临的无数潜在安全威胁。有多种硬件和软件方法可用于实现加密解决方案。通常理解,基于硬件的解决方案(即专用安全IC)是信任根的最有效表述,也是提供防止多种常见攻击的对策和保护的方法。

与嵌入式系统相关的宝贵资产面临着无情的威胁。例如,此类系统会遇到入侵,例如盗窃知识产权、引入恶意软件来破坏或破坏设备、未经授权访问敏感通信以及篡改从物联网端点生成的数据。可用的安全IC和加密解决方案可以解决这些威胁。但是,安全IC本身可能成为试图规避或破坏安全性的对手的攻击目标。

对安全 IC 的攻击

假设基于安全 IC 的保护解决方案,则攻击场景分为两类:非侵入性[1]和侵入性。

非侵入性攻击包括操作测量,有时与其他外部应用的刺激相结合,以获取加密密钥或其他敏感数据。此类工作的例子包括差分或简单的功率/电磁分析(DPA/SPA/DEMA/SEMA)或通过电压毛刺、极端热条件或激光和定时攻击诱发故障状态。虽然非侵入性攻击威胁在技术上很难解决,但已经建立了电路和算法对策,这些电路和算法对策已被证明可以有效地保护安全IC和敏感的存储数据免受损害。

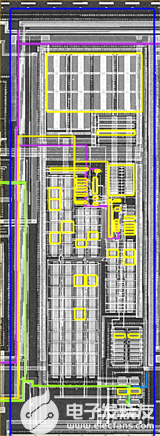

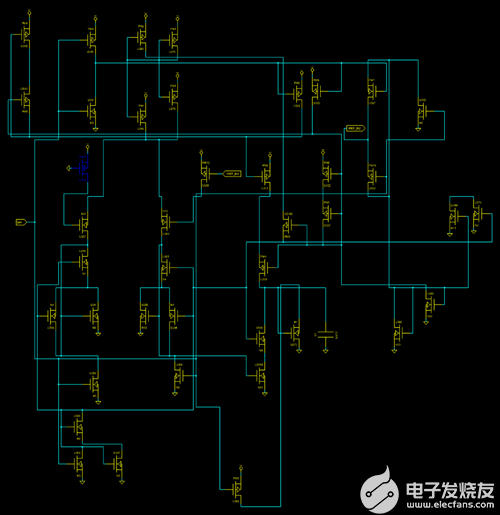

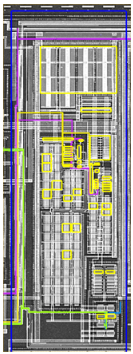

对安全IC的侵入性攻击包括直接芯片级电路探测、修改、反处理和逆向工程,其目的同样是通过获取密钥、禁用功能或将设计完全逆向工程到网表进行复制来破坏解决方案。技能集和所需工具比非侵入性场景更复杂,但它们确实存在,并且通常用于攻击保护高价值资产的安全 IC。例如,图1和图2是工具的输出示例,这些工具可用于侵入性攻击,首先对IC的一部分进行成像,然后从成像中提取网表和原理图。攻击者将对整个IC重复此过程,最终目标是获得一些见解以发起子电路攻击或生成数据库以复制IC

图1.用于原理图/网表提取的成像安全IC区域。

图2.用于对区域进行成像的工具的逻辑示意图输出。

与非侵入性情况一样,也有电路解决方案可用于对抗侵入性攻击。一个例子包括顶级芯片屏蔽,这些屏蔽被主动监控以发生篡改事件,并结合采取防御性反击的检测电路。然而,采用侵入性技术的攻击者的技能和装备迅速发展,历来是一个决定性击败的挑战。

PUF 技术如何应对侵入性攻击

物理不可克隆功能(PUF)技术已经出现,可提供针对入侵威胁的强大保护[2].PUF源自IC复杂多变的物理/电学特性。由于PUF依赖于随机物理因素(不可预测和不可控制),这些因素是原生存在的和/或在制造过程中偶然引入的,因此几乎不可能复制或克隆。PUF 技术原生为其关联的安全 IC 生成数字指纹,该指纹可用作唯一的密钥/机密,以支持加密算法和服务,包括加密/解密、身份验证和数字签名。

Maxim Integrated的PUF实现,称为ChipDNA技术,基于基本半导体MOSFET器件模拟特性的自然随机变化和失配。这种随机性源于氧化物变化、阈值电压的器件间不匹配和互连阻抗等因素。同样,晶圆制造过程通过不完善或不均匀的沉积和蚀刻步骤引入随机性。矛盾的是,半导体器件参数变化通常是IC设计人员在开发过程中面临的挑战,也是Maxim的PUF设计的基本基础。

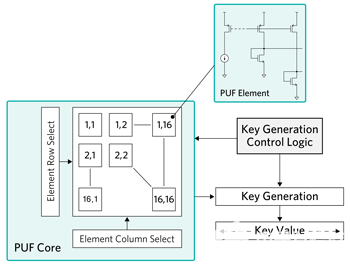

图3是Maxim的ChipDNA PUF架构的简化框图,示例密钥大小为128位。PUF 核心块中显示的是一个由 16 个 PUF 元件组成的 16x256 阵列,每个元件都是模拟结构。通过工厂调理,这256个元素组合成128对。在比较结构与结构时,由于前面描述的参数而存在随机I / V特性,并且通过对中每个元件的精密电路级比较来生成二进制1/0值。例如,元素 {2,1} 和 {14,16} 可以构成一对,并且比较每个元素的 I/V 特性以得出一个位值。对 128 对中的每一对重复此操作,以生成示例密钥大小的 128 位 PUF 密钥输出。对于较大的密钥大小要求,只需缩放ChipDNA PUF元件的数量即可。

图3.Maxim Integrated的ChipDNA PUF架构框图。

对于侵入性攻击,对 ChipDNA PUF 元件的任何探测或尝试模拟测量都会导致敏感的模拟电气特性因电容/电感/电阻负载等因素而发生变化。这就是为什么不可能通过侵入性测量提取任何关键数据的原因。此外,由于不完善的制造技术的统计性质,没有已知的方法可以从检查方法中识别任何关键信息。同样,即使了解ChipDNA PUF元件配对也不会揭示任何有关最终可以从PUF元件结构的模拟特性得出的关键值的信息。最后,PUF 密钥值仅在执行加密操作时以数字方式存在;此后,它会被立即擦除。这些ChipDNA PUF属性共同产生了一种对侵入性攻击高度免疫的解决方案。

PUF 可靠性和加密质量

从加密的角度来看,可靠性和随机性是 PUF 解决方案必须表现出的关键特征。要用作加密密钥或其根,PUF 输出必须具有 100% 的可靠性,这意味着 PUF 派生的密钥位值必须在一段时间内和所有操作条件下可重复。对于半导体器件,该评估使用JEDEC定义,经过行业验证的可靠性研究方法进行。这包括选择具有统计意义的设备样本集并将其置于环境和操作压力条件下,从而能够评估使用寿命的可靠性性能。这些应力包括高温工作寿命 (HTOL)、温度循环、封装和焊料回流影响、电压和温度漂移以及高度加速的温度/湿度应力测试 (HAST)。使用这些经过验证的方法进行可靠性鉴定研究,可以对设计在系统中使用期间的性能进行统计评估。例如,假设系统最终产品的设计寿命为10年,工作在-40°C至+85°C的环境中,电源可能会波动±10%。

与PUF解决方案同样重要的是对高性能加密质量的要求,其关键属性是随机性。低质量随机性可以通过可预测性弱点创建加密攻击漏洞。统计测试套件(包括 NIST SP 800-22)提供了一种经过行业验证的方法来测量 PUF 输出的随机性。针对测试套件的评估提供了多个指标,这些指标确定 PUF 输出是否与随机序列一致。为了具有统计意义,这些工具需要大型数据集进行分析(例如,20 kbit序列)。因此,大量 PUF 实例的输出是必需的,并用于评估。

芯片DNA的可靠性研究

对Maxim的ChipDNA PUF进行终身可靠性分析的结果证明了其功能。从根本上说,可靠性研究产生了了解PUF元素的数据,例如老化,温度/电压漂移,IC封装和PCB组装的转变。相对于两个PUF成对元件的时间零特性,可靠性研究后的成对元件消耗了大约7%的总裕量,以保持输出二进制值的稳定性。分析的最终输出是 ChipDNA PUF 密钥错误率 (KER) = 5ppb,其中 KER 定义为 PUF 产生的总密钥大小中的 1 位(例如,256 位)可以翻转产品的生命周期的概率。

ChipDNA PUF 的随机性评估依赖于 NIST 标准 SP 800-22 单比特、扑克、运行测试和长期运行测试的性能。这些测试套件评估输出数据是否与随机序列一致。四个测试中每个测试的评估结果都验证了在随机性方面的出色表现。

为了评估Maxim ChipDNA PUF解决方案对侵入性攻击和逆向工程的免疫力,由一家领先的美国公司[3]评估,该公司专门从事芯片级安全评估和IC逆向工程专业知识。在给定的评估时间范围内,ChipDNA解决方案没有受到损害,并且有一个定性的结论,即该解决方案“非常有效且能够抵抗物理逆向工程攻击”。

芯片DNA技术用例

ChipDNA PUF技术可以通过多种方式用于安全IC内的加密操作,例如:

在图 4 中,为了保护安全 IC 上存储的所有数据,ChipDNA PUF 派生密钥用于根据需要使用 AES 等算法加密/解密数据。如果侵入性攻击获得了对任何非易失性存储器 (NVM) 数据的访问权限,则该数据将毫无用处,因为它已加密,攻击者无法获取基于 PUF 的解密密钥。在本例中,数据的加密/解密仅根据需要在片上完成。PUF 密钥加密数据不会从 IC 传输。

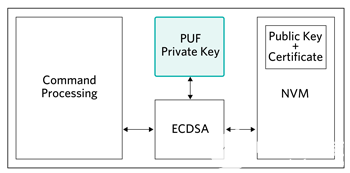

图 5 显示了使用 ChipDNA PUF 作为 ECDSA 签名操作的唯一私钥。在这种情况下,设备将从 PUF 私钥计算自己的相应公钥,并且在最终使用部署之前,证书颁发机构将在 NVM 中安装证书。

图5.使用 PUF 作为私钥的 ECDSA 签名。

在图6中,ChipDNA PUF私钥是安全IC的根私钥,与终端系统结合使用,与安全IC建立“信任根”,用于后续服务。

图6.PUF 作为信任锚私钥。

Maxim基于ChipDNA的商用安全IC

Maxim目前提供两款基于ChipDNA PUF的安全IC:DS28E38采用非对称ECDSA认证,DS28E50采用对称SHA3认证。

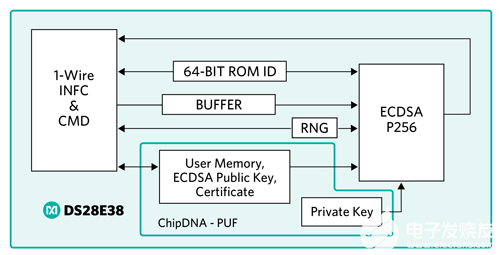

DS28E38是一款ECDSA认证器,利用公司的ChipDNA PUF输出作为关键内容,对所有器件存储的数据进行加密保护。或者,在用户控制下,ChipDNA技术被用作ECDSA签名操作的私钥。该器件提供一组核心加密工具,这些工具源自集成模块,包括非对称 (ECC-P256) 硬件引擎、符合 FIPS/NIST 标准的真随机数发生器 (TRNG)、2Kb 安全 EEPROM、仅递减计数器和唯一的 64 位 ROM 标识号 (ROM ID)。ECC 公钥/私钥功能从 NIST 定义的 P-256 曲线运行,以提供符合 FIPS 186 的 ECDSA 签名生成功能。DS28E38的框图如图7所示。

图7.Maxim基于ChipDNA PUF的ECDSA认证器框图。

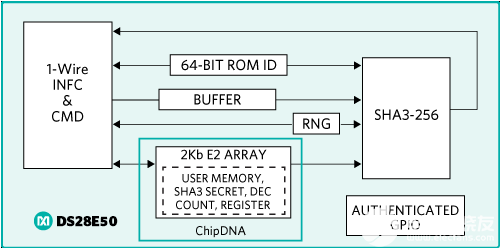

DS28E50是一款SHA3认证器,与DS28E38一样,利用ChipDNA PUF输出作为加密/解密密钥来保护所有器件存储的数据。该器件提供符合 FIPS-202 标准的双向 SHA3-256 身份验证、符合 FIPS/NIST 标准的 TRNG、2Kb 安全 EEPROM、仅递减计数器、安全 GPIO 和独特的 64 位 ROMID。DS28E50的框图如图8所示。

图8.Maxim基于ChipDNA PUF的SHA3认证器框图

总结

密码学保护嵌入式系统内的电子资产。通过在嵌入式设计中使用具有加密功能的安全IC,设计人员无需成为密码学专家即可获得强大的设计保护。然而,安全IC本身可能成为日益复杂的网络犯罪分子的攻击目标。基于其固有的品质,ChipDNA PUF技术对逆向工程方法具有高度免疫力,为侵入性攻击提供了决定性的对策。

审核编辑:郭婷

-

MOSFET

+关注

关注

141文章

6569浏览量

210134 -

半导体

+关注

关注

328文章

24506浏览量

202126 -

晶体管

+关注

关注

76文章

9054浏览量

135212

发布评论请先 登录

相关推荐

芯片DNA如何物理不可克隆的功能技术保护嵌入式系统

芯片DNA如何物理不可克隆的功能技术保护嵌入式系统

评论