“开关噪声-EMC基础篇”前后共有21篇文章,本文是最后一篇。从“EMC基础”知识开始,以开关电源为前提分别介绍了“降噪对策(步骤与概要)”、“使用电容器降低噪声”、“使用电感降低噪声”、“其他降噪对策”相关的基础内容。本文将对各篇文章的关键要点做最终总结。

<EMC基础>

关键要点

・EMC(电磁兼容性)是指兼备EMI和EMS两方面的性能。

・EMI(电磁干扰)是指因辐射/发射(Emission)电磁波而对环境产生的干扰。

・EMS(电磁敏感性)是指对电磁波干扰(EMI)的耐受性/抗扰度(Immunity)。

▶频谱基础

关键要点

・当频率升高时,频谱振幅整体增加。

・上升/下降延迟时,进入-40dB/dec衰减时的频率降低,频谱的振幅衰减。

・Duty变更时,虽然会产生偶次谐波,但对谱峰无影响。基波频谱衰减。

・仅上升延迟时,tr分量从更低的频率开始衰减。

关键要点

・电磁干扰EMI大致可分为“传导噪声”和“辐射噪声”两种。

・传导噪声可分为差模(常模)噪声和共模噪声两类。

・关于辐射噪声,差模噪声的线缆环路面积、共模噪声的线长是非常重要的因素。

・注意;即使条件相同,共模噪声带来的辐射远远大于差模噪声。

▶何谓串扰

▶开关电源产生的噪声

<降噪对策>

关键要点

・随着开发进程的推进,可使用的降噪对策技术和手段越来越有限,对策成本也越来越高。

・在产品开发的初期阶段,预先进行充分探讨与评估,可以从容有效地采取降噪对策。

・掌握噪声的种类和性质,并针对不同的噪声采取不同的有效对策是非常重要的。

・降噪对策按照“把握频率成分→把握产生源和传导路径→强化GND→增加降噪部件”的步骤进行。

关键要点

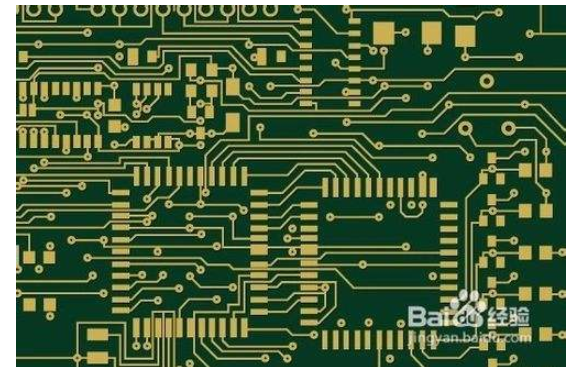

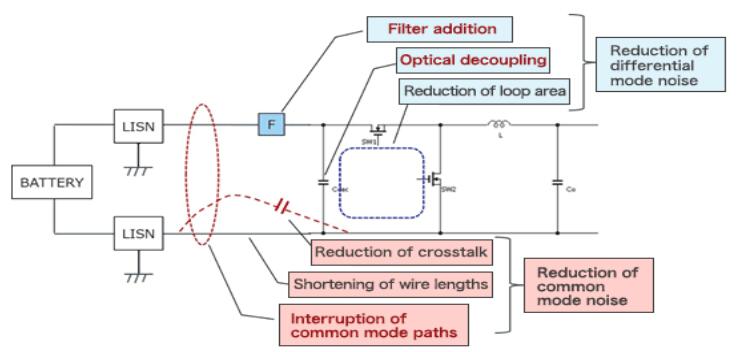

・要想降低差模噪声,可在电路板上缩小大电流路径的环路面积,并增加最优解耦和输入滤波器。

・尽可能地抑制噪声的发生源–差模噪声是非常重要的,也关系到降低共模噪声。

・要想降低共模噪声,可缩短布线,抑制串扰,切断(滤波)共模路径。

<使用电容器降低噪声>

关键要点

・降噪用电容器的选型需要根据阻抗的频率特性进行(而非容值)。

・容值和ESL越小,谐振频率越高,高频区域的阻抗越低。

・容值越大,容性区域的阻抗越低。

・ESR越小,谐振频率的阻抗越低。

・ESL越小,感性区域的阻抗越低。

关键要点

・通过降低目标噪声频率的阻抗来降低噪声幅度。

・降噪用电容器的选型需要根据阻抗的频率特性进行(而非容值)。

关键要点

・去耦电容的有效使用方法有两个要点:①使用多个电容,②降低电容的ESL。

・使用多个电容时,容值相同时和不同时的效果不同。

关键要点

・去耦电容的有效使用方法有两个要点:①使用多个电容,②降低电容的ESL。

・通过降低电容的ESL,可改善高频特性,并可更有效地降低高频噪声。

・有的电容虽然容值相同,但因尺寸和结构不同而ESL更小。

关键要点

・理解Q与频率-阻抗特性之间的关系,并根据目的区分Q的差异。

・高Q电容窄带阻抗急剧下降。低Q电容在较宽频段相对平缓下降。

・PCB图形的热风焊盘等会增加电感分量,使谐振频率向低频端移动。

・探讨对策时的试装,如果不按照现实的修改实际安装,很可能在修改后的PCB板上无法获得探讨时的效果。

・电容量变化率大时,谐振频率会变化,无法获得目标频率理想的噪声消除效果。

・在温度条件和变动较大的严苛应用中,可以探讨使用具有CH、C0G特性的温度特性优异的电容。

<使用电感降低噪声>

关键要点

・电感在谐振频率之前呈现感性特性(阻抗随频率升高而增加)。

・电感在谐振频率之后呈现容性特性(阻抗随频率升高而减小)。

・在比谐振频率高的频段,电感不发挥作为电感的作用。

・电感值L变小时,电感的谐振频率会升高。

・电感的谐振点阻抗受寄生电阻分量的限制。

关键要点

・用于降噪对策的电感,大致可以分为绕组型电感构成的滤波器和利用铁氧体磁珠进行热转换两种。

・铁氧体磁珠与普通电感相比,具有电阻分量R较大、Q值较低的特性。

・普通的电感可容许较大的直流叠加电流,只要在其范围内,阻抗不怎么受直流电流的影响。

・铁氧体磁珠对于直流电流容易饱和,饱和会导致电感值下降,谐振点向高频段转移。

・普通电感构成的滤波器,可选电感值的范围较宽。

・铁氧体磁珠的Q值较低,因此在较宽频率范围内具有有效的降噪效果。

关键要点

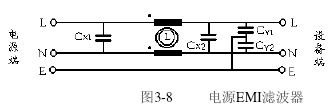

・使用共模滤波器消除对共模噪声。

・共模滤波器是利用自感作用来阻止共模电流通过的滤波器。

关键要点

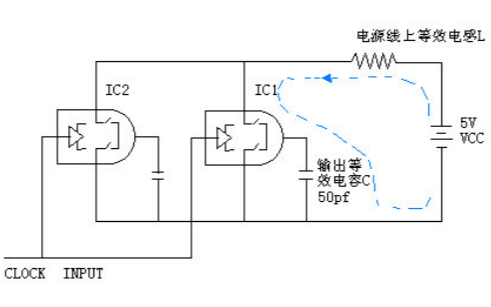

・有些PCB板布线布局,会因串扰而导致滤波效果下降。

・Π型滤波器的电容的GND的某些设置方法可能会带来地线反弹噪声。

・优化PCB板布线布局可避免这些问题。

<其他降噪对策>

关键要点

・RC缓冲电路可通过电阻将寄生电容、寄生电感等产生的尖峰电压转换为热,从而降低尖峰电压。

・增加缓冲电路可能会导致效率降低,因此需要探讨噪声水平和效率之间的平衡点。

・电阻是将噪声电压转换为热,因此需要注意电阻的容许损耗。

EMC基础-总结

EMC基础-总结

评论