本文介绍DS3112多路复用成帧器如何从高速多路复用信号中恢复低速时钟信号,以用于器件的三种多路复用工作模式。第一种工作模式是在M13和C位奇偶校验模式下从DS3信号中恢复28个DS1时钟信号。第二种模式是从E13模式下的E3信号中恢复16个E1时钟信号。第三种模式是在G.747模式下从DS3信号中恢复21个E1时钟信号。恢复低速时钟时,需要注意的是,高速信号中存在的实际数据会影响恢复过程。因此,当术语“信号”单独使用时,它指的是组合的时钟、数据和使能信号。将术语“时钟”、“数据”或“启用”与信号结合使用的任何内容均指单个信号组件。

用于M13和C位奇偶校验模式的DS1时钟恢复

从DS3信号中恢复28个独立的DS1时钟是一个复杂的三阶段过程。

第一级,即M23级,将DS3信号解复用为7个独立的DS2信号。不是恢复单个DS2时钟,而是创建DS2使能。七个DS2使能中的每一个都处于活动状态,每个DS3帧的DS3时钟周期为84 x 7 +(84或83)。恢复最后的84或83个DS3时钟周期的决定基于DS2填充位控制。

第二级是M12级,它将7个DS2信号中的每一个解复用为4个DS1信号,总共28个DS1信号。与 M23 级一样,M12 级不会恢复单个 DS1 时钟,而是创建 DS1 使能。四个 DS1 使能中的每一个都处于活动状态,持续 48 x 5 +(48 或 47)DS2 使能周期。恢复最后 48 或 47 DS2 使能周期的决定基于 DS1 填充位控制。

第三个也是最后一个阶段是FIFO级,它实际上重新创建各个DS1时钟。每个DS1时钟都是通过将DS3时钟(HRCLK)除以28或29来创建的。除数的选择基于当前存储在FIFO中的数据量。FIFO使用DS1使能将数据写入FIFO,使用DS1时钟(LRCLKx)从FIFO读取数据。正确的DS1时钟速率由FIFO恢复,试图将FIFO中的数据量保持在半满标记的中心。如果数据量超过半满标记,则选择“除以 28”。如果数据量低于半满标记,则选择“除以 29”。时钟恢复机制的完整示意图如图1所示。

图1.M13 和 C 位奇偶校验模式。

E13 模式的 E1 时钟恢复

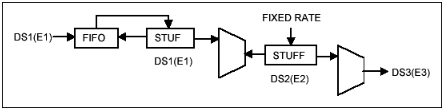

从E3信号中恢复16个单独的E1时钟也是一个复杂的三阶段过程。

第一级是E23级,它将E3信号解复用为四个E2信号。不是恢复单个 E2 时钟,而是创建 E2 启用。四个 E2 使能中的每一个都处于活动状态,每个 E3 帧的 E3 时钟周期为 93 + 95 x 2 +(95 或 94)。恢复最后 95 或 94 个 E3 时钟周期的决定基于 E2 填充位控件。

第二级是E12级,它将四个E2信号中的每一个解复用为四个E1信号,总共16个E1信号。与 E23 级一样,E12 级不会恢复单个 E1 时钟,而是创建 E1 使能。四个 E1 使能中的每一个都处于活动状态,持续 50 + 52 x 2 +(52 或 51)个 E2 使能周期。恢复最后 52 或 51 个 E2 启用周期的决定基于 E1 填充位控件。

第三级,也是最后一级,是FIFO级,它实际上重新创建了各个E1时钟。每个 E1 时钟都是通过将 E3 时钟 (HRCLK) 除以 16 或 17 来创建的。除数的选择基于当前存储在FIFO中的数据量。FIFO使用E1使能设备将数据写入FIFO,并使用E1时钟(LRCLKx)从FIFO读取数据。正确的E1时钟速率由FIFO恢复,FIFO试图将FIFO中的数据量保持在半满标记的中心。如果数据量超过半满标记,则选择“除以 16”。如果数据量低于半满标记,则选择“除以 17”。时钟恢复机制的完整示意图如图2所示。

图2.E13 模式。

G.747 模式的 E1 时钟恢复

从DS3信号中恢复21个独立的E1时钟也是一个复杂的三阶段过程。

第一级是M23级,它将DS3信号解复用为7个DS2信号。不是恢复单个DS2时钟,而是创建DS2使能。七个DS2使能中的每一个都处于活动状态,每个DS3帧的DS3时钟周期为84 x 7 +(84或83)。恢复最后的84或83个DS3时钟周期的决定基于DS2填充位控制。

第二级是G.747级,它将7个DS2信号中的每一个解复用为3个E1信号,总共21个E1信号。与 M23 级一样,G.747 级不会恢复单个 E1 时钟,而是创建 E1 使能。三个 E1 使能中的每一个都处于活动状态,持续 53 + 55 x 3 +(55 或 54)DS2 使能周期。恢复最后 55 或 54 DS2 使能周期的决定基于 E1 填充位控件。

第三个也是最后一个阶段是FIFO阶段,它实际上重新创建各个E1时钟。每个 E1 时钟都是通过将 DS3 时钟 (HRCLK) 除以 21 或 22 来创建的。除数的选择基于当前存储在FIFO中的数据量。FIFO使用E1使能设备将数据写入FIFO,并使用E1时钟(LRCLKx)从FIFO读取数据。正确的E1时钟速率由FIFO恢复,FIFO试图将FIFO中的数据量保持在半满标记的中心。如果数据量超过半满标记,则选择“除以 21”。如果数据量低于半满标记,则选择“除以 22”。时钟恢复机制的完整示意图如图3所示。

图3.G.747 模式。

审核编辑:郭婷

-

fifo

+关注

关注

3文章

406浏览量

45496 -

时钟

+关注

关注

11文章

1953浏览量

134552

发布评论请先 登录

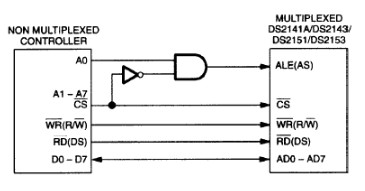

DS3 / E3 / STS成帧器设计用于多标准网络和传输系统

DS3150 业内首款单端口T3/E3 LIU,集成了抖动衰

DS3112 LRCLKx Low Speed Clock

Bit Error Rate Testing the DS3

DS3112 Clock Rates and Frequen

DS3112 接口 - 电信

DS3112 DS3/E3多路复用成帧器如何恢复低速时钟信号

DS3112 DS3/E3多路复用成帧器如何恢复低速时钟信号

评论