作为使用PAL、GAL或CPLD器件实现非易失性门控功能的替代方案,这些电路使用串行接口控制的数字电位器(MAX5427或MAX5527)存储门控信号(模块或发送)。

下面介绍了通常由 PAL、GAL 或 CPLD 器件实现的非易失性门控功能的简单替代方案。要“选通”逻辑信号(以阻止或传输它),通常使用逻辑门(如AND门),并使用门的第二个输入来定义门是阻塞还是传输施加的信号(图1)。由于逻辑门执行即时布尔运算,因此它们的运算是组合的,没有内存。

图1.AND 门用于门控信号。

如果需要对门进行编程,该门在系统启动后应始终阻塞或传输信号,则必须将“发送/阻塞”逻辑状态存储在某种形式的非易失性存储器中。有两种基本方法可用于存储此类逻辑状态。第一种涉及微控制器与非易失性存储器(如EEPROM)的组合。如果系统可以等到微控制器从存储器读取逻辑状态并将其应用于硬件引脚(通常通过GPIO引脚),则此方法适用。但是,某些系统要求在启动时存在发送/块信号。对于这些,从内存读取延迟是不可接受的。

第二种方法适用于没有μC的系统,或者无法等待μC在启动时从存储器读取的系统,它将逻辑状态存储在器件中,使其在上电时立即可用。用于此目的的典型可编程逻辑器件是PAL、GAL或CPLD,它们将门控功能与可编程非易失性存储器相结合。然而,这些器件提供的不仅仅是存储器门控,对于只需要几个这样的门的系统来说,这些器件可能过于合格。此外,它们的封装相对较大,以适应它们提供的许多逻辑 I/O 引脚。

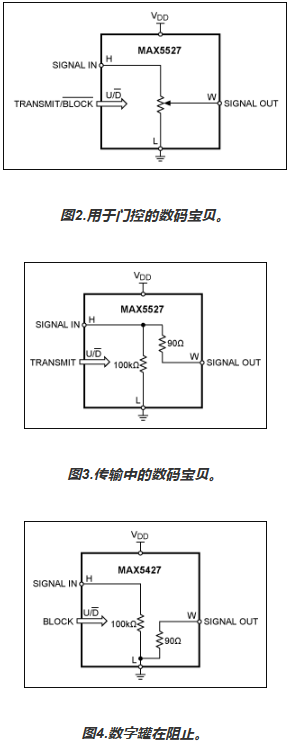

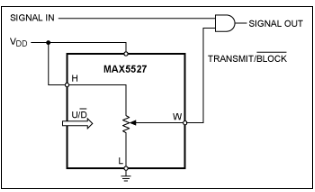

如果只需要几个非易失性栅极,请考虑使用模拟和混合信号系统中常见的元件——数字电位计或DigiPot(图2)。将电阻串的L端接地,并将信号路由到电阻串的H端。然后,游标输出短路至地以进行阻塞,或连接到输入信号进行传输(图3和图4)。这些连接仅对 DigiPot 进行编程,使其处于 N 个可能状态中的两种:D∈[1,N],其中 N = 抽头次数。

您可以在电路板或系统测试期间通过其串行接口对 DigiPot 进行编程。在某些DigiPots上找到的上/下接口适用于此目的。选择非易失性DigiPot时,应考虑以下标准:

DigiPots 通常有 32 个或更多水龙头(至少需要两个)。DigiPot游标具有与内部开关相关的电阻,应尽可能小,以避免开关信号失真。典型游标电阻为100Ω至1kΩ(MAX5527游标电阻测量值低至90Ω)。

由于 DigiPot 游标的电阻会随着电源电压的增加而减小,因此您应该为 DigiPot 选择高电源电压。

为了最大限度地减少信号源的负载,并且不限制DigiPot的信号带宽,您应该选择具有高端端到端电阻的DigiPot。100kΩ对于许多应用都是可以接受的。

如果门的状态必须在非易失性存储器中编程,请选择非易失性DigiPot。一些DigiPot具有OTP(一次性编程)功能,可让您一劳永逸地保存游标的设置。OTP 适用于您不希望以后对门控功能进行更改的情况。必须存储状态的门数决定了 DigiPot 的数量,每个包以 1 到 6 个(或更多)的数组形式提供。

DigiPot带宽决定了通过DigiPot传输的信号的最大数据速率。如果这些外加逻辑信号的开关速率对于可用的DigiPot来说太高,则可以使用传统的(高速)逻辑门,其发射/块输入由DigiPot控制(图5)。

图5.高速信号的非易失性选通。

审核编辑:郭婷

-

cpld

+关注

关注

32文章

1259浏览量

173289 -

存储器

+关注

关注

39文章

7714浏览量

170827 -

电位器

+关注

关注

14文章

1026浏览量

68807

发布评论请先 登录

TPL1401数字电位器易失性和非易失性的区别是什么?

非易失性MRAM的基础知识汇总

非易失性MRAM基础知识汇总

求助,如何使用非易失性密钥生成CMAC?

非易失性内存有写入限制吗?

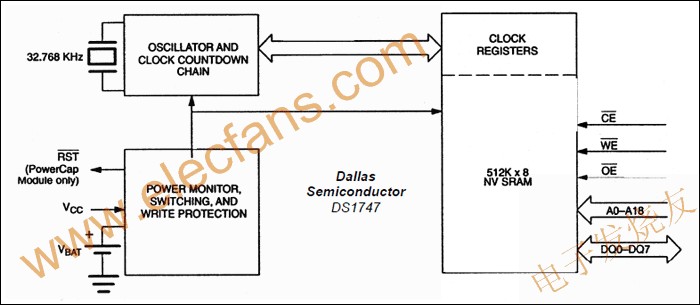

非易失性SRAM DS1747

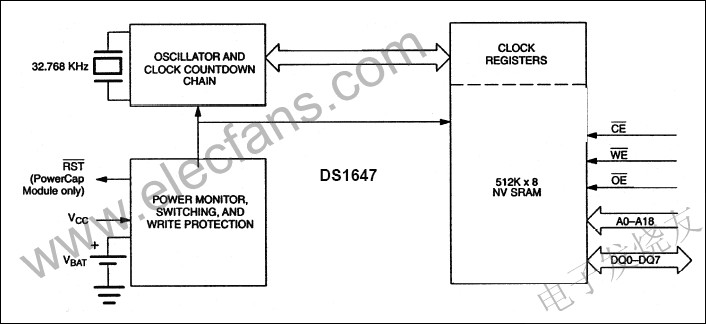

DS1647为512k x 8非易失性静态RAM

简单的非易失性门控

简单的非易失性门控

评论