ADI最新一代高速DAC具有出色的相位噪声,可在下一代低相位噪声、快速跳频捷变RF/微波频率合成器中实现尺寸、重量、功耗/性能和成本优势。一个挑战是,为了实现这种DAC功能,固定DAC采样时钟必须具有非常低的SSB相位噪声,这超出了主流宽带VCO PLL的能力。本文提供了一种采用模拟鉴相器(PD)的方法,与传统的相位/频率鉴相器频率合成器相比,该方法可将环内相位噪声性能提高10 dB至20 dB。为了满足最苛刻的相位噪声系统要求,建议的固定时钟实现方案是使用模拟PLL锁定的介质谐振器振荡器(DRO)。其它更常规的例子是采用市售的MMIC VCO提供的。本文解释了基于DAC的粗/细混频器微波合成器的优势,并提供了框图、测量的相位噪声结果和应用电路,以便感兴趣的工程师可以在实验室中试用。

介绍

航空航天与国防(ADEF)社区对相位噪声有着合理的痴迷。例如,雷达、电子战(EW)和大量其他应用需要快速跳频频率合成器和激励器提供一流的相位噪声性能。这些频率功能模块通常设置关键系统性能,例如雷达杂波衰减,并用于更大的频率转换、调谐器和调制方案。ADI公司最新一代高速DAC具有极低的加性相位噪声,实现了简化敏捷频率生成架构的长期梦想。向基于 DAC 的频率合成的演进可实现更小的尺寸、重量、功耗和成本 (SWaP-C) 解决方案,取代更大、更昂贵的信号链。然而,为了实现潜在的相位噪声,系统设计人员不能只使用任何旧的采样时钟源方案。本文介绍在实现采样时钟以获得最佳DAC相位噪声时的相位噪声考虑因素和权衡。更进一步,本文探讨了一种在Ku波段至Ka波段范围内实现宽带快速跳频频率合成器的低相位噪声方法。提供应用电路框图和测量数据,以便设计人员可以在工作台上复制实验数据,并在设计中利用该方法。

电子战和雷达中的SSB相位噪声影响

ADEF传感系统需要在恶劣的电磁环境中以时间关键的方式拦截不希望被检测到的敌方目标的微小信号或回波。瞬时无杂散动态范围(SFDR)是一个品质因数,通常用于表示接收系统在存在大阻塞信号的情况下对小信号的检测能力。SFDR以IMD2或IMD3和本底噪声表示,本底噪声假定是均匀的,即从任何载波相位噪声肩上充分偏移,以避免频率偏移依赖性使方程过于复杂。这是一个可接受的假设,比如说,距离载波10 MHz。然而,电子战和雷达应用需要在这个10 MHz偏移区域内更靠近载波的位置运行。因此,SFDR中没有明确捕获的一个重要方面是,在不埋在载波噪声肩中的情况下,可以保持多近的发射载波动态范围。该噪声肩是单边带(SSB)相位噪声,表示为载波频率偏移的函数:L(f)。

通信和卫星通信系统可能更关心单个集成均方根抖动数,该抖动数将相位噪声肩负中的总噪声积分在目标偏移上,而大多数雷达和电子战设计人员更关心载波特定频率偏移处的点SSB相位噪声包络。通常,这需要尽可能低,特别是在1 kHz至1 MHz范围内的多普勒偏移时。频率合成器设计人员面临的挑战是,这个关键任务区域通常是与锁相环(PLL)噪声结构相关的高相位噪声平台期。最小化该区域的噪声贡献是本文的主要目标。

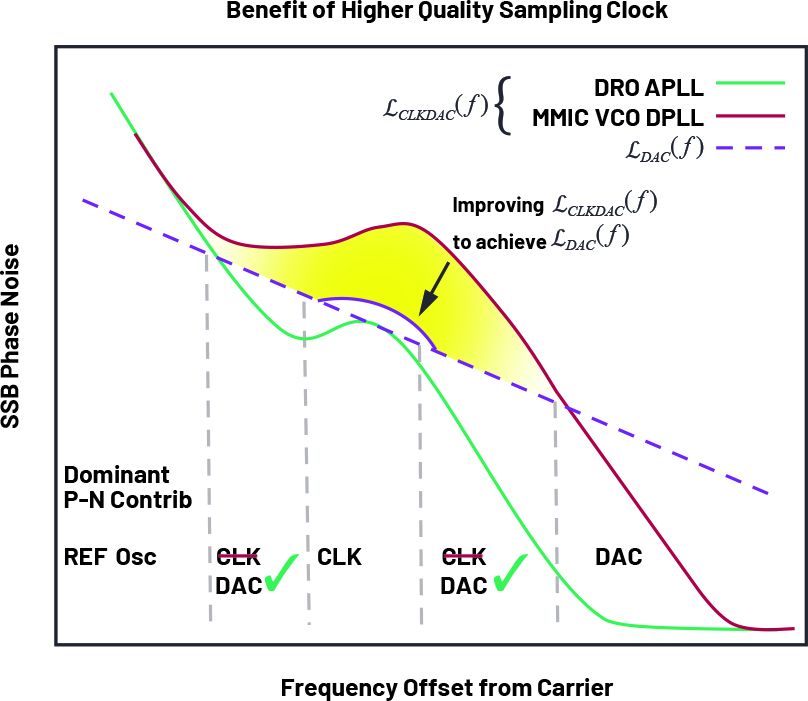

如果本文有一个要点,请记住,大多数雷达和电子战系统理想情况下希望采样时钟SSB相位噪声馈送到DAC以下~10 dB,允许DAC设置系统的相位本底噪声,而不是时钟!在实践中,我们将看到这是非常困难的。这证明了ADI公司的DAC相位噪声性能已经变得多么出色,以及基于DAC的合成器具有多么大的变革性。

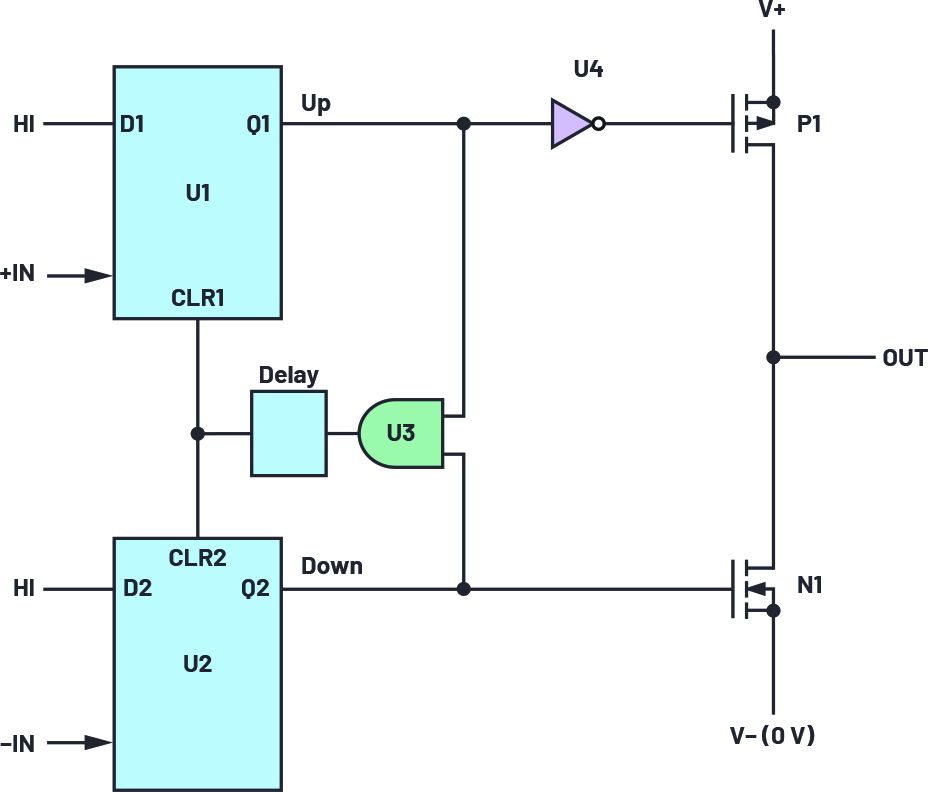

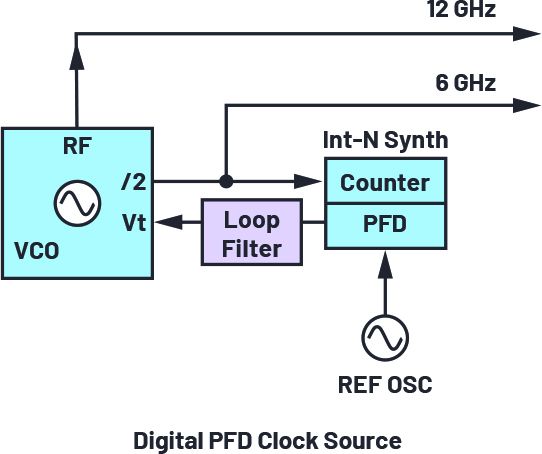

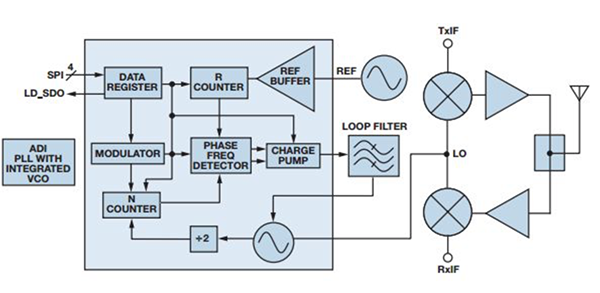

在整个讨论中,DPLL 通常是指采用有源相位/频率检测器 (PFD) 和分频器方案的任何集成 PLL 或频率合成器芯片。图1所示为经典数字PFD。

图1.经典的数字相位/频率检测器(PFD)。

APLL是指采用无源混频器作为鉴相器(PD)。需要明确的是,SSB相位噪声适用性对每个人来说意味着不同的东西,这取决于特定的任务要求和应用用例。多倍频程微波调谐、可编程性、易用性和低SWaP-C是宽带MMIC PLL-VCO合成器的现代优势。对于本文未介绍的大多数宽带调谐频率合成器应用,ADI的集成PLL-VCO频率合成器是最佳选择。我们只考虑DAC固定采样时钟的这个特定用例。例如,表 1 中使用的描述符旨在传达与此利基用例相关的比较性能。

现在有什么不同?

过去,使用真实中频实现基于DAC的高速合成的障碍是DAC的采样速率相对较低(即100 MSPS)和低模拟频率带宽(即250 MHz)。在使用较旧的DAC时,低IF使转换变得困难,并迫使一些笨重的,也许是不可能的RF滤波器。另一种选择,倍频,是不切实际的,因为所需的高乘法因子(称为N)转化为DAC加性相位噪声L代数转换器(f) 过高,特别是在地板上。提醒从F1上变频到F2时相干频率转换的影响:

换言之,ADI的较低采样速率DAC加成相位噪声很好,但它的直接载波频率太低,无法在低SWaP-C下实际转换为微波范围。

快进到今天,游戏已经改变。DAC采样速率、模拟带宽和由此产生的直接实际中频频率能力已增加到多GHz,加性相位噪声L代数转换器(f) 仍然非常出色,因此我们终于有了一款多功能构建模块,为实现低 SWaP、微波、宽带、快速调谐频率合成器开辟了各种新选择。

使用高速DAC的宽带微波频率合成器

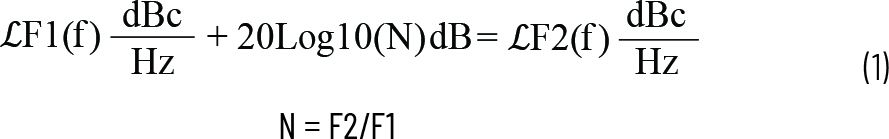

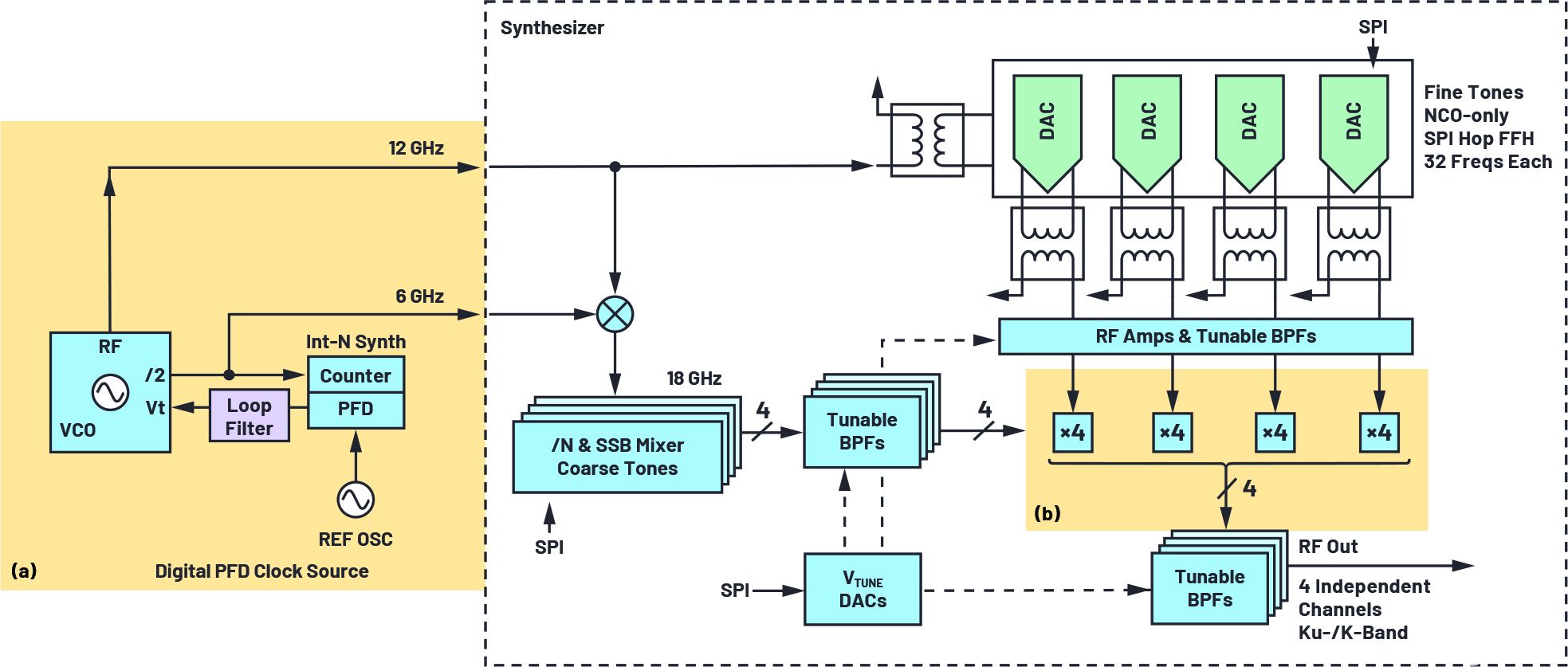

图2是我们在此提及的基于DAC的频率合成器的基本描述。每个功能块在与载波的不同偏移处对整体相位噪声的贡献略有不同。本次讨论的中心点是如何设计每个模块,以使出色的DAC添加剂(也称为残差)相位噪声能力L代数转换器(f) 设置系统相位噪声。我们会发现这不是微不足道的。

ℒ代数转换器(f) 加性相位噪声由多个因素组成,例如器件 1/f 噪声和随机模式等实现技术。电源相位噪声下降是一个臭名昭著的妖怪,谨慎的低噪声LDO实现至关重要。

参考振荡器 F裁判是频率合成器将被锁定的系统相位参考信号,通常在100 MHz范围内。ℒ裁判(f) 是绝对源相位噪声,它将频率合成器相位噪声设置为最接近的偏移,通常为 <1 kHz。使用SWaP-C平衡参考相位噪声性能和频率是一项重要的系统权衡:如果参考相位噪声不足,则下游相位噪声的恢复介于不可能和非常痛苦之间。不要在参考时钟上偷工减料。

固定频率模块是锁相环 (PLL) 所在的位置,锁相环将本地 RF 电压控制源 (RF 源) 锁定到频率参考。射频源绝对相位噪声的选择L射频源(f)是与SWaP-C权衡的另一个权衡,SWaP-C设置肩部与本底噪声相遇处的远偏移相位噪声。PLL技术是一种加性相位噪声贡献者L锁 相 环(f) 确定临界中间偏移平台(通常为 1 kHz 至 1 MHz)处的相位噪声。PLL有源环路滤波器使用的运算放大器具有重要的噪声贡献,因此归入这一类。这个中间偏移SSB相位噪声区域对L 的影响最大射频发展委员会(f)并且经常决定合成器任务的适用性。本讨论的第一部分侧重于最小化采样时钟相位噪声L中科达克(f) 允许DAC相位噪声L代数转换器(f) 支配L射频发展委员会(f)。

调谐发生器模块是加性相位噪声贡献者L根(f) 将DAC RF输出与一组固定频率与绝对相位噪声L 混合粗(f) 上变频为宽带捷变射频输出。本讨论的第二部分侧重于最小化相位噪声L的技术外(f) 和杂散,一旦你有你的DAC输出,需要将其转换为更高的微波频段。

图2.基于DAC的宽带频率合成和相位噪声贡献因素框图。

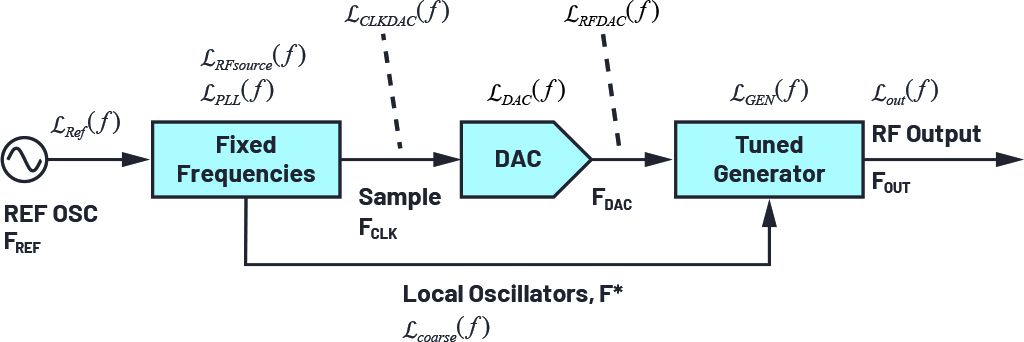

图3.相位噪声对整个DAC时钟源相位噪声的贡献。

图4.您需要较低相位噪声采样时钟的原因。

总结图2、图3和图4中的重要相位噪声关系:

关键目标是 L代数转换器(f) 设定 L射频发展委员会(f),L的捐款尽可能少中科达克(f)。

ℒ外(f < 1 kHz) 为 L裁判(f < 1 kHz) + 20LogN (N = 最终/参考频率比)。

ℒ中科达克(f > 1 kHz) 高度依赖于我们选择如何实现 L射频源(f)和L锁 相 环(f). L裁判(f) 本底噪声也将在这里发挥作用。

ℒ外(f > 1 kHz)取决于上述因素,以及我们如何选择上变频L射频发展委员会 (f > 1 kHz)。建议使用 L 的方法粗(f < 1 kHz)。

新的DAC优势,新的时钟挑战

我的一位同事引用了悲伤守恒的自然法则,当传统的信号链被重新吸吮以支持较低的SWaP-C进步时。该定律在这里适用,因为我们只需要旧SWaP-C的一小部分来执行基于DAC的调谐发生器功能块(悲伤减少),但固定频率源变得更加微妙(悲伤增加)。由于DAC的加性相位噪声非常低(这是一件好事,这也是本文的原因),并且由于采样时钟现在相当高,为12 GSPS(这也是一件好事,允许可以合理滤除真正的IF),采样时钟源所需的SSB相位噪声迫使我们考虑更复杂的时钟源解决方案。换言之,使用MMIC VCO-PLL不足以实现DAC加性相位噪声潜力。

我们首先考虑图2中参考振荡器、固定频率块和DAC的相互作用。固定频率模块由锁相环中的RF压控振荡器(VCO)组成,该锁相环将RF源锁定到参考振荡器。锁相环由一个分频器或转换器、PFD和采用运算放大器的有源环路滤波器组成。

在以后的讨论中比较了三个不同的实现示例:

| 描述 | 射频 Osc | PD/PFD |

SSB 相位 噪声 |

SWaP-C |

易用性 |

| 毫米式 VCO DPPL | 多媒体视频 | 主动式聚苯乙烯 | 好 | 最好 | 最好 |

| MMIC VCO APLL | 多媒体视频 |

无源 混频器PD |

更好 | 更好 |

穷 |

| 德罗阿普尔 | 刚果民主共和国 |

无源 混频器PD |

最好 | 穷 |

穷 |

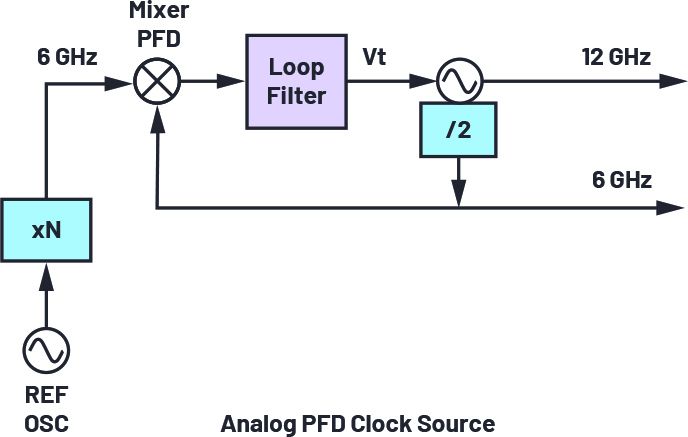

旧的又是新的

模拟鉴相器比污垢更古老,是现代集成有源相位/频率检测器(PFD)合成器的祖父。在绝大多数现代宽带频率合成器应用中,它们已经过时,考虑到集成频率合成器IC的进步,这是理所当然的。当需要在最佳SWaP-C下使用宽带调谐VCO-PLL时,模拟PD是一个糟糕的选择。那么,为什么在此DAC时钟用例中选择模拟PD?这与无源模拟PD的出色附加相位噪声有关。PD比较两个输入频率,并输出代表相位差的拍频信号。当比较频率正交或锁定时,PD输出0 V DC信号。在采用有源PFD的整数N分频和小数N分频频率合成器中,两个比较输入信号的最大工作频率通常在100 MHz至500 MHz左右。 HMC698系列等频率合成器/PFD可以工作高达1.3 GHz的PFD输入,这有利于相位噪声,但代价是更高的直流功率。最重要的是,有源PFD本身会产生加性1/f噪声,并且高度依赖于实现,也就是说,并非所有结果都是平等的。因此,在此示例中选择了HMC440,其具有非常低的PFD 1/f噪声。在将环内PD频率转换为RF输出频率时,以尽可能高的频率操作PD的经验法则可降低该环内加性PD相位噪声平台的理论20LogN增加。像ADF4401A这样的转换环路可以实现尽可能高的PFD频率,同时避免来自有源分频器的噪声。

图5.模拟锁相环 (APLL) 的简化框图。

图6.数字锁相环 (DPLL) 的简化框图。

例如,让我们考虑使用PFD的锁相10 GHz RF输出信号,其附加噪声为–153 dBc/Hz。为了简化起见,我们假设PFD是主要的环内噪声贡献因素(并不总是正确的)。以10 MHz运行PFD将获得以下带内相位噪声(即平台):

对于完全相同的情况,让我们在 100 MHz 时将 PFD 频率高出 10×。环内相位噪声改善至:

20 dB 的优势是巨大的。始终将您的 PFD 时钟尽可能高。使用基于模拟混频器的PD有几个优点。

无源混频器的加法噪声非常低,因此通常可以忽略不计。运算放大器有源环路滤波器噪声成为环内限制噪声贡献者。

比较频率可以根据需要高,通常为多个GHz,这与环内组件的残余噪声相平衡。通常,频率越高,可用的残余噪声RF放大器选择越小。

总之,最佳无源PD频率足够高,使得PD和带内分频器的加性噪声低于乘法参考振荡器的绝对相位噪声,但又不会太高,以免RF放大器残余噪声降低性能。需要多个RF放大器。

RF放大器残余相位噪声本身就是一个话题。工艺技术以及节点和电路架构是重要因素。一般来说,Si BJT提供最佳性能,但频率范围(<1 GHz)有限。砷化镓HBT是次佳的器件,通常可通过Ku波段获得(例如,ADL8150、HMC606LC5、HMC3653和HMC3587)。

pHEMT放大器在高频下广泛使用,但由于残余相位噪声变化很大,因此应谨慎使用。一般来说,pHEMT相位噪声不是很大,并且会出现温度变化。

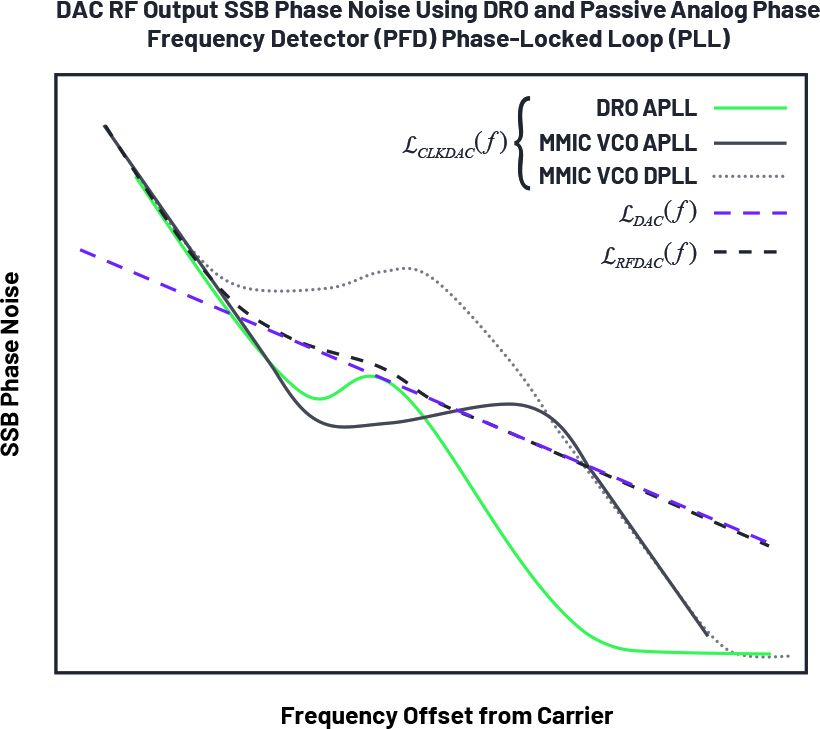

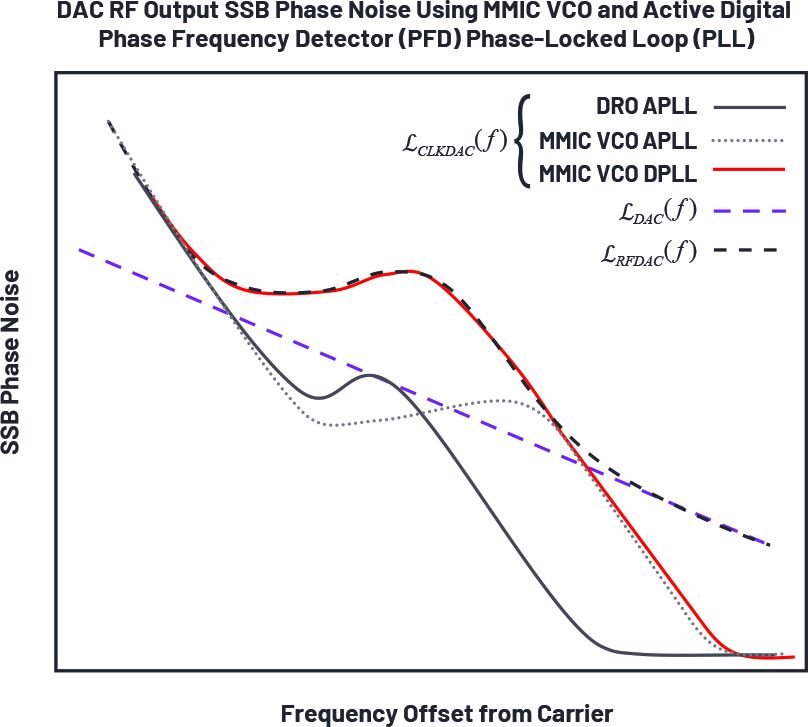

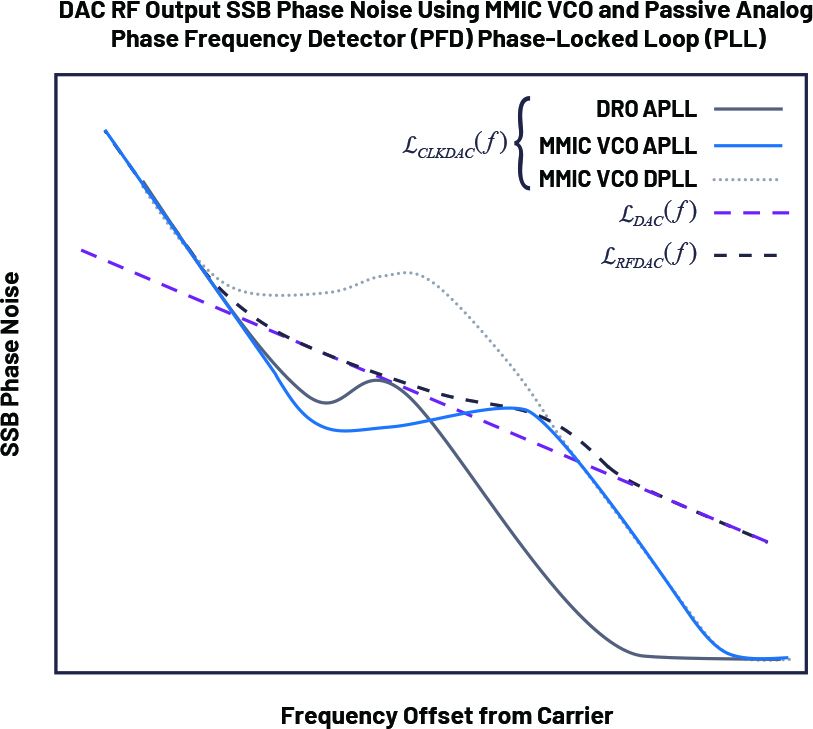

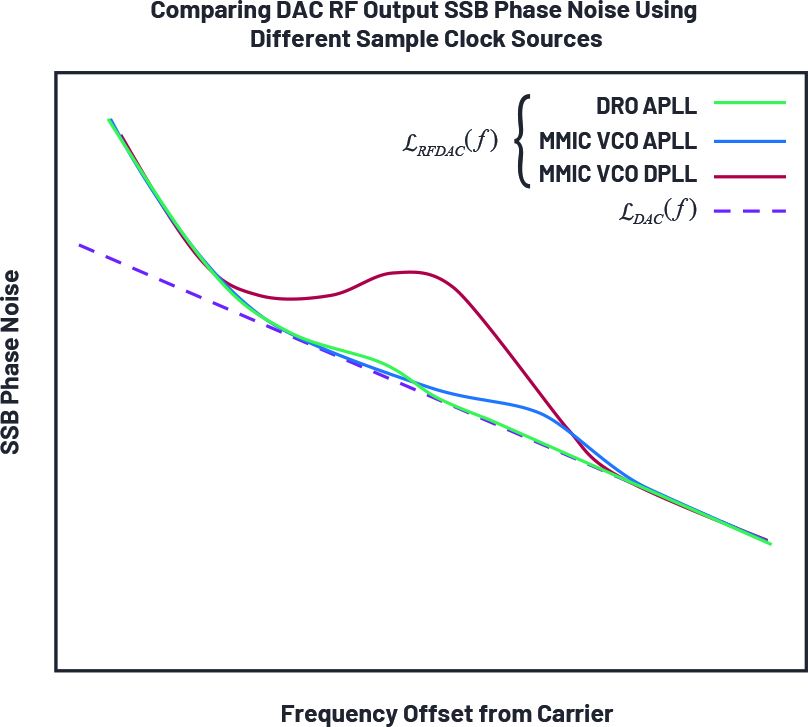

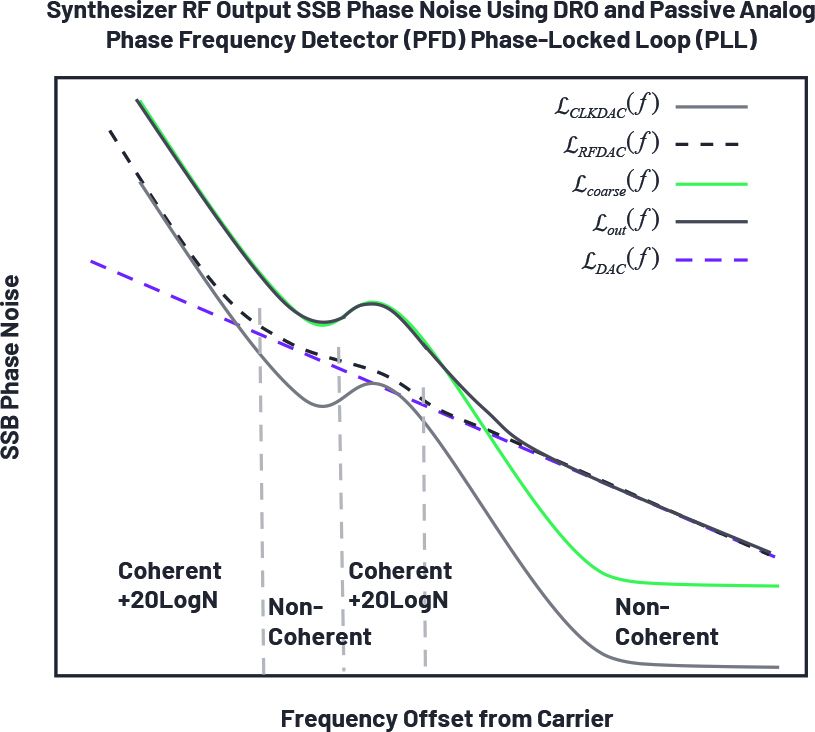

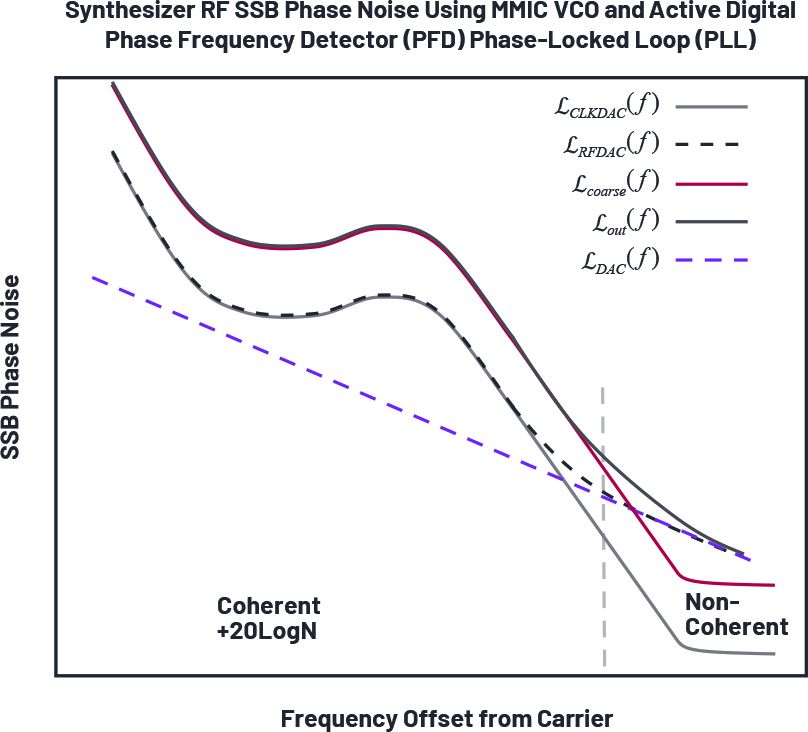

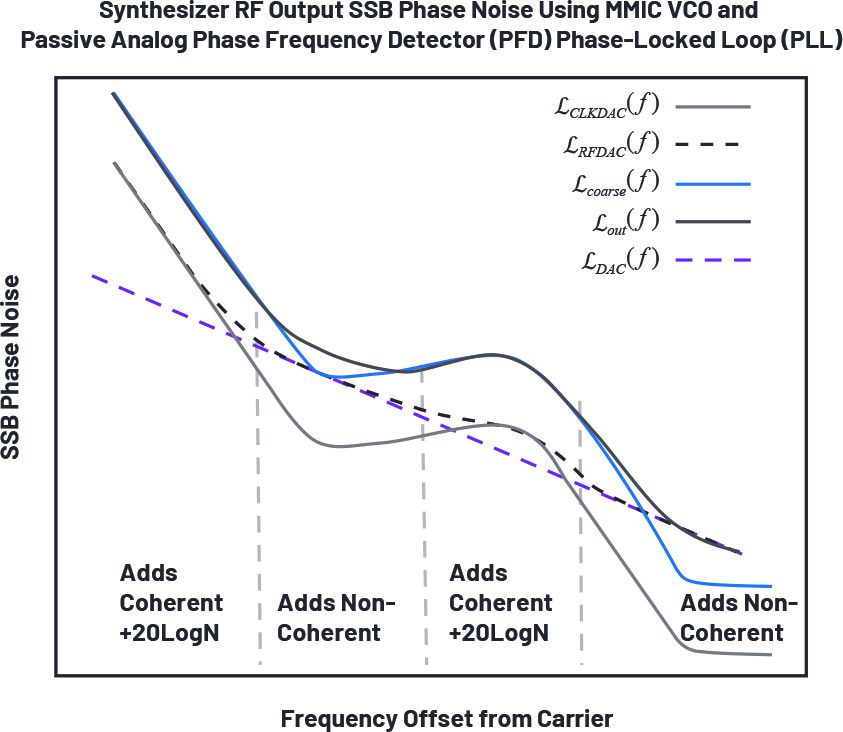

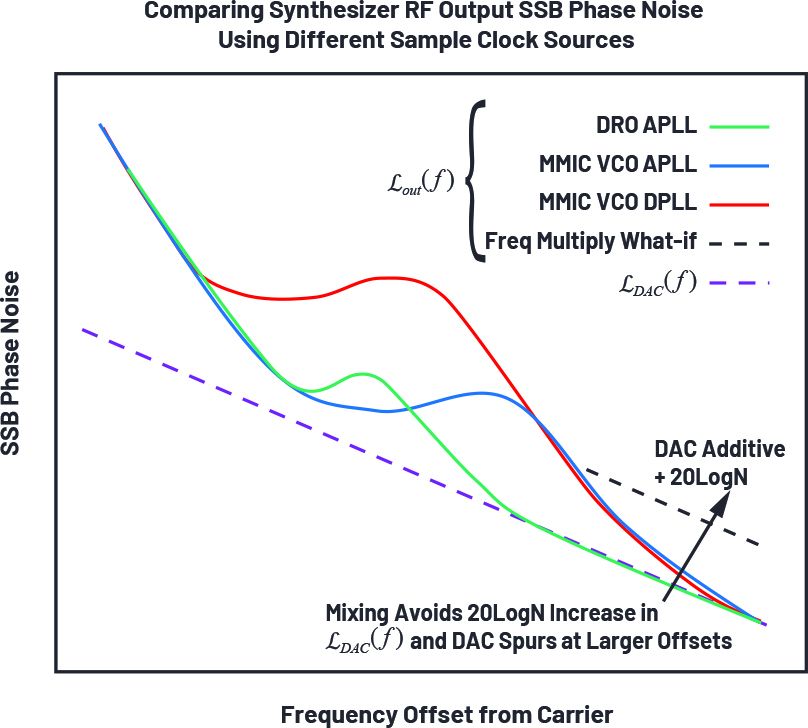

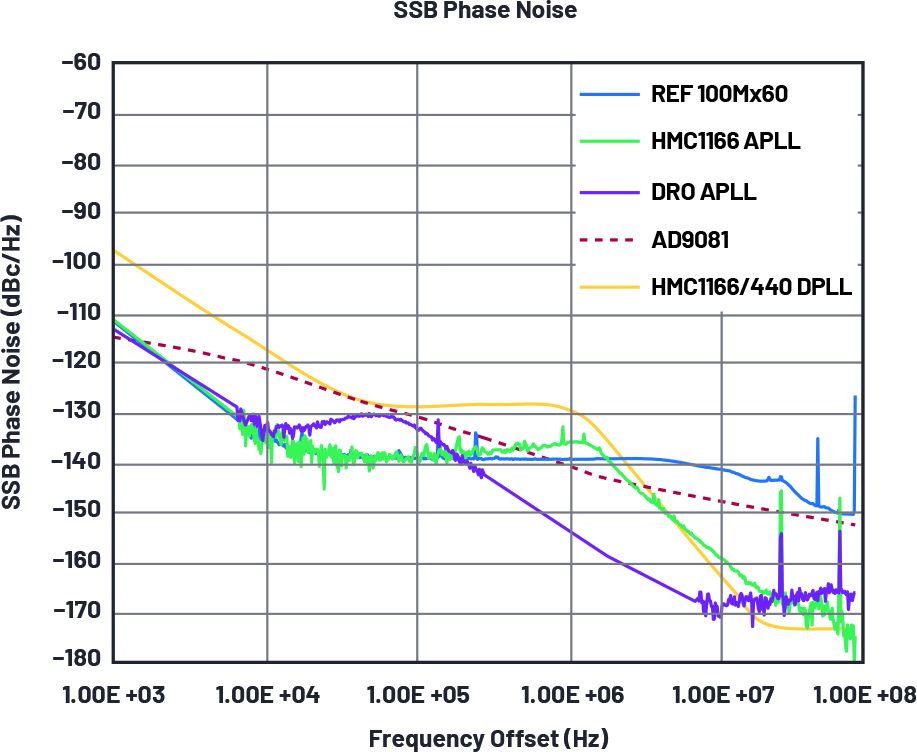

图7至图10示出了由此产生的DAC输出信号相位噪声L射频发展委员会(f) 适用于表 1 中概述的三种时钟实现方案。测得的相位噪声值如图18至图20所示。图7显示,高性能DRO RF振荡器和模拟锁相环(DRO APLL)在狭窄区域内推动DAC残余噪声,但在DAC噪声之下在很大程度上可以被认为是“不可见的”。这提供了比图8所示的传统MMIC VCO DPLL采样时钟更好的性能,后者在非常宽的失调范围内占主导地位,浪费了DAC相位噪声能力,尽管提供了最佳的SWaP-C和易用性。SWaP-C和性能的最佳平衡可能是图9中的MMIC VCO APLL,它在一段良好的关键失调范围内保持DAC相位噪声能力,但由于MMIC VCO相位噪声低于DRO,因此性能会降低到较高的失调。图10显示了时钟源选项相对于DAC加性相位噪声的复合叠加。

应该注意的是,即使在DRO之间,SSB相位噪声也有很大差异。这里使用的选项是一个大约大理石大小的小型SWaP-C DRO。存在更高性能的DRO,可以将曲线完全推低到DAC残余噪声以下。但是,DRO 相位噪声电平与 SWaP-C 之间存在直接关联,也就是说,该解决方案将比弹珠大得多,仅 DRO 组件就可能要花费数千美元!

图7.DAC 射频输出 SSB 相位噪声,使用 DRO 锁定和模拟 PD。

图8.DAC 射频输出 SSB 相位噪声,使用 MMIC VCO 锁定,有源 PFD 锁定。

图9.DAC射频输出SSB相位噪声使用MMIC VCO锁定和模拟PD。

图 10.DAC射频输出SSB相位噪声比较三种方法。

微波合成器实现

到目前为止,我们已经考虑了相对于DAC加性相位噪声电位的采样时钟源的实现选项。现在我们将研究调谐生成器的实现。设计人员根据多种DAC和ADC目标(包括奈奎斯特区、瞬时带宽和数据有效载荷等)选择数据转换器采样时钟频率。一个有趣的难题是如何有效地规划从可用的采样时钟及其次谐波、N谐波和/N兄弟中生成一组固定音调的频率。这些固定音调是粗频集,与DAC输出的精细频率集混合。

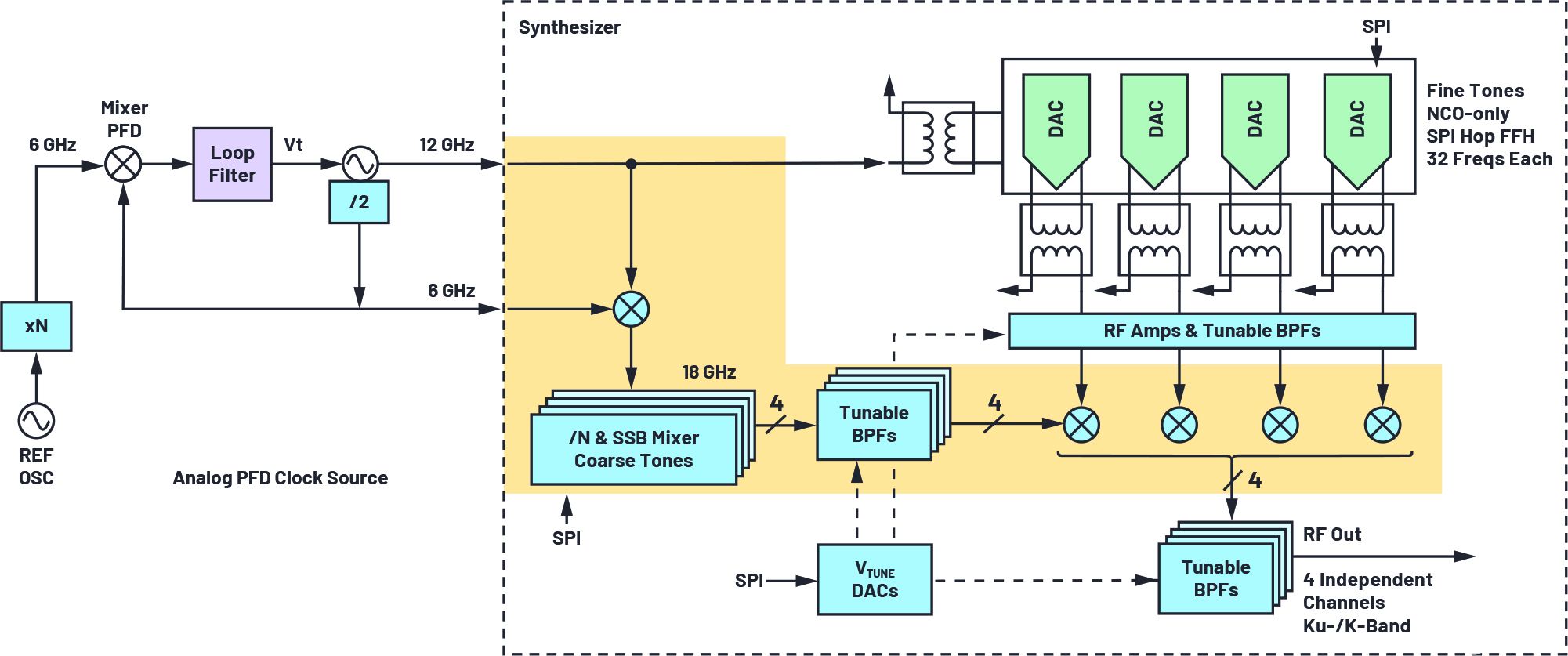

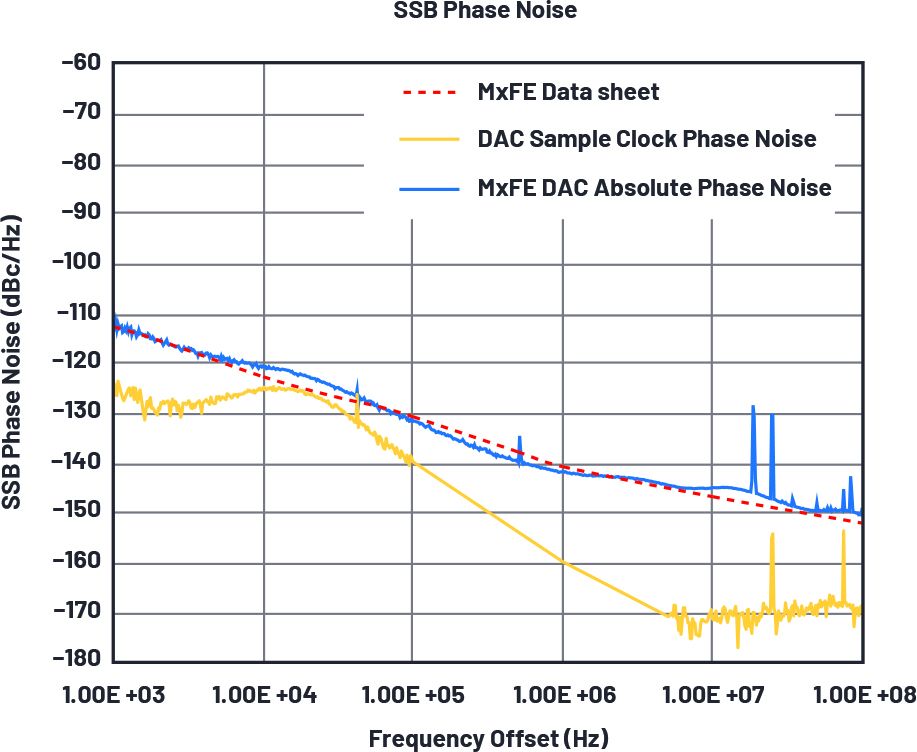

图11是粗/细混合方案的框图。在本例中,我们使用MxFE RF ADC AD9081/AD9082,采样时钟为12 GSPS,来自VCO的VCO,该VCO也以6 GHz输出RF/2。这些音调是“免费”的,因为您需要它们来为DAC提供时钟,因此将粗调发生器建立在它们周围是非常有意义的。结果表明,将可编程分频器馈送到单边带混频器方案的18 GHz会产生一组粗频率,当与DAC输出混合时,可以覆盖大多数Ku和K频段的合成。可调谐带通滤波器对于衰减许多混频和DAC杂散至关重要。精密DAC将SPI控制转换为低噪声模拟控制信号,调谐可调谐滤波器(例如ADV7125)。®

图 11.推荐使用模拟PD源的基于DAC的粗/细混频器合成器。

当然,这种混频方案听起来有点复杂,一个蛮力更简单的选择是频率乘以DAC输出而不是混频。倍频很有吸引力,因为它更简单且SWaP-C更低,因为图11中的橙色突出显示功能块被图12b中的乘法器功能块取代。倍频的问题,以及为什么我们在这里不认真考虑它作为一种选择,是20LogN DAC本底噪声和DAC杂散退化。直接RF DAC输出具有出色的附加相位噪声和杂散性(通常DAC产生的杂散远低于60 dBc)。但是,要将3 GHz至6 GHz DAC RF输出转换为Ku波段,至少需要乘以4,即DAC杂散和相位噪声下降12 dB。从任务的角度来看,这种12 dB的降级很有可能使DAC杂散和噪声从合规变为不合规。

图 12.(a) 性能较低的替代方案:集成数字PLL采样时钟。(b) 性能较低的替代办法:乘数块。

粗/细混频器方法增加的复杂性值得麻烦,因为它避免了DAC的倍增,因此DAC杂散和相位噪声电平以1:1转换为上变频RF输出(不增加12 dB!

图13至图16说明了粗略和精细的SSB相位噪声如何结合,在所需的上变频微波频率下产生最终的SSB相位噪声。测量的相位噪声值稍后如图18至图20所示。倍频与将信号与自身副本混合相同。同样,混合不同频率的相干信号具有与乘法相同的20LogN相位噪声影响。换句话说,在图13至图16中,在标注为“相干”的偏移区域中,采用混合与乘法方法没有相位噪声优势。在将灰度所示的采样时钟上变频为更高的LO频率时,整个相位噪声曲线被简单地向上转换20LogN。粗/细混音的主要动机是当相位噪声肩接近本底噪声时,在较大的偏移下获得的好处。由于在这些偏移处,LO粗音相位噪声远低于DAC加性噪声水平,因此它基本上没有任何贡献,您只能看到DAC相位噪声1:1转换为上变频微波信号。图16比较了每种方法的最终频率合成器相位噪声,并注释了混频与乘法的远失调优势。

图 13.微波合成器SSB相位噪声使用DRO锁定与模拟PD。

图 14.微波合成器SSB相位噪声使用MMIC VCO锁定,有源PFD锁定。

图 15.微波合成器SSB相位噪声使用MMIC VCO锁定与模拟PD。

图 16.微波合成器SSB相位噪声比较的三种方法。

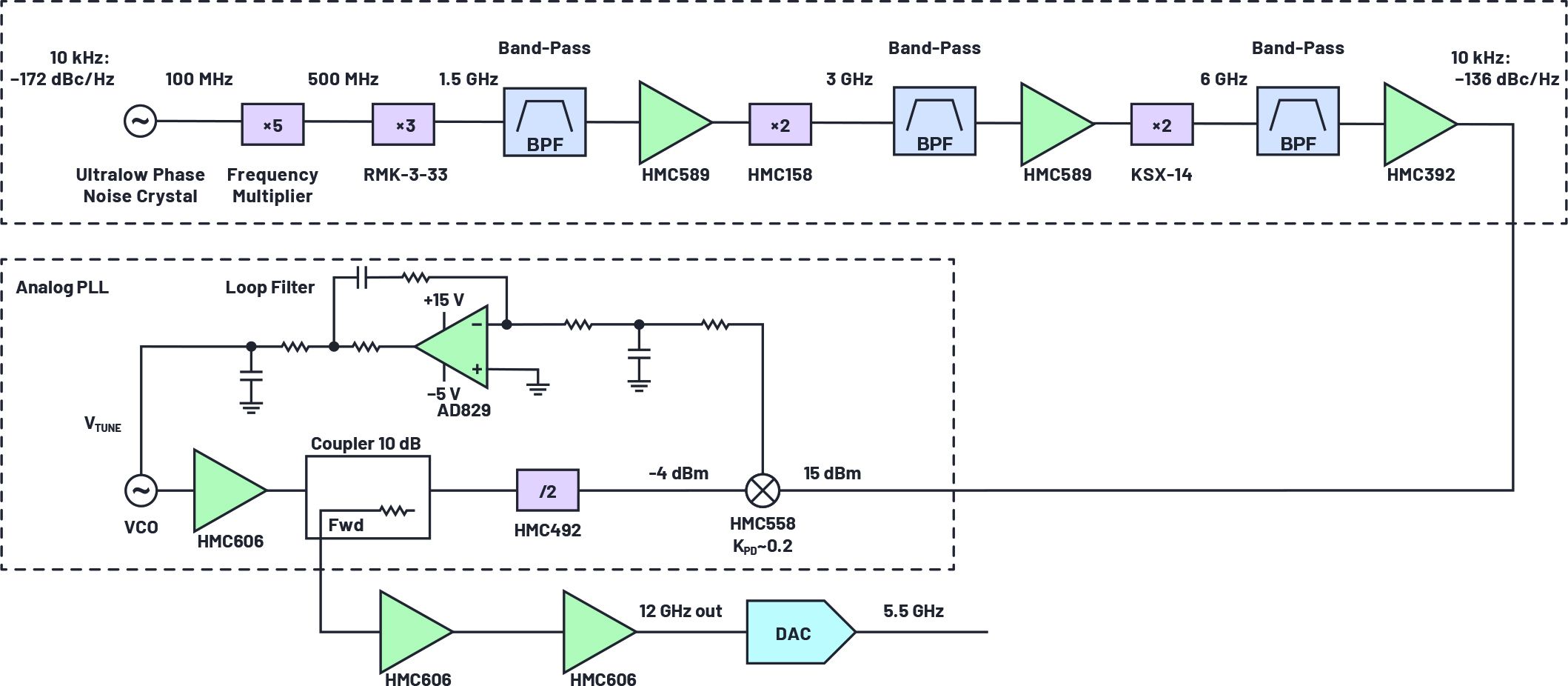

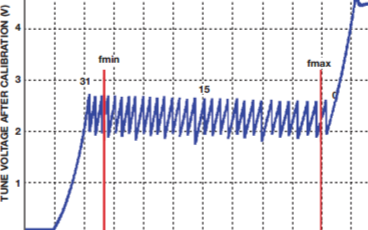

图17是实验室中用于获取图18所示的SSB相位噪声的元件链。超低噪声100 MHz晶体振荡器乘以60。图18中产生的6 GHz参考相位噪声的底限为–137 dBc/Hz。作为健全性检查,将100 MHz晶体本底噪声加上乘法链的加性相位噪声置于–173 dBc,这是有道理的。基准电压源6 GHz信号馈送HMC558双平衡混频器的LO端口,该混频器用作模拟PD。 (请注意,混频器的IF端口必须直流耦合。PD 常数 (K帕金森)来计算运算放大器有源滤波器值。这是使用机械延迟块和电压表通过实验测量的。实验设置在RF振荡器点测量了DRO和MMIC VCO(HMC1166)。因为 KVCO两者之间有很大不同,需要不同的环路滤波器值。使用HMC606时,放大器不会增加残余相位噪声。

图 17.评估电路。

图 18.测量的SSB相位噪声比较了采样时钟场景、DAC加法和基准电压源。所有走线归一化为测得的DAC输出频率5.5 GHz。

如前所述,根据–137 dBc/Hz的倍增参考底电平选择6 GHz作为PD比较频率。环内相位噪声将升高20Log10 (12/6 GHz) = 6 dB,表示为N=2。在此参考本底噪声电平下,相反支路的运算放大器、分频器和放大器残余噪声完全低于基准基准,因此它们不会产生影响。如果改为选择3 GHz PD频率,则参考底值为–143 dBc/Hz(与6 GHz方案相比,改进了6 dB)和N=4(与6 GHz情景相比,降低了6 dB),因此参考绝对相位噪声对最终相位噪声的影响随着频率的放大或缩小而受到洗刷。但是,环内分频器、放大器和运算放大器的加性噪声现在必须有效提高6 dB,才能在3 GHz时保持无贡献者。随着PD频率的降低,您将达到这种加性噪声占主导地位的点。反过来,将PD频率提高到12 GHz可以消除环内分频器的附加噪声(良好),并且可能是可行的。RF放大器的附加噪声会随着频率的增加而增加,但在12 GHz时可能很好。 K帕金森需要在 12 GHz 下重新测量。本文未评估 12 GHz PD 设置,但此设置可能工作正常。

如果在产品中实现,则需要锁采集电路。这没有被证明。V调整需要“预充电”以将VCO频率控制得足够接近基准电压源,以便可以捕获锁定。

在图19中,使用带有模拟PLL和AD829 o的HMC1166测得的相位噪声结果令人印象深刻。P 放大器有源环路滤波器。使用相同的HMC1166 VCO,我们演示了使用模拟PLL的~15 dB改进,而基于HMC440的PD采用1 GHz方案则提高了~1 dB。最重要的是,时钟主导相位噪声的失调被限制在200 kHz至2 MHz,DAC加性相位噪声的最坏情况降级为~10 dB。与此形成对比的是HMC440方案,在HMC440实现中,时钟在20 kHz至2 MHz之间占据了额外的十倍,DAC加性噪声的最坏情况会降低17 dB。在闭合失调时,VCO APLL跟踪参考相位噪声,在中间失调处有来自环路滤波器的一点峰化。这个大约 500 kHz 的区域可能会随着进一步的迭代而得到改善。在建模中显示出有希望的结果的建议技术是减少KVCO的VCO。上述方案使用现成的 COTS 组件,并且以低成本相当容易演示。

图 19.使用VCO (HMC1166)使用模拟PLL锁定测得的DAC输出SSB相位噪声。所有走线归一化为测得的DAC输出频率5.5 GHz。

真正令人兴奋的性能来自图 20 中的 DRO 场景,尽管 SWaP-C 更高。考虑到DRO APLL的性能,我们几乎将其降低到足以在DAC相位噪声下不可见。DAC RF输出相位噪声在CLK峰值接近DAC相位噪声的10 kHz区域确实上升了几dB。环路带宽非常窄,以便获得到极低DRO相位噪声的最佳转换点。DRO APLL的峰值被怀疑是运算放大器噪声。总体而言,我们认为目标在几dB内实现,可以推荐使用模拟PLL锁定的12 GHz DRO,用于需要MxFE器件全相位噪声能力的最低相位噪声合成器。

图 20.使用模拟PLL锁定的DRO测量的DAC输出SSB相位噪声。所有走线归一化为测得的DAC输出频率5.5 GHz。其他优点。

使用基于 DAC 的混频器频率合成器的其他优势

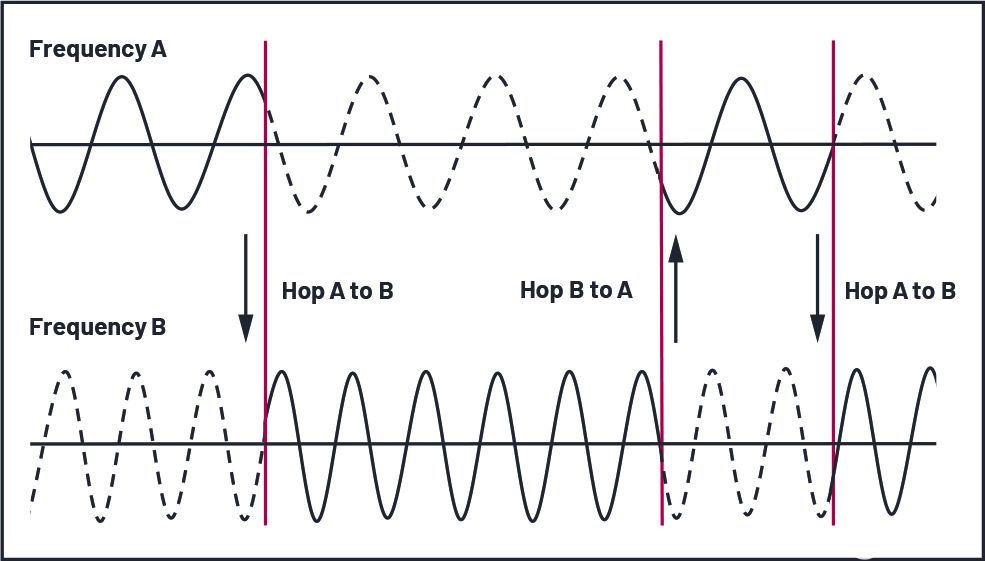

除了相位噪声优势外,基于 MxFE DAC 的粗/细混频器频率合成器在仅快速跳频 (FFH) NCO 模式下能够实现 ~300 ns 的捷变跳频。在32个独立的NCO之间跳频时,频率跳相位相干性保持不变,如图21所示。此外,该合成器不仅限于敏捷音调生成。DAC提供了通过JESD204B/JESD204C数据链路实现任意调制的灵活性。

图 21.跳频相位相干性。

结论

ADI公司最新一代高速DAC(例如AD9162、AD9164、AD9172、AD9174、AD9081、AD9082)具有出色的相位噪声,使SWaP-C在下一代低相位噪声、快速跳频、捷变RF/微波频率合成器中具有优势。固定DAC采样时钟必须具有非常低的SSB相位噪声,这超出了主流宽带VCO-PLL的能力。与传统的基于PFD的有源PLL频率合成器相比,模拟PD可提供10 dB至20 dB的环内相位噪声性能改进。为了满足最苛刻的相位噪声系统要求,建议的固定时钟实现方案是使用模拟PLL锁定的DRO。提供了基于DAC的粗/细混频器频率合成器示例、测量的相位噪声结果和应用电路。

-

ADI

+关注

关注

150文章

46086浏览量

271141 -

振荡器

+关注

关注

28文章

4158浏览量

142385 -

dac

+关注

关注

44文章

2701浏览量

196462 -

谐振器

+关注

关注

4文章

1162浏览量

67376

发布评论请先 登录

低相位噪声电压控制振荡器(VCO)和稳定基准电压构成的频率合成器

TI推出LMX2581业界最低相位噪声的频率合成器

业界最低相位噪声频率合成器LMX2581的特性优势是什么

面向 RF 应用的低相位噪声频率合成器演示介绍

如何实现低BER(误码率)、低杂散输出和低相位噪声的系统级目标

AN-419: 用于完整的直接数字频率合成器AD9850的分立、低相位噪声、125MH晶振

基于DAC的低相位噪声频率合成适用于快速跳频宽带微波应用

基于DAC的低相位噪声频率合成适用于快速跳频宽带微波应用

评论