1 (背景)云计算复杂计算场景挑战

云计算是由IaaS、PaaS以及SaaS组成的分层服务体系,计算、存储和网络是IaaS层核心的三类服务。

云计算的特点:

超大的规模、大量的数据、复杂的网络以及无处不在的安全问题;

虚拟化、多租户;

复杂系统解构以及可扩展性;

繁重的工作负载以及针对特定场景的服务;

可迁移性,和对设备和服务接口一致性的要求。

底层硬件架构挑战:

如何兼顾性能和灵活性;

从业务异构加速、工作任务卸载,到业务和管理分离;

如何实现接口的标准化和弹性,以及硬件加速的虚拟化和个性化;

如何实现硬件加速的弹性和支持软件的长期迭代;

如何硬件高可用;

最大挑战:一个平台应对上述所有挑战。

2 (理论)软硬件融合综述

2.1 软硬件融合的背景

软件应用层出不穷,并且快速迭代。两年一个新的软件热点,并且,已有热点技术仍在快速演进和迭代。

而硬件越来越复杂,芯片工艺走向5nm以下,甚至即将进入亚纳米,3D堆叠封装,4D的Chiplet互联。这都使得芯片规模越来越大。芯片如此复杂,越来越难以驾驭;同时,芯片的一次性成本及研发风险都变得越来越高。

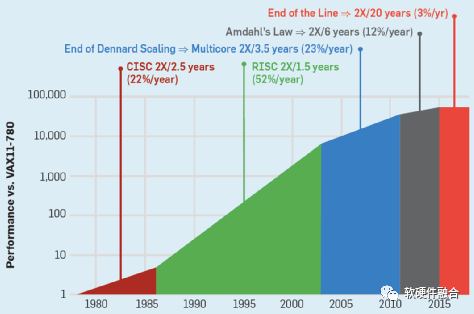

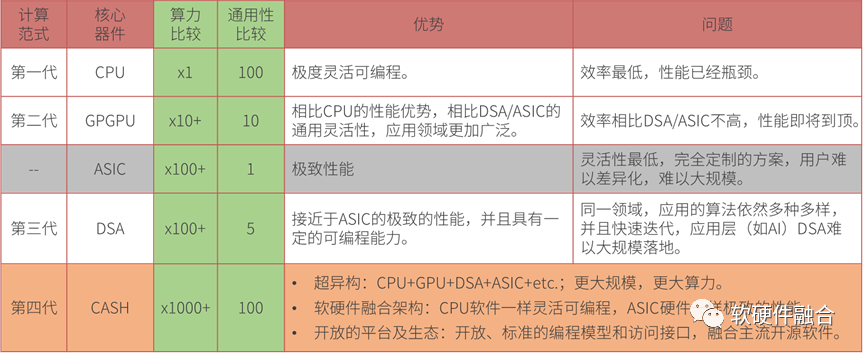

CPU性能瓶颈,但服务器的工作负载数量和单个负载的算力消耗仍在增加,“摩尔定律”要想持续,必须需要更多更复杂的硬件加速。而ASIC/DSA的灵活性不够,难以满足应用的多样和变化,也使得芯片越来越难以大规模落地。

软硬件之间的鸿沟越拉越大:CPU软件性能低下,定制ASIC难以大规模复制;软件迭代越来越快,硬件迭代却越来越慢。芯片高投入高风险,严重制约着软件的发展。

2.2 软件和硬件的定义

指令是软件和硬件的媒介,指令的复杂度(也即单位计算的密度)决定了系统的软硬件解耦程度。

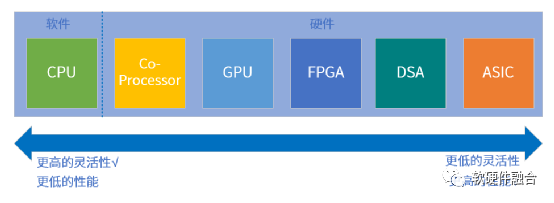

按照指令的复杂度划分,典型的处理器平台大致分为CPU、协处理器、GPU、FPGA、DSA、ASIC等。从左往右,各个处理器平台的单位指令越来越复杂,性能越来越好,而灵活性却越来越低。

我们把任务在CPU运行,定义为软件运行;把任务在协处理器、GPU、FPGA、DSA或ASIC运行,则定义为硬件加速运行。

2.3 软硬件融合

把一个Workload映射到处理引擎,有如下特点:

均衡:根据任务特点,映射到CPU、GPU、DSA、ASIC等最合适的处理引擎。

动态:任务最合适的处理引擎,并非一成不变,而是随着系统发展迭代有可能Offload/Onload。

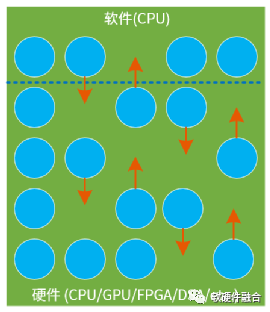

复杂的系统,由分层分块的各个组件有机组成。软硬件融合,不改变系统层次结构和组件交互关系,但打破软硬件的界限,通过系统级的协同,达成整体最优。

传统分层很清晰,下层硬件上层软件;软硬件融合的分层分块,每个任务模块都是不同程度软硬件解耦基础上的软硬件协同。整个系统呈现出:软件中有硬件,硬件中有软件,软硬件融合成一体。

《软硬件融合》图书的副标题是“超大规模云计算架构创新之路”,来源是:①复杂分层的系统、②CPU性能瓶颈、③超大规模以及④特定场景服务,这些原因共同使得:软硬件融合当前主要是系统不断卸载。

“无规模,不卸载”。哪些任务适合卸载?

性能敏感,占据较多CPU资源;

广泛部署,运行于众多服务器。

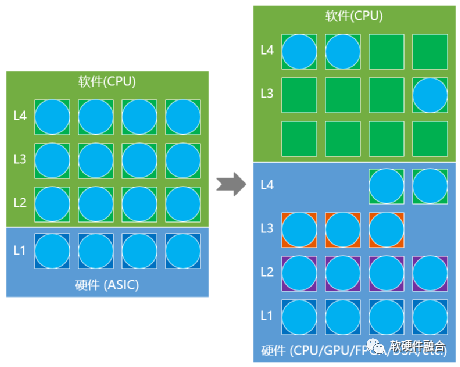

宏观的看,分层的系统,越上层越灵活软件成分越多,越下层越固定硬件成分越多,根据这个特点,软硬件融合卸载可以形成如下趋势:

被动的趋势。庞大的规模以及特定场景服务,使得云计算底层Workload逐渐稳定并且逐步Offload到硬件。

主动的趋势。软硬件融合架构,使得“硬件”更加灵活,功能也更加强大,使得更多的层次功能向“硬件”加速转移。

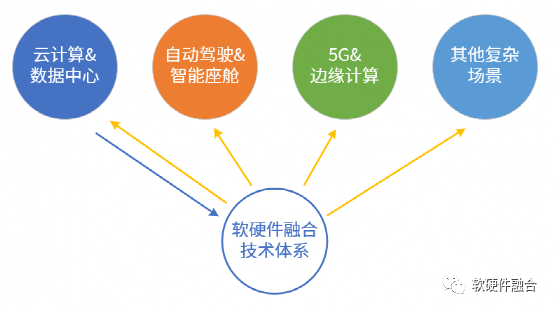

2.4 软硬件融合的应用领域

云计算的规模庞大,算力要求最高,系统也最复杂。所以,云计算最先遇到各种挑战,最需要软硬件融合。

未来,随着其他领域的算力需求和系统复杂度也质的提升,必然也需要软硬件融合相关技术。软硬件融合,面向未来复杂计算场景,超异构混合计算,算力需求再上1-2个数量级。

软硬件融合相关技术,从云计算抽象出来,反过来指引包括云计算在内的各种复杂计算场景的芯片及系统设计。

3(技术)软硬件融合技术基础

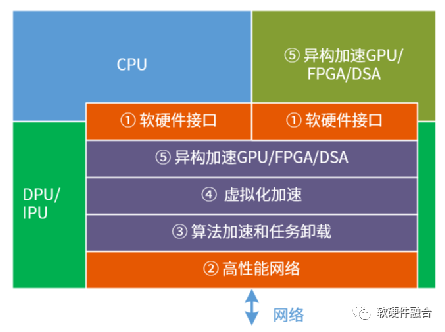

软硬件融合相关的技术包括:

软硬件接口。聚焦软件和硬件高效的数据交互;

高性能网络。例如RDMA和拥塞控制。

算法加速和任务卸载。算法硬件实现以及任务卸载框架。

虚拟化的硬件加速。虚拟化处理的高性能实现。

异构计算加速平台。独立/集成的GPU/FPGA/DSA异构加速平台。

4(场景)DPU/IPU,云计算软硬件融合的核心承载

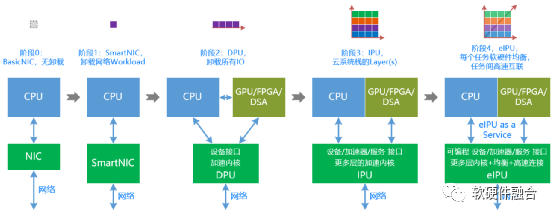

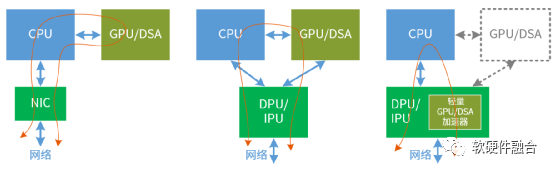

4.1 CPU卸载视角:DPU是集成加速平台

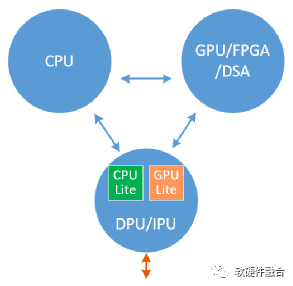

需要有独立的加速平台,不断的把工作任务从CPU软件卸载到硬件加速。因此,DPU/IPU主要用于底层通用任务加速,而GPU/FPGA/DSA用于应用层的业务加速。

NVIDIA 2020年5月发布DPU,10月份大张旗鼓宣传;作者2020年8月份提出四阶段论;Intel 2021年6月份发布IPU。

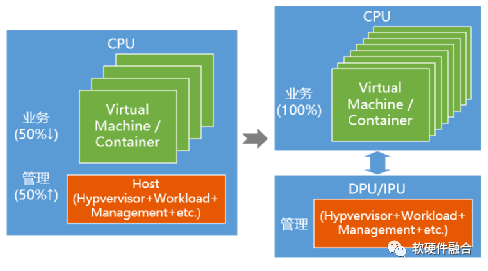

4.2 DPU的额外价值:业务管理分离,释放AI强劲动力

业务和管理分离,有非常多的额外好处,如:

CPU资源完全交付;

传统客户方便上云;

主机侧独立安全域;

物理机+虚拟机的优势合并;

统一公有云和私有云运维。

CPU性能瓶颈,IO带宽持续增大,IO成为系统瓶颈。DPU/IPU增强了IO的功能,并且逐渐吞噬CPU和GPU的通用工作任务。

4.3 以数据为中心

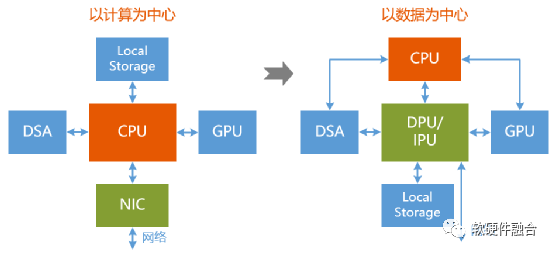

大数据、AI等场景呈现“高数据量低计算量”的特点,并且“云原生”等趋势使得云计算复杂系统解构,进一步增强了这一特点。

以计算为中心,指令控制流驱动计算;未来,以数据为中心,数据流驱动计算。

4.4 DPU/IPU典型案例

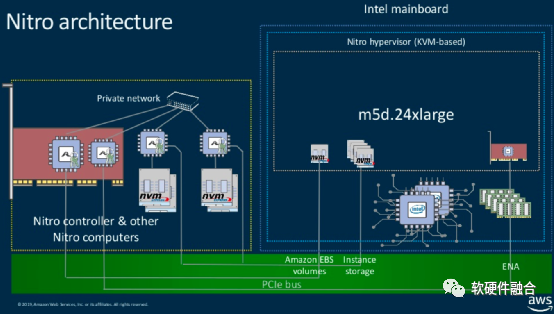

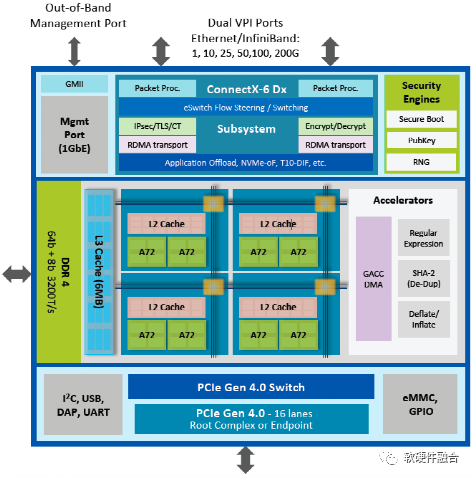

典型案例:AWS Nitro系统 (偏通用可编程)vs NVIDIA Bluefield DPU (偏定制极致性能)。

AWS Nitro系统包括:VPC加速卡、EBS加速卡、本地存储加速卡、Nitro控制器、安全芯片以及Lite Hypervisor。

NVIDIA DPU-2的优势:硬件网络加速/RDMA网卡/单芯片SOC;劣势:存储软件卸载/非标接口/难以差异化/网络无法数据面编程。

5(本质)基于软硬件融合的超异构计算

5.1 DPU成为计算的核心

CPU、GPU和DPU,既相互协作,又相互竞争。互联网法则:得入口者得天下。DPU/IPU成为数据中心算力和服务的核心。

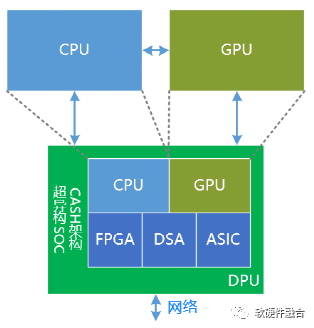

传统的观点,大家认为DPU是CPU的任务卸载。而从软硬件融合观点,则认为:DPU是包含嵌入式CPU/GPU在内的超异构计算平台,而独立CPU/GPU是DPU的扩展。

5.2 超异构和软硬件融合

当前,大家对DPU的认识还没有形成定论,从DPU到超异构计算,整个认识是逐级增强的:

Level 1:DPU是CPU的任务卸载/加速。

Level 2:IPU是基础设施,支撑上层应用。

Level 3:DPU/IPU是计算的核心,CPU和GPU成为扩展。

Level 4:DPU/IPU的本质是超异构计算,需要在极致灵活性的基础上,提供极致的性能。

要实现超异构计算,为什么需要软硬件融合架构(Converged Architecture of Software and Hardware,CASH)?软硬件融合能够做到:

性能。相比GPGPU,性能再提升100+倍;相比DSA,性能再提升10+倍。

灵活性。接近于CPU的灵活性、通用可编程性。

资源效率。跟DSA接近的资源效率,单位晶体管消耗下最极致的性能。

设计规模。软硬件融合,驾驭10+倍更大规模的设计。

架构。基于软硬件融合架构的超异构计算:CPU + GPU + DSA + ASIC + etc.。

生态。开放的平台及生态,开放、标准的编程模型和访问接口,融合主流开源软件。

5.3 第四代算力革命:基于软硬件融合的超异构计算

审核编辑:刘清

-

asic

+关注

关注

34文章

1269浏览量

124054 -

DPU

+关注

关注

0文章

407浏览量

26201 -

DSA

+关注

关注

0文章

53浏览量

15770

原文标题:软硬件融合:从DPU到超异构计算

文章出处:【微信号:阿宝1990,微信公众号:阿宝1990】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

详细分析DPU认识的四个层级

详细分析DPU认识的四个层级

评论