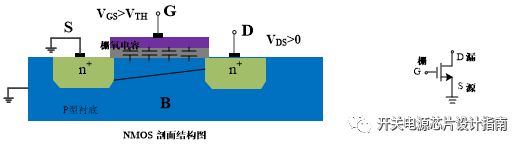

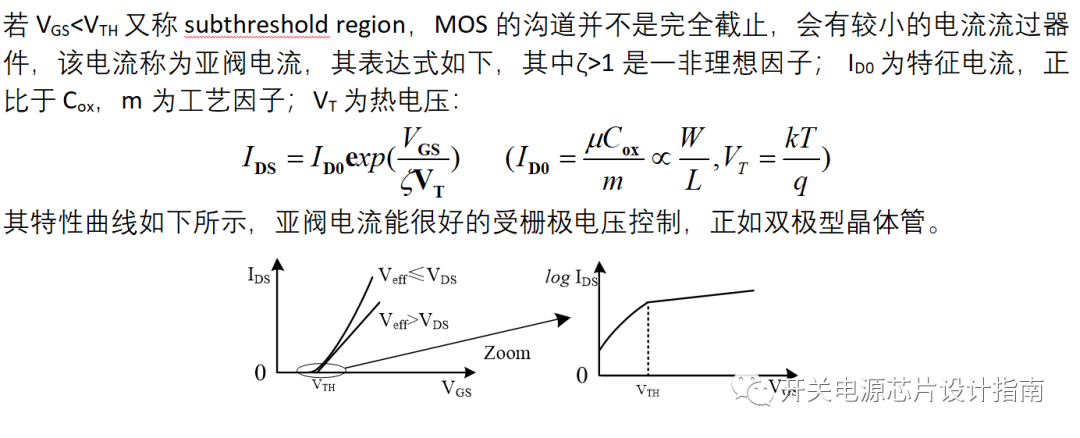

本章定性和定量分析MOS的电流IDS与栅源电压VGS、漏源电压VDS间的IV特性关系。NMOS的剖面结构图以及其电路符合如下图所示,由栅极(G),漏极(D)、源极(S)和基板(B)构成。当GS极加入正电压,当VGS>VTH时,G极板通过栅氧电容会在D极和S极间形成带自由电子的导电沟道;当VDS>0时,导电沟道的自由电子就会移动形成电流。

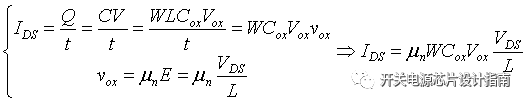

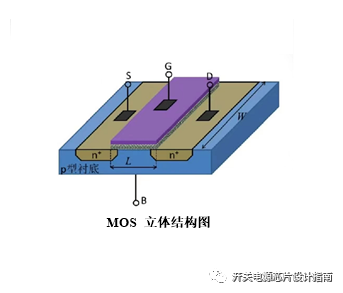

根据电流的定义单位时间流过横截面的电荷量,可以求出IDS为总的电荷量Q处于时间t;电容的电荷量为C*Vox;下图为NMOS 的立体结构图,G极对B极的电容可以近似求出为WLCox(Cox为单位面积栅氧电容值),L(导电沟道长度)除以t则为电荷移动速度vox。电荷移动速度vox又可以由电场VDS/L(假设电场分布均匀)和电子迁移率μn相乘得到。

当VDS=0时即只有VGS作用:形成导电沟道的有效电压(过驱动电压)可表示如下:

实际上由于VDS与Veff共同作用,形成的沟道电荷厚度不是均匀分布,如下图所示,导电沟道呈斜坡状。当VDS

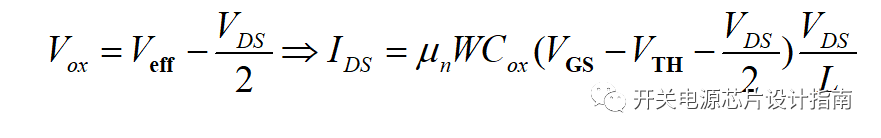

靠近VSS端有效沟道形成电压高(Veff)电荷厚。取中间点平均电压VDS/2来近似计算IDS:

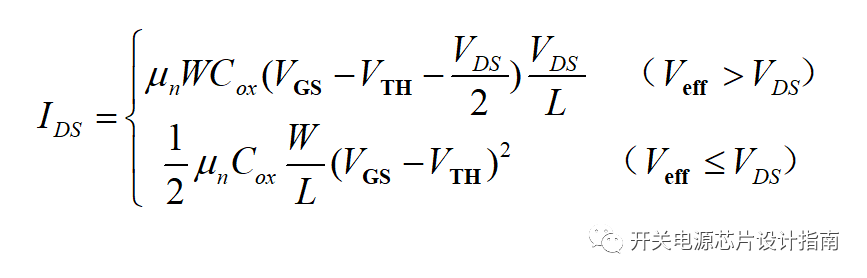

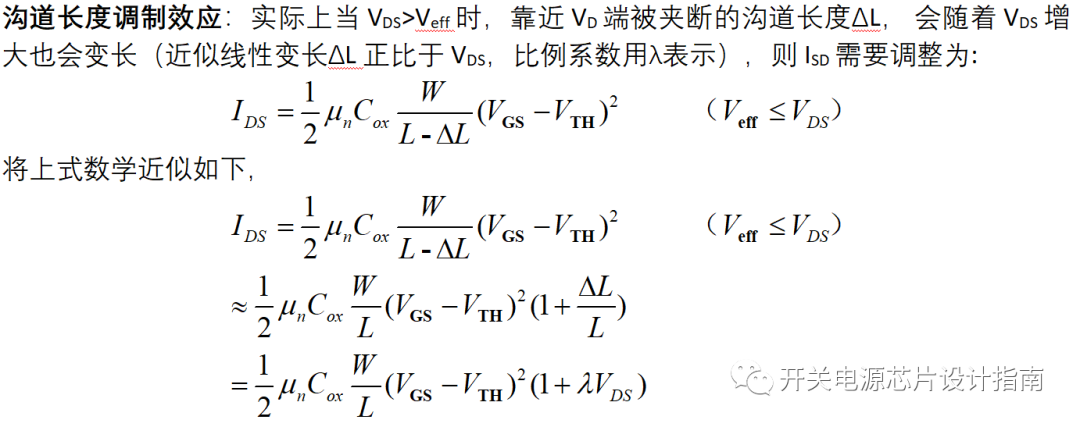

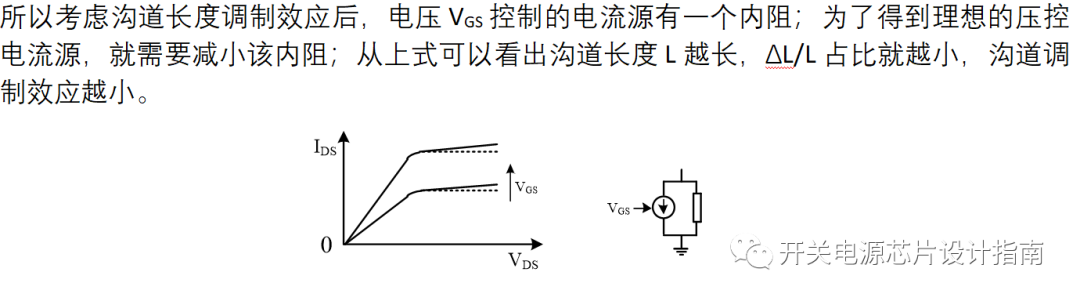

当VDS从0V继续增大到VDS=Veff时,靠近VD端的沟道被夹断,有效沟道形成电压为0;再继续增大VDS,夹断点将向源极方向移动,VDS增加的部分全部落在夹断区,故ID几乎不随VDS增大而变化,IDS可表示为:

考虑以上两种情况下的Vox, IDS可综合如下

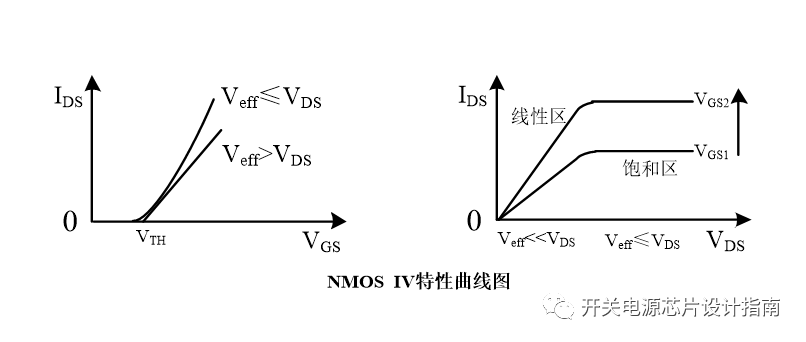

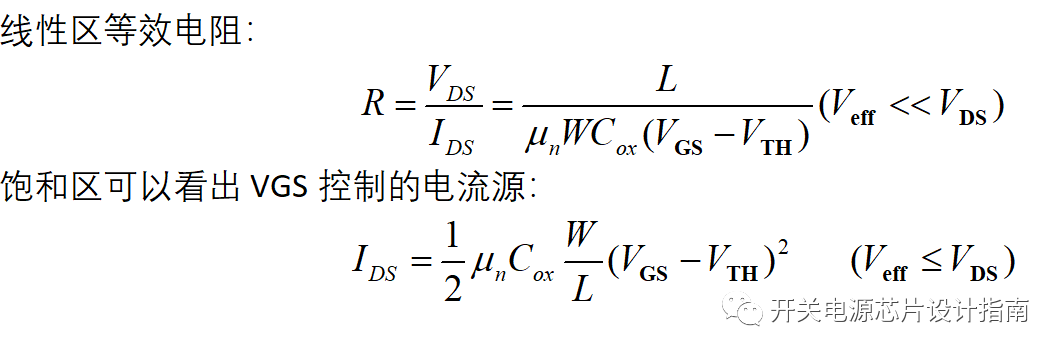

通过分析IDS与VGS和VDS的关系式,NMOS的IV特性曲线如下图所示。左图中当VGS

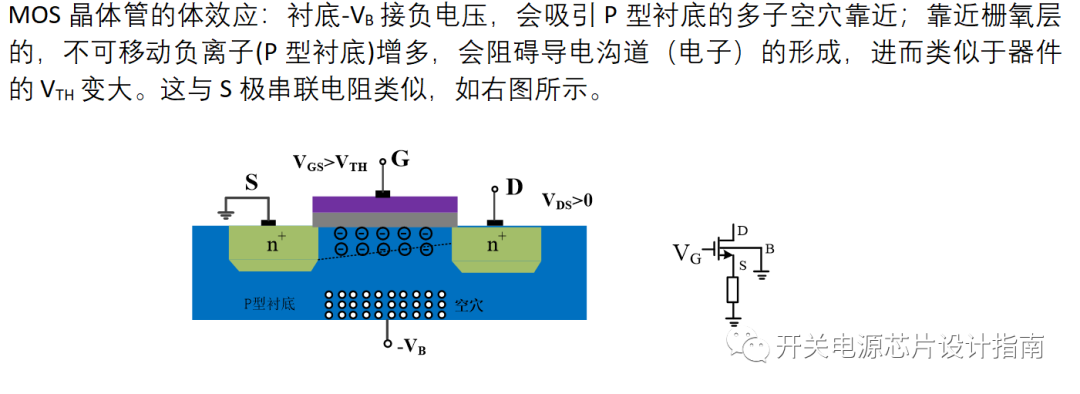

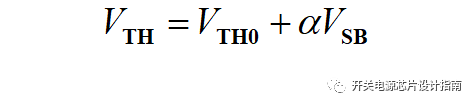

公式如下,其中VSB为源极对衬底的电压,α为比例系数,大概0.2左右。

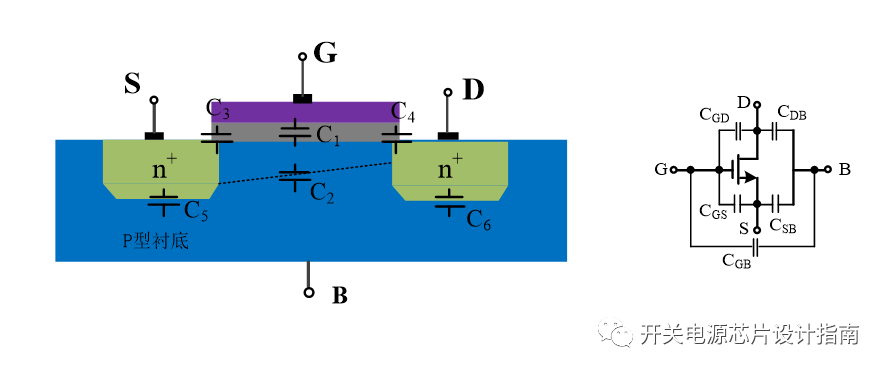

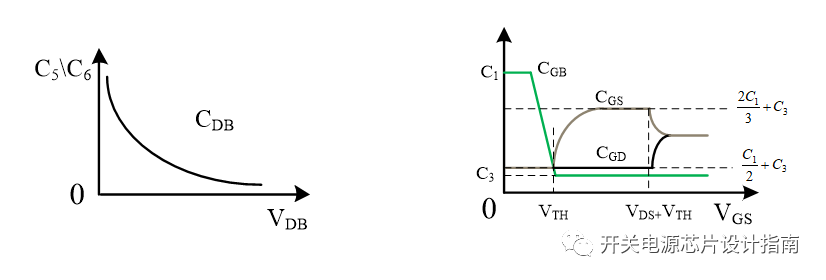

寄生电容:栅氧化层电容C1=WLCox, 衬底和沟道与衬底间的耗尽层电容C2,栅和源/漏极电容C3, C4,源/漏极与衬底间的PN结电容C5和C6。

各电容随电压变化趋势如下图所示。当VGS=0时,没有沟道耗尽层C2=0, C3=C4, CGB=(C1串联连接C2)=C1; 随着VGS上升至VTH,由于C2很小,C1和C2串联后的CGB变小;当VDS>VGS>VTH,由于饱和区沟道的存在,C1不存在,CGB=C2保持一个很小的状态,CGD=C4不变(沟道夹断),CGS可以看成C3并联‘C1*2/3’(由于沟道分布不均匀,不等于WLCox); 接着增大VGS>VDS(线性区), 沟道近似线性分布,CGB由于沟道的隔离任然保持一个很小的状态,CGS可近似认为等于CGD=C3+C1/2=C4+C1/2。源/漏极与衬底间的PN结电容C5与C6,即CDB随VDB增大而变小,如果S接地,CSB的耗尽层电压不变也不变。

审核编辑:汤梓红

-

NMOS

+关注

关注

3文章

404浏览量

36941 -

晶体管

+关注

关注

78文章

10439浏览量

148584 -

MOS

+关注

关注

32文章

1757浏览量

101229

原文标题:MOS晶体管I-V特性

文章出处:【微信号:开关电源芯片设计指南,微信公众号:开关电源芯片设计指南】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶体管的结构特性

吉时利——半导体分立器件I-V特性测试方案

晶体硅光伏(PV)方阵I-V特性的现场测量 GB/T 122

CMOS晶体管,CMOS晶体管是什么意思

增强型MOS晶体管,增强型MOS晶体管是什么意思

数字源表可帮助提取半导体器件的基本 I-V 特性参数

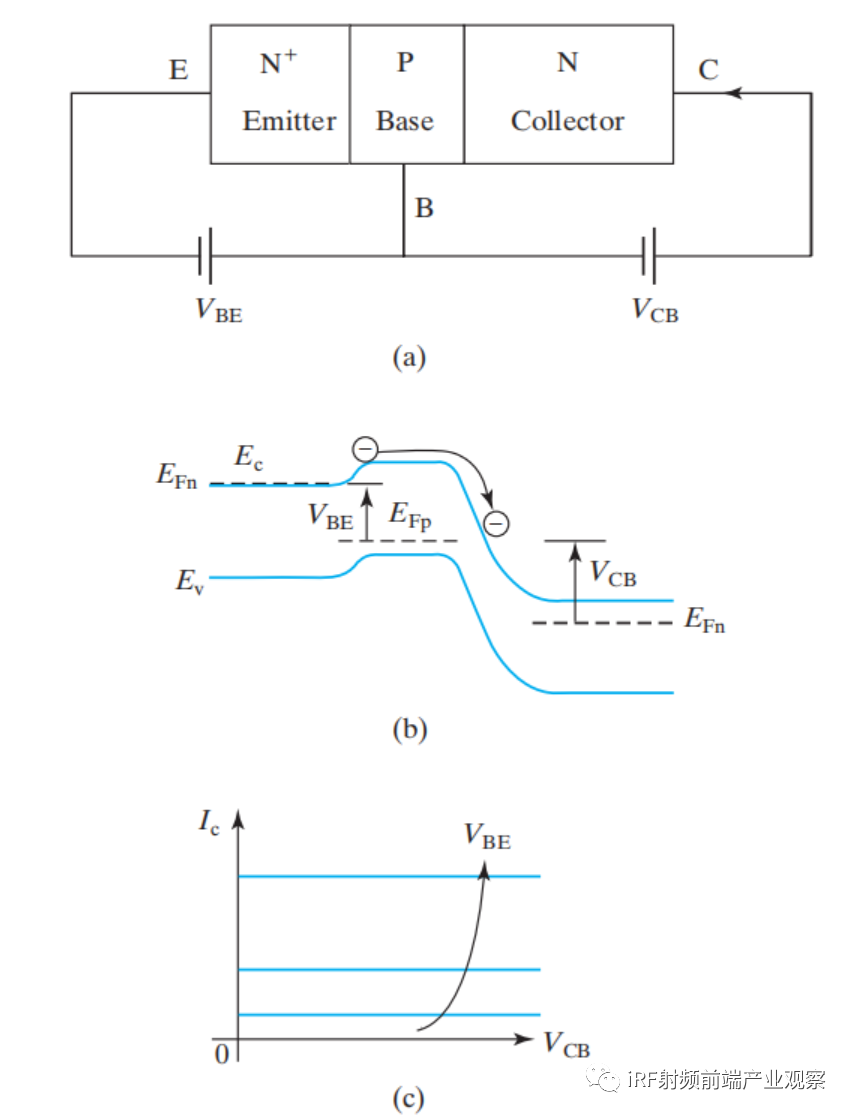

熟透双极性晶体管(BJT) 轻松做手机射频PA

MOS晶体管I-V特性

MOS晶体管I-V特性

评论