多核、超线程和高速 DMA 等现代处理器功能旨在优化平均案例执行时间。但是,这些优化通常以牺牲最坏情况的执行时间为代价,并使系统更难绑定。这种情况给安全关键型软件的开发人员带来了重大挑战,他们必须针对最坏情况进行设计。因此,以下讨论探讨了为什么在软件开发过程中关注最坏情况的行为,以及安全关键软件开发人员面临的一些与处理器相关的关键挑战以及解决这些问题的方法。

为什么要关注最坏的情况行为?

在安全关键型软件环境中,必须确保三个关键事项:

首先,每个周期线程(或任务)必须始终以其定义的速率(例如,100 Hz)执行。这很重要,因为每个线程必须以给定的速率执行,否则系统可能会变得不稳定,因此不安全。

其次,必须为每个周期线程分配一个不能超过的固定时间预算(例如,100 Hz 时为 200 微秒)。这很重要,因为它允许底层 RTOS 强制执行时间分区。

第三,每个周期线程的固定时间预算必须足以覆盖线程的最坏情况行为。这很重要,因为许多安全关键线程必须在每个周期内执行以完成。否则,系统可能会变得不稳定,从而导致不安全。

请注意,这组要求与非关键软件系统形成鲜明对比,在非关键软件系统中,人们希望整体性能处于最高水平,但可以容忍性能低于平均水平的偶尔“故障”。

多核和缓存/内存争用

自 1985 年以来,CPU 吞吐量大约每 18 个月翻一番,这与摩尔定律一致。然而,由于三个关键因素,这一趋势在2005年左右开始放缓。主要原因是内存速度跟不上CPU性能,在同一时间段内每年仅增加约10%。较大的缓存有助于缓解此问题,但内存子系统仍然是重要的性能瓶颈。

从理论上讲,更高的并行性应该通过使CPU能够同时处理多个指令来提高峰值性能。然而,流水线、分支预测和推测执行等技术已经开始“碰壁”,这使得利用这种并行性变得越来越困难。

散热因素也减缓了 CPU 吞吐量的推进速度。随着工作频率的增加,功耗和发热也会成比例地增加。在许多环境中,散发这种热量提出了艰巨的挑战,特别是对于被动冷却的嵌入式系统。

最近,多核处理器已经发展到可以应对其中的许多挑战。例如,为了提高内存吞吐量,每个 CPU 内核都配备了自己的 L1 缓存。更紧密的物理封装还通过缩短内核之间的信号运行来提高性能,从而使数据传输成比例地更快、更可靠。同时,多内核使处理器能够在每个时钟周期执行更多指令。这使得每个内核都能以较低的频率运行,从而消耗更少的功率并产生更少的热量。

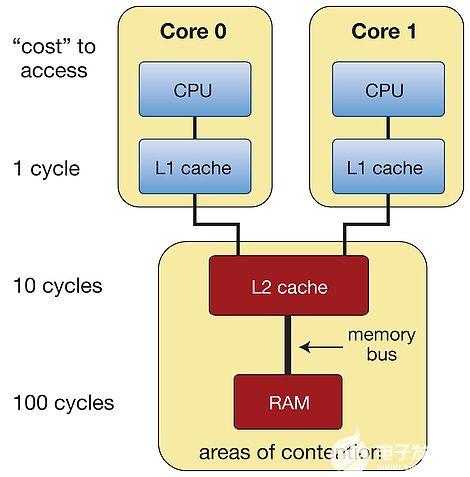

尽管取得了这些进步,但多核处理器仍然给安全关键型软件的开发人员带来了挑战:主要是对二级缓存和内存子系统等共享资源的争用增加。图 1 显示了一个简单的双核处理器,每个内核都有自己的 CPU 和 L1 缓存,两个内核共享一个 L2 缓存和一个 RAM 子系统。

图1:一个简单的双核处理器,每个内核都有自己的CPU和L1缓存,两个内核共享一个L2缓存和一个RAM子系统

左侧列出的值表示每个 CPU 在访问给定资源时产生的“成本”。例如,假设 CPU 访问其本地 L1 缓存需要一个周期。如果访问未命中,并且 CPU 必须转到 L2 缓存,则需要 10 个周期。如果二级缓存未命中并且CPU必须转到RAM,则成本为100个周期。如果缓存“脏”并且需要“回写”,则性能会更差。请注意,这些数字并不准确,并且会因处理器而异,但相对数量级是典型的。重要的一点是,CPU 访问数据的距离越远,数据传输所需的时间就越多。

当 CPU 上的多线程进程同时争用该内核的 L1 缓存时,以及当多个内核同时竞争共享的 L2 缓存和内存子系统时,就会发生争用。即使使用单核处理器,CPU 也很容易使内存子系统不堪重负。在多核系统中,多个内核必须争用共享内存资源,内存访问瓶颈要严重得多。

松弛调度和缓存分区

开发人员可以减少内存争用并利用多核的强大功能,同时仍满足最坏情况的执行要求的一种方法是利用针对安全关键型应用程序优化的实时操作系统。例如,DDC-I 的 Deos 提供缓存分区和松弛调度功能,可缓解内存访问瓶颈,增强确定性,并提高跨一个或多个内核的安全关键应用程序的 CPU 利用率。

缓存分区使设计人员能够将一部分缓存专用于每个内核,从而减少内存争用和最坏情况下的执行时间。通过这种物理分区,每个核心可用的缓存总量将减少。但是,由于多个内核不再共享同一资源,因此总体争用减少了。

同时,Slack 调度利用了平均线程执行时间通常比最坏情况执行时间短得多的事实。对于那些实际执行时间小于最坏情况预算时间的线程,RTOS回收未使用的时间并将其重新分配给其他线程,从而提高整体系统性能。

超线程 (HT)

HT 允许通过复制存储特定应用程序状态的处理器部分而不复制处理器的主处理引擎 (CPU) 来提高计算的并行化。这样,HT 处理器在 RTOS 中显示为两个逻辑处理器。超线程技术还可用于多核设置,其中每个内核有两个逻辑内核。

超线程处理器的优点是提高了应用程序代码的并行化,并缩短了反应和响应时间。例如,与非HT处理器相比,某些HT处理器的性能提高了30%。不幸的是,使用安全关键型软件很难实现此性能,因为 HT 增加了对缓存和内存子系统的争用,并使系统更难绑定。因此,在许多安全关键应用中必须禁用HT。

动态频率缩放 (DFS)

DFS(也称为 CPU 节流)允许实时调整处理器时钟的频率,以节省功率或减少芯片产生的热量。虽然DFS主要用于电池供电的移动设备,但也可用于被动冷却的航空电子系统,该系统必须仅使用环境空气来满足严格的热分布。DFS通常与动态电压调节(DVS)结合使用,因为频率与工作电压成正比,功耗随着电压的平方而增加。

DFS 和 DVS 可以节省功耗并减少热量,但在安全关键环境中,它们存在问题,因为它们还可以减少处理器在给定时间内可以发出的指令数量(包括减慢内存总线访问速度)。因此,性能可能会以难以绑定的不可预测的方式降低。如果功耗不是门控因素,则可以禁用 DFS 和 DVS。或者,想要利用DFS和DVS的设计人员可以通过测量最坏情况的性能来实现,同时在较低频率/电压下运行处理器,然后相应地进行预算。

直接内存访问 (DMA)

DMA 允许设备在不涉及 CPU 的情况下将大量数据(包括地图显示和地形数据库)移入和移出系统内存,从而提高性能,从而释放 CPU 以执行其他工作。对于安全关键型软件,DMA 的主要缺点是它在 CPU 和内存管理单元 (MMU) 的控制之外运行。因此,DMA 控制器中的缺陷可能会破坏空间分区。缓解此问题的一种方法是将RTOS与满足最高设计保证的特殊DMA控制器软件一起使用。

在像Deos这样的RTOS的帮助下,安全关键型系统的设计人员可以获得具有多核、高速DMA和DFS的高级处理器的性能优势,而不会影响最坏情况下的执行时间。然而,并非所有高级处理器功能都非常适合安全关键型应用。有些(如超线程)虽然是提高平均性能的理想选择,但只是缺乏安全关键应用程序所需的确定性,必须禁用。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20148浏览量

247050 -

cpu

+关注

关注

68文章

11216浏览量

222912

发布评论请先 登录

关于协处理器自定义指令的实现

云拼接处理器的性能如何?

DS5003安全微处理器芯片技术手册

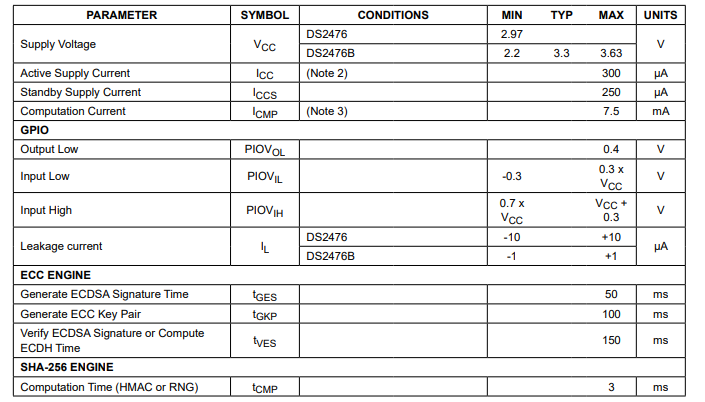

DS2476 DeepCover安全协处理器技术手册

解决安全关键型软件的处理器挑战

解决安全关键型软件的处理器挑战

评论