在过去 30 年中,缓冲区溢出一直是网络传播的攻击中最常被利用的漏洞。考虑到缓冲区的创建方式,这并不奇怪。

下面是 C 语言中的一个示例:

步骤 1.程序员使用 malloc 函数并定义缓冲区内存量(例如 32 字节)

步骤2.返回一个指针,指示内存中缓冲区的开始

第3步。程序员在需要读取或写入该缓冲区时使用指针(仅)作为引用

有了指针,程序员很容易忘记分配给给定缓冲区的实际内存量。编译器使用元数据在组装过程中分配适当的缓冲区大小,但此元数据通常在生成时被丢弃以减少占用空间。

如果程序内或程序之间传输的数据随后超出了最初定义的缓冲区大小,则该数据信息将覆盖相邻的内存。这可能导致内存访问错误或崩溃,以及安全漏洞。

缓冲区溢出和漏洞利用

黑客可以使用堆栈缓冲区溢出将可执行文件替换为恶意代码,从而允许他们利用堆内存或调用堆栈本身等系统资源。例如,控制流劫持利用堆栈缓冲区溢出将代码执行重定向到正常操作中使用的位置以外的位置。

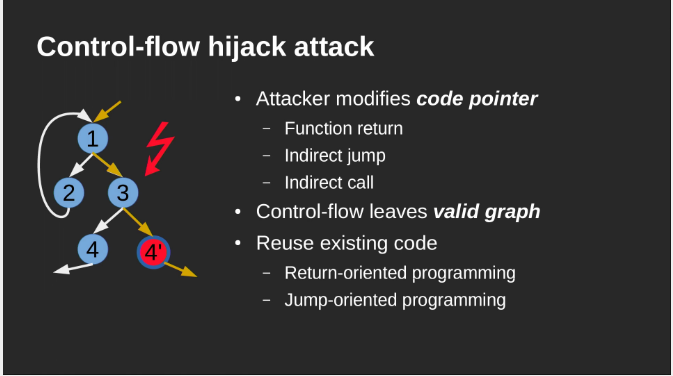

一旦负责控制流, 控制流劫持者可以修改指针和重用现有代码, 同时也可能替换代码。控制流的命令还允许攻击者修改指针以用于间接调用、跳转和函数返回,从而留下有效的图形以向防御者隐藏其操作。

图 1.控制流劫持是一种常见的攻击,它利用缓冲区溢出来征用系统堆栈。

尽管动态地址空间布局随机化 (ASLR) 机制和堆栈 Canaries 用于在代码执行发生之前检测和防止缓冲区溢出,但此类威胁仍然是一个挑战。

安全性:软件还是芯片?

ASLR 和堆栈 Canary 是基于软件的缓冲区溢出保护机制,它们确实使攻击者更难利用缓冲区溢出。例如,ASLR动态地重新定位内存区域,以便黑客必须有效地猜测目标组件(如基本可执行文件,库以及堆栈和堆内存)的地址空间。不幸的是,最近的漏洞,如幽灵和崩溃泄漏来自CPU分支预测器的信息,这限制了ASLR的有效性,原因显而易见。

另一方面,堆叠金丝雀在内存中返回指针之前插入小整数。检查这些整数以确保它们在例程可以使用相应的返回指针之前未发生更改。尽管如此,黑客仍有可能读取金丝雀,如果他们确定包含正确的金丝雀值,则可以简单地覆盖它和随后的缓冲区而不会发生事故。此外,虽然 Canary 保护控制数据不被更改,但它们不保护指针或任何其他数据。

当然,基于软件的安全解决方案的另一个挑战是它们非常容易受到错误的影响。据估计,每1000行代码存在15-50个错误,这意味着解决方案中存在的软件越多,漏洞的数量就越多。

当解决疾病而不是缓冲区溢出的症状时,一种更强大的方法是在硅中实现安全性 - 虽然堆栈缓冲区溢出利用旨在操纵软件程序,但解决此类攻击的根本原因始于意识到处理器无法确定给定程序是否正确执行。

除了减轻软件错误的影响之外,硅不能远程更改。但是,必须对处理器或芯片IP进行编程,以便在运行时识别尝试写入内存或外围设备的指令是否在执行合法或非法操作。

多佛微系统公司开发了这样一种名为CoreGuard的技术。

运行时的硅安全性

CoreGuard 是一块芯片 IP,可以与 RISC 处理器架构集成,以便在运行时识别无效指令。该解决方案以 RTL 形式提供,可针对各种功率和面积要求进行优化,或进行修改以支持自定义处理器扩展。

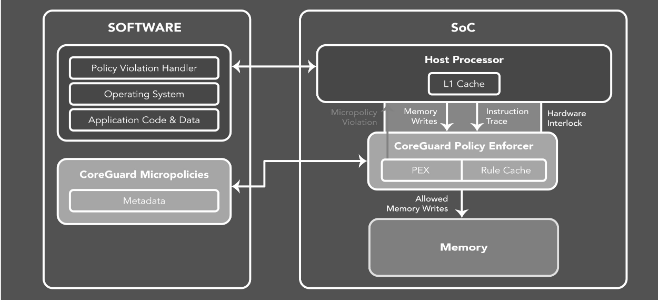

如图 2 所示,CoreGuard 体系结构包括一个硬件互锁,用于控制主机处理器与系统其余部分之间的所有通信。硬件互锁将这些通信汇集到策略实施器中。

图 2.多佛微系统的CoreGuard安全IP使用微策略和硬件联锁来识别和阻止无效指令,然后再执行。

另外,CoreGuard 使用称为微策略的可更新安全规则,这些规则是用高级专有语言创建的简单管理策略。这些规则安装在与其他操作系统或应用程序代码隔离的安全、不可访问的内存区域中。CoreGuard 还在此处为通常被编译器丢弃的应用程序元数据保留了少量内存分配,用于为系统中的所有数据和指令生成唯一标识符。这些组件在系统引导时加载。

当指令尝试在运行时执行时,以特权模式运行的 CoreGuard 策略执行核心或主机处理器会根据定义的微策略交叉引用指令的元数据。硬件互锁确保处理器仅向存储器或外设输出有效指令,从而防止无效代码完全执行。应用程序会收到类似于被零除错误的策略违规通知,并通知用户。

与主机处理器集成所需的一切,以支持指令跟踪输出、失速输入、不可屏蔽中断 (NMI) 输入和中断输出。对于非芯片设计人员,多佛微系统公司最近宣布,其CoreGuard技术正在被设计到某些恩智浦处理器中。

消除攻击类别

在缓冲区溢出的情况下,像CoreGuard这样的技术的好处是显而易见的。可以合并作为经常丢弃的编译器元数据的一部分捕获的缓冲区大小,以限制攻击者从整个网络操作系统堆栈的能力。更进一步,相同的原则通常可以应用于控制流劫持,因为从内存中的各个点返回可以在发生之前受到限制。

在实践中,这种实时感知也为安全行业创造了一个新的竞争环境。通过在损坏发生之前识别错误或攻击,用户可以选择动态重新分配内存,切换到单独的,更安全的程序或记录事件,同时继续运行相同的程序。如何继续完全取决于应用程序或业务案例的需求。

审核编辑:郭婷

-

cpu

+关注

关注

68文章

11216浏览量

222944 -

编译器

+关注

关注

1文章

1669浏览量

51082 -

IOT

+关注

关注

189文章

4369浏览量

206584

发布评论请先 登录

CW32L052串口的缓冲区机制

飞凌嵌入式ElfBoard-标准IO接口之设置缓冲区

移植的lvgl,在运行的时候,缓冲区无法释放怎么解决?

请问USB缓冲区取数据可以多次取吗?

socket缓冲区溢出的原因?怎么解决?

解析RZ/N2L CANFD模块的缓冲区机制(2)

FX3 Socket缓冲区切换的最大时间是多少?

在传输DMA通道中的所有缓冲区后,DMA标志(就绪和部分)被卡住了是怎么回事?

求助,关于3014的缓冲区设置疑问求解

请问如何在Linux中使用帧缓冲区更新epdc显示?

FreeRTOS进阶使用之流缓冲区:高效处理字节流的秘密武器

缓冲区溢出漏洞的原理、成因、类型及最佳防范实践(借助Perforce 的Klocwork/Hleix QAC等静态代码分析工具)

RTOS的流缓冲区机制解析

消除IoT上的缓冲区溢出漏洞

消除IoT上的缓冲区溢出漏洞

评论