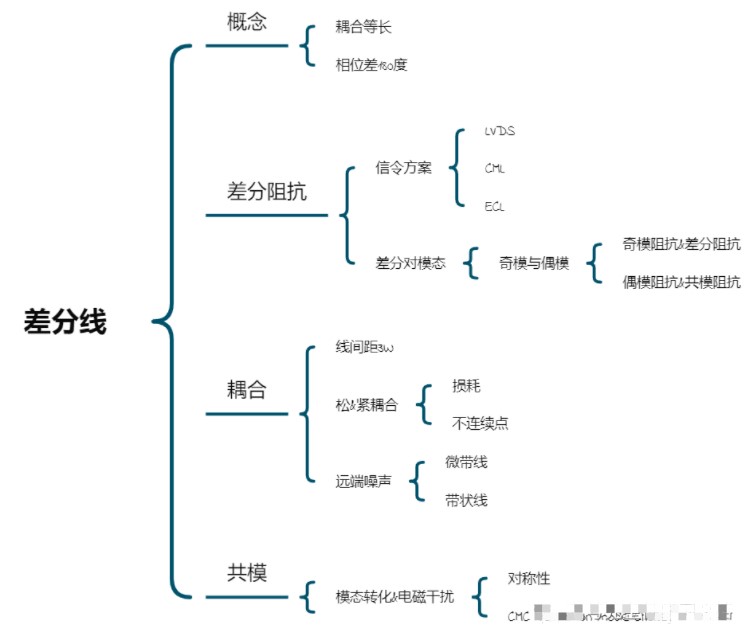

整个基础知识体系中,差分线(对)是很难搞的部分,却是最常用的部分。说到差分线基础知识,里面的概念很多,记得刚接触的时候,奇模&共模有时候会搞不清楚。话不多说,直接上图:

1、概念

差分线从理论上说,可以是任意两根传输线。

最初的时候,曾有疑惑:距离很远的两根传输线呢?实际工作中,很多高速线都是差分线,更多的是利用其抗干扰的能力。既然讲到抗干扰,那是不是尽量保证两根线的周围环境一致。

所以,差分线的定义:两条存在耦合且平行等长的两根传输线,用来传输相位差180度的信号。

2、差分阻抗

差分线本身没有什么特别,决定它们特性的是这两条传输线上的信号传输方式。差分线除了传输差分信号,还有共模信号,前一种是大小相等方向相反的驱动电压,后一种是相等方向相同的驱动电压。

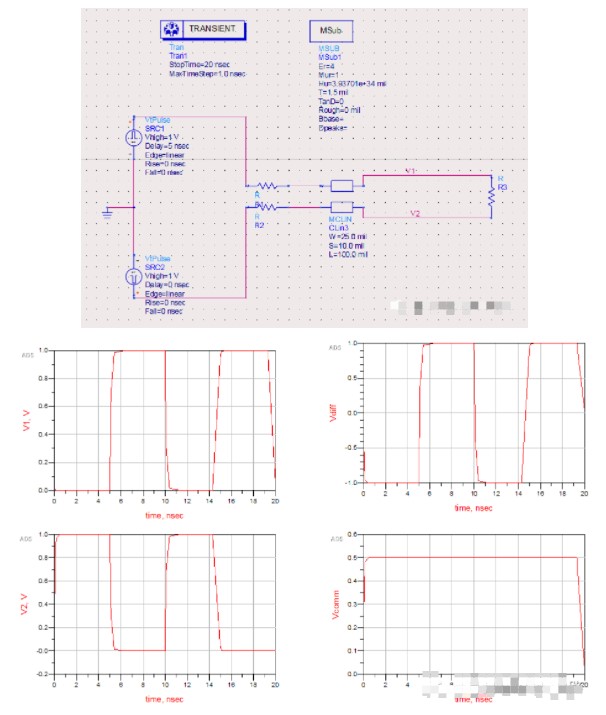

为了方便理解,针对差分阻抗的特性,搭建相关链路:

Vdiff = V1–V2 Vdiff 表示差分线号

Vcomm= (V1+V2) Vcomm表示共模信号

V1表示线1相对于其返回路径的信号电压

V2表示线2相对于其返回路径的信号电压

从仿真结果看出:相同电平的幅值,差分线的峰峰值是单端线的两倍。单端线的基准是地平面,外界的干扰差异会很大;而差分线的基准是彼此,对共模干扰有很好的抑制。

差分线最重要的电特性就是对差分信号的阻抗,称为差分阻抗。

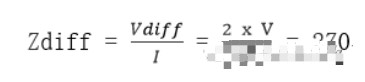

以Z=V/I来推算:

Z0单端信号线的特性阻抗

差分阻抗还可以看成两条单端信号线等效阻抗的串联:

Zdiff = Z0 +Z0 = 2 x Z0

Zdiff 表示两条信号线之间的等效阻抗(即差分阻抗)

Z0 表示每条信号线与返回路径之间的阻抗

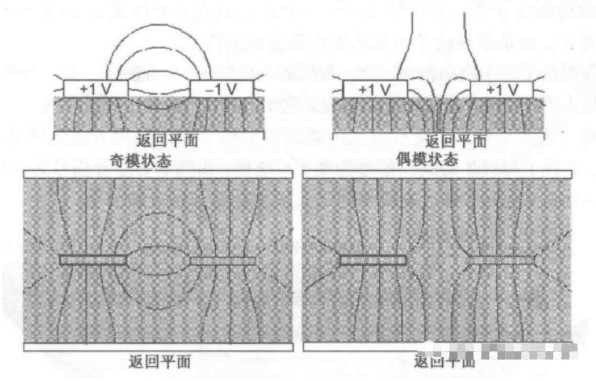

上面计算方法可以得出差分阻抗,由差分阻抗引出两种模态:

奇模阻抗

奇模阻抗与差分阻抗有直接的关系。差分阻抗是差分信号受到的阻抗,奇模阻抗是传输线处于奇模状态时每条信号线的阻抗。

偶模阻抗

共模信号使差分对处于偶模状态。当传输线上传播共模信号时,此时每条线的特性阻抗称为偶模特性阻抗。

对于共模信号而言,阻抗是每条线特性阻抗的并联。两个偶模阻抗的并联阻值:

Zcomm表示共模阻抗

Zeven表示当差分对处于偶模状态时每条线的特性阻抗

信令方案有多种,最常用的就是LVDS低压差分信号。

需要注意的是:LVDS 信号不仅有差分信号还有共模信号,只不过默认共模信号是没有变化的直流。

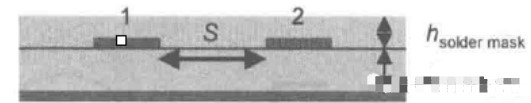

除了常规的线宽线距,介质厚度等因素对差分阻抗的影响。最近有写阻焊相关的发明,发现随着阻焊层厚度的增加,紧耦合的情况下,阻焊层对奇模阻抗影响比较大,差分阻抗偏离值高达10%。设计表面层信号线差分阻抗时要考虑阻焊层的原因,这也是为什么差分线建议走内层的原因之一。

上面讲的概念都是无耦合的情况,如果考虑耦合,就引入了共模干扰的问题。

3、耦合

写到耦合的时候,想起之前有和同事聊过:关于差分线,因为相互耦合,一条线的返回路径可不可以是另外一条线?

当地平面发生不连续的时候,无参考平面的区域,差分走线之间的耦合才会提供主要的回流通路。这是没有任何问题的。

其实上面说差分线的一条线的返回电流由另一条线传输,还有一个前提条件:当信号线与返回路径平面之间的距离大于等于两条信号线距离(包含线宽)。

但是共模信号怎么办?不给共模信号提供地阻抗回路,势必会造成EMI 辐射,引入电磁干扰。相互作为回流路径的做法弊大于利。

在实际工作中,大多数板级互连中,信号线与平面之间的耦合度远大于两条信号线之间的耦合度,所以此时平面的返回电流十分重要。此时,第一条信号线的返回电流不能看成由第二条信号线运送。

线间距3倍线宽(3W)的情况,耦合很小,可以忽略。考虑两条线之间的耦合,当线间距的减小,奇模阻抗减小,偶模阻抗增加,对应的差分阻抗减小,共模阻抗增加。相对于3W的情况,差分阻抗减小了约12%。

远端串扰

如果差分对为同介质的,比如带状线,两种模态的传播速度相同,差分对就不会出现远端噪声。如果差分对为不同介质的,比如微带线,那么奇模的有效介电常数比偶模小,奇模有更快的传播速度。差分信号分量比共模分量先到达末端,相互间造成远端噪声。

紧耦合与松耦合

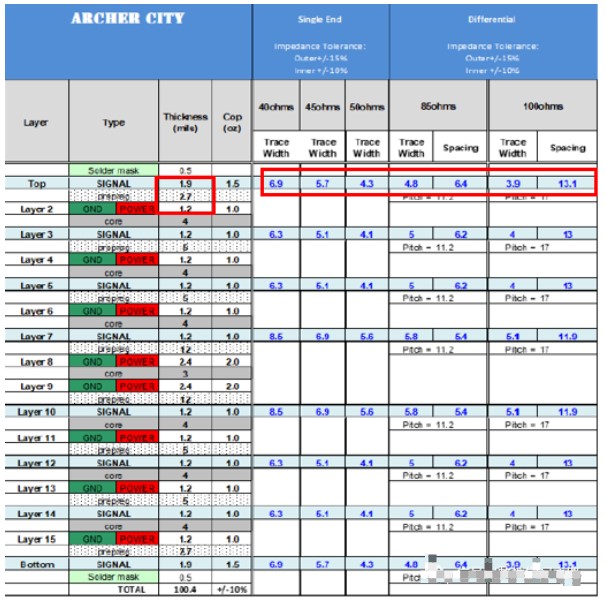

下图为阻抗计算软件算出差分阻抗为85 Ω,线间距差别比较大:

一般松耦合经验值为线间距大于2倍的线宽

返回平面受损时,例如在双绞线电缆、带状电缆、连接器和一些集成电路封装中,使用紧耦合。紧耦合对减小串扰有很强的作用。

紧耦合情况下,差分阻抗和共模阻抗受耦合的影响依然很小。在最紧耦合下,差分阻抗仅减小了10%。

一般规则:高速率产品,损耗要求较严,应当使用松耦合的差分对。消费类产品,成本要求较严,应使用紧耦合的差分对。

4、共模信号

我们主要用差分线传输差分信号,但在实际的链路中,任何不对称因素(串扰、驱动器错位、线长偏差及不对称的负载等)都会使部分差分信号转化为共模信号。

共模信号的产生及改变,危害就是会引起误码,引入过量电磁干扰。消费类的产品,一般都进行相关电磁辐射测试,这就需要我们在实际工作中进行管控。如何使共模信号的影响降到最小:

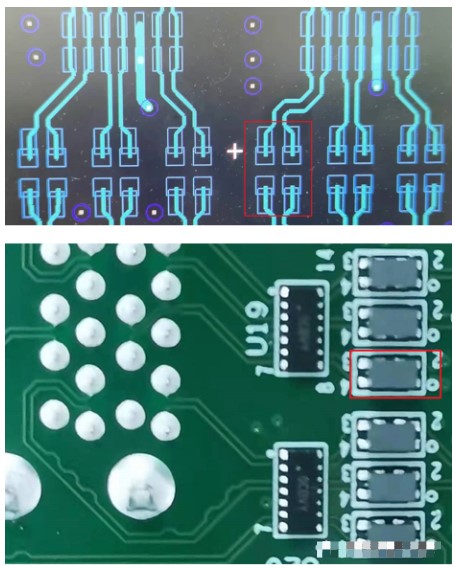

1.链路做到尽量对称。过孔转换&等长匹配&出Pin区域等。

2.增加共模信号扼流器CMC(Common mode Choke),起到EMI滤波的作用,用于抑制高速信号线产生的电磁波向外辐射发射。

实际应用

讲到电磁干扰,还有一种情况需要说明:双绞线是否使用屏蔽?

屏蔽对差分阻抗影响其实不大,屏蔽的重要作用在于为共模电流提供一个返回路径,从而减小它的辐射效应。

审核编辑:刘清

-

lvds

+关注

关注

2文章

1216浏览量

69113 -

差分阻抗

+关注

关注

1文章

27浏览量

10594 -

共模信号

+关注

关注

1文章

92浏览量

14552 -

差分线

+关注

关注

0文章

39浏览量

9216 -

驱动电压

+关注

关注

0文章

100浏览量

13909

发布评论请先 登录

差分线是如何去定义的呢

差分线是如何去定义的呢

评论