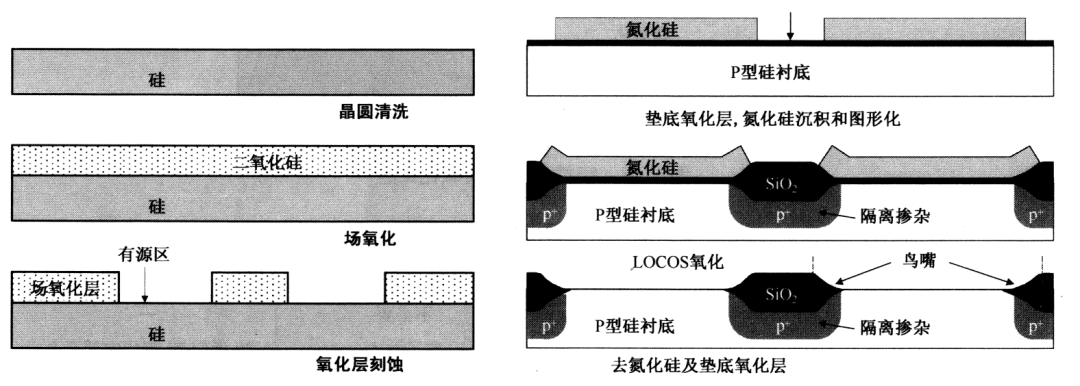

热生长的二氧化硅最重要的应用之一是形成绝缘体使IC芯片上相邻晶体管间电气隔离。整面全区覆盖式氧化和局部氧化是隔离相邻元器件并防止它们相互干扰所用的两种技术。整面全区覆盖式氧化层是最简单的隔离工艺,早期的半导体生产普遍使用这种技术。热生长一层5000-10 000A的二氧化硅,通过光刻技术使其图形化,再用氢氟酸刻蚀氧化层,接着将器件区打开后就可以开始晶体管的制造过程了(见下图)。

硅局部氧化(LOCOS)的隔离效果比整面全区覆盖式氧化效果好。LOCOS工艺使用一层很薄的二氧化硅层200-500A作为衬垫层以缓冲LPCVD氮化硅的强张力。经过氮化硅刻蚀、光刻胶剥除和晶圆清洗后,没有被氮化硅覆盖的区域再生长出一层厚度为3000〜5000 A的氧化层。氮化硅的阻挡效果比二氧化硅好,由于氧分子无法穿过氮化硅层,所以氮化硅层下的硅并不会被氧化。而未被氮化硅覆盖的区域,氧分子就会不断扩散穿过二氧化硅层与底层的硅形成更厚的二氧化硅。LOCOS的形成过程如下图所示。

由于氧在二氧化硅中的扩散是一种等向性过程,所以氧也会碰到侧边的硅。这使得 LOCOS工艺有两个缺点:一个缺点是靠近刻蚀氧化窗口的氮化硅层底生长有氧化物,这就是所 谓的鸟嘴(Bird?sBeak)(见下图)。鸟嘴占据了晶图表面的很多面积,是应尽量避免出现的情况。另一个缺点是由于氧化物的生长特点而形成氧化层对硅有一个表面台阶,这将引起表面平坦化问题。

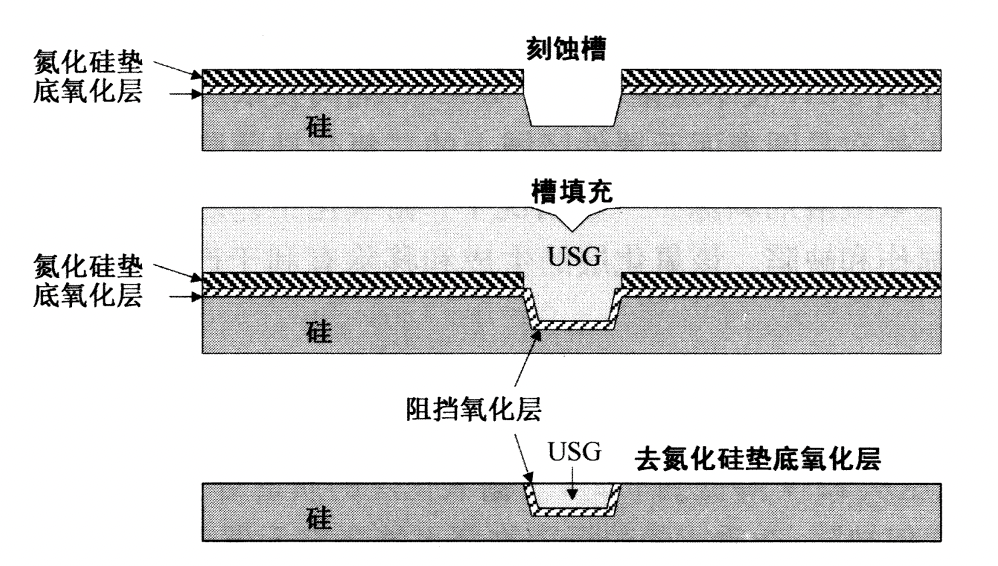

已经采用了许多方法抑制鸟嘴效应,其中最普遍的是多晶硅缓冲层(Poly Buffered LOCOS, PBL)T艺。较厚的衬垫层形成较长的鸟嘴,这使得氧分子扩散的路径变得较宽。使用一层厚度大约为500 A的多晶硅缓冲LPCVD氮化硅的高张力,衬垫氧化层的厚度能从500 A降低到 100 A,从而可以大大减小氧化物的侵入。但是硅的局部氧化层两侧总有0. 1〜0.2um的鸟嘴。当最小图形尺寸小于0.35um时,鸟嘴问题变得很严重,于是发展出了浅沟槽隔离(STI)工艺以避免鸟嘴效应,STI形成的表面也比较平坦。20世纪90年代中期,当元器件图形尺寸缩小到0. 35um以下时,STI技术逐渐取代了LOCOS隔离技术。

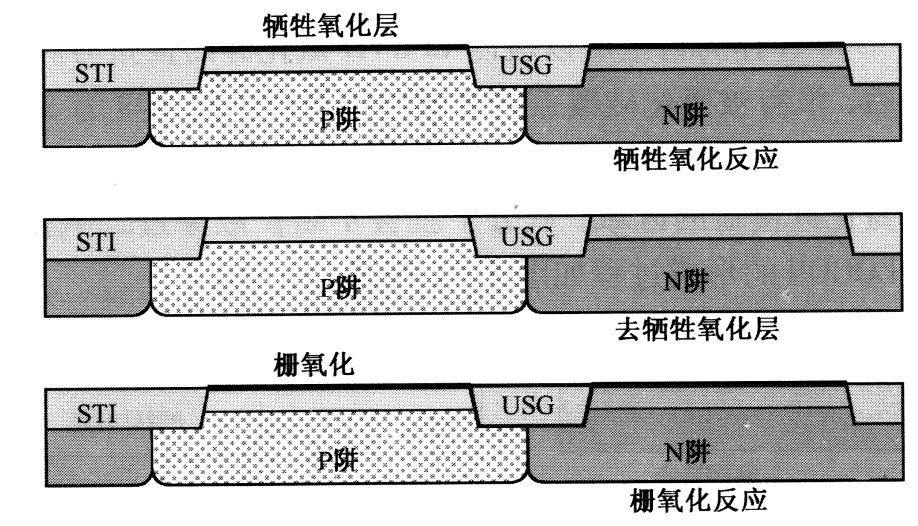

牺牲氧化层是生长在晶圆表面元器件区域上的二氧化硅薄膜(低于1000 A)o牺牲氧化层生成之后将立刻被氢氟酸溶剂剥除。一般情况下,栅氧化工艺之前都将先生长一层牺牲氧化层来移除硅表面的损伤和缺陷。该氧化层的生成和移除有利于产生零缺陷的硅表面并获得高质量的栅氧化层。

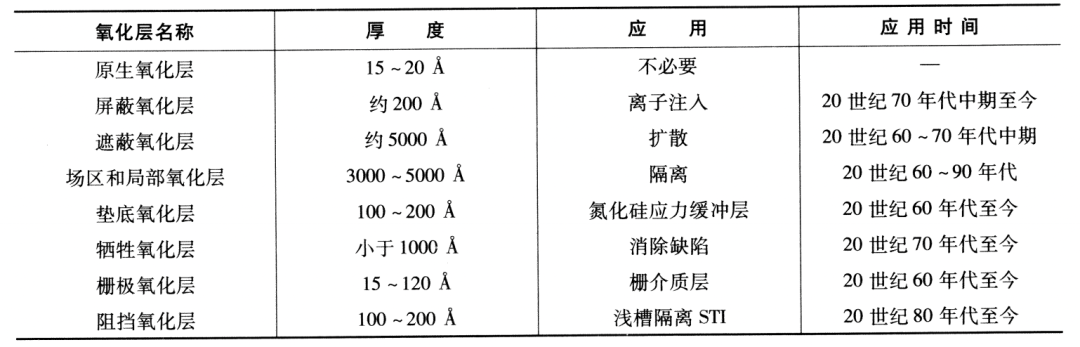

以MOS为主的IC芯片,其最薄也最重要的二氧化硅层是栅氧化层。由于元器件尺寸不断缩小,栅氧化层从20世纪60年代大于1000 A厚度降低到2000年复杂芯片上的15 A左右,而且IC芯片的工作电压从12 V降低到1.2 Vo栅氧化层的质量对于元器件能否正常工作非常重要,栅氧化层中的任何缺陷、杂质或微粒污染物都可能影响元器件的性能,并且显著降低芯片的成品率。下图说明了牺牲氧化层和栅氧化层的形成过程,下表列出了 IC生产中应用热生长的二氧化硅情况。

审核编辑 :李倩

-

半导体

+关注

关注

339文章

31279浏览量

266689 -

晶体管

+关注

关注

78文章

10443浏览量

148676 -

IC芯片

+关注

关注

8文章

267浏览量

28234

原文标题:半导体行业(一百二十三)——加热工艺(四)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体制造中的侧墙工艺介绍

原子级洁净的半导体工艺核心是什么

半导体行业案例:晶圆切割工艺后的质量监控

高精度半导体冷盘chiller在半导体工艺中的应用

从原理到应用,一文读懂半导体温控技术的奥秘

大模型在半导体行业的应用可行性分析

苏州芯矽科技:半导体清洗机的坚实力量

半导体制冷机chiller在半导体工艺制程中的高精度温控应用解析

什么是半导体行业用的面板系列Panel Chiller?

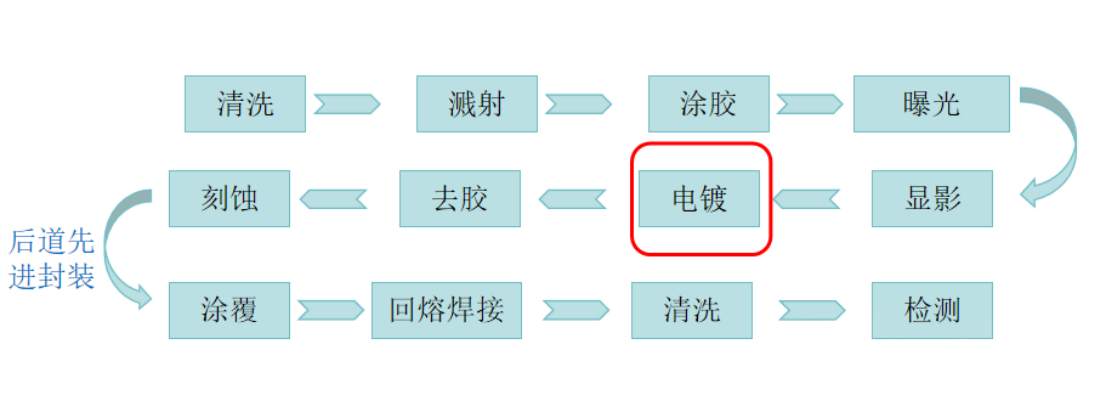

揭秘半导体电镀工艺

半导体行业——加热工艺解析

半导体行业——加热工艺解析

评论