在 CacheQ 编译器集合中,编译器消除了手动代码重写和使用线程库或复杂的并行执行 API,如 OpenMP 或 MPI。它采用单线程 C 代码并生成可在 CPU 上运行的可执行文件,利用带或不带超线程的物理 x86 内核以及 Arm 和 RISC-V 内核。

使用 CacheQ 灵活的编译器,用户可以为相同或不同架构上的多核处理器生成代码,并使用运行时变量对使用情况进行基准测试。它们可以添加到硬件以提高性能和功耗,或减少内核数量并分配其他进程以实现每瓦功耗的更优化性能。

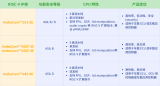

根据该公司的说法,基于模拟股票交易中人类行为的 Black Scholes 金融算法的基准,结果是在具有 12 个逻辑内核的 X86 处理器上的单线程执行速度提高了 486% 以上。具有八个 Arm 内核的 Apple M1 处理器比单线程 GNU 编译器集合 (GCC) 快 400%。

CacheQ 使软件开发人员能够为包括 FPGA、CPU 和 GPU 在内的异构计算系统开发和部署定制硬件加速器。它的 CacheQ Compiler Collection 以 gcc 工具套件为模型,包括类似于常见开源编译器的用户界面。因为它需要有限的代码修改,所以可以缩短开发时间并提高系统质量。

该工具套件支持对生成的虚拟引擎进行编译、检查和错误检测、性能预测、分析、调试和可视化。它支持目标硬件,包括单核和多核处理器,以及具有连接到 x86 和 Arm 处理器的 FPGA 加速器的异构计算系统。

CacheQ 编译器集合通过导出函数调用的“混合”访问来支持 C 代码和 C++。

CacheQ Compiler Collection 的其他基准测试突出了其跨越高端服务器和消费电子设备的能力。具有两个内核的 M1 处理器的执行性能优于具有 11 个内核的 x86 芯片,显示出每瓦成本的优势。据该公司称,四核 Apple M1 处理器的性能比 12 核 x86 快 210%。总体而言,它的执行速度比使用 CacheQ 编译器集合在 x86 上运行的单线程 GCC 快约 1,476%。

所有模拟都是在为不同目标编译的相同代码上执行的。基准测试是在运行频率为 3.7GHz 的 Intel i7-8700k x86 CPU 上执行的,该 CPU 具有六个物理内核和超线程,可用于运行 Ubuntu 18.04 的 12 个逻辑内核。Apple M1 基准测试是使用运行本机 Arm Ubuntu 20.04 映像的 Parallels VM 捕获的。

审核编辑:郭婷

-

FPGA

+关注

关注

1663文章

22494浏览量

638984 -

C++

+关注

关注

22文章

2127浏览量

77357 -

编译器

+关注

关注

1文章

1672浏览量

51895

发布评论请先 登录

寻找对RISCV众核并行计算感兴趣的伙伴、朋友

寻找对RISCV众核并行计算感兴趣的伙伴

摩尔线程正式开源TileLang-MUSA项目

Linux多线程对比单线程的优势

开源鸿蒙技术大会2025丨编译器与编程语言分论坛:语言驱动系统创新,编译赋能生态繁荣

rt-thread studio 如何进行多线程编译?

兆松科技ZCC-FuSa编译器全面支持晶心科技车规级RISC-V处理器IP核

进迭时空同构融合RISC-V AI CPU的Triton算子编译器实践

边缘设备AI部署:编译器如何实现轻量化与高性能?

兆松科技ZCC编译器全面支持芯来科技NA系列处理器

RISC-V架构下的编译器自动向量化

CacheQ的编译器支持多线程CPU加速

CacheQ的编译器支持多线程CPU加速

评论