在ASIC中用到锁存器的地方很多,Time Borrowing是使用锁存器的典型应用之一,在深度流水线的设计中可以极大地提高处理性能。另外锁存器和寄存器相比能够显著的减小面积:寄存器占用的硅片面积是锁存器的两倍,在ASIC设计中一个典型的主从寄存器是由两个锁存器级联来实现的。

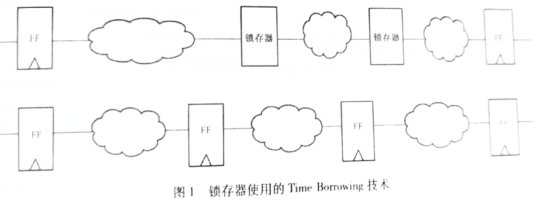

图1说明了如何使用锁存器的Time Borrowing技术来替代关键路径中的寄存器。通过重新分配相邻锁存器之间的组合逻辑延迟,从而延长最长路径的时钟周期。

对于Xilinx的 FPGA芯片来说,不管是锁存器还是寄存器,都是用相同的硬件资源实现的。这些硬件资源共享相同的数据输入/输出、复位和使能信号,可以配置成边沿触发的寄存器或者电平使能的锁存器。因此在 FPGA芯片中,无论是锁存器还是寄存器都使用相同的硬件资源,使用锁存器并不会带来任何的优势。

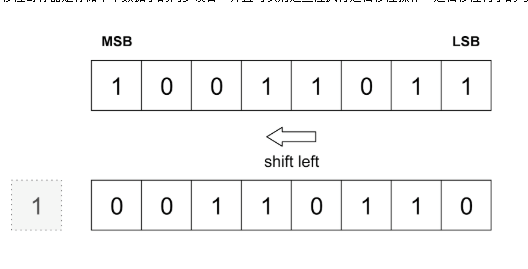

寄存器和锁存器关于数据的存储方面存在着根本的差异。锁存器属于电平敏感电路,当门使能信号有效时,输入数据将直接输出;而门使能信号无效时,数据保持到锁存器中。寄存器属于边沿敏感电路,数据只有在时钟的上升沿或者下降沿才会被保存到寄存器中。

虽然锁存器和寄存器使用相同的FPGA硬件资源,但还是要尽量避免使用前者。首先,当锁存器处于导通状态时,输入信号的毛刺会直接传递到后面的逻辑中;另外,对于静态时序分析工具来说、分析寄存器远远比锁存器简单得多。因为对于寄存器而言,只考虑到时钟的上升或者下降沿:对于锁存器而言,不仅需要考虑其上升沿和下降沿,而且还要考虑上、下沿之间的持续时间。对于具有周期性抖动的信号而言,锁存器常常会造成问题。而对于边沿敏感的寄存器,由于只需要关心时钟边沿的达到时间,因此即便是门使能的信号具有周期抖动,也不会造成任何的问题。ASIC设计中锁存器的Time Borrowing电路,对于FPGA结构来讲更是难以回避的挑战。由于某级流水线的延迟和前面所有流水线的延迟相关,这种流水线的高度相关性将使得静态时序分析更加难以处理,并且其困难程度和流水线的级数也不存在任何的线性关系。

正是因为上述原因,基于锁存器的设计需要更加仔细和周密的时序约束。对于基于锁存器流水线的逻辑综合和物理实现,更是要从整个芯片的角度去做分析,才能够正确地约束不同的时序关系。

因此在将ASIC 设计移植到FPGA时,最好就是将电平使能的锁存器转换为边沿触发的寄存器。这需要工程师投人许多的时间去分析和修改,因为不是所有描述锁存器的代码风格都能够通过同样的方式进行转换。

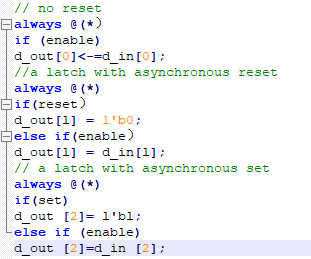

大多数商用综合工具都支持锁存器的设计,代码中的if语句如果缺少相应的case语句,将自动生成锁存器。

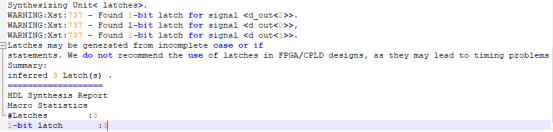

当Xilinx的综合工具XST 遇到锁存器之后,会产生以下类似的报告。

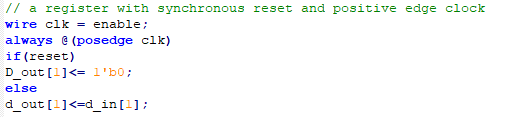

通过修改成综合工具所支持的代码风格,可以将锁存器转换成寄存器。下面通过一个简单的例子展示了其中的一种代码风格,可以将门使能信号转换成时钟信号。

当然也有其他一些代码风格,比如时钟可以使用上升沿或者下降沿(Xilinx的FPGA不支持双时钟沿)、同步或者异步的复位置位等。

原文标题:FPGA知识汇集-锁存器的移植

文章出处:【微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22516浏览量

639694 -

寄存器

+关注

关注

31文章

5621浏览量

130466 -

锁存器

+关注

关注

8文章

958浏览量

45494

原文标题:FPGA知识汇集-锁存器的移植

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何使用锁存器的Time Borrowing技术来替代关键路径中的寄存器

如何使用锁存器的Time Borrowing技术来替代关键路径中的寄存器

评论