本系列文章已突出介绍了连续时间Σ-Δ(CTSD)模数转换器(ADC)调制器环路的架构特性,这种架构能够简化ADC模拟输入端的信号链设计。现在讨论将ADC数据与外部数字主机接口以对此数据执行应用相关处理的简单但创新的方法。对任何应用而言,数字数据输出采样速率都是ADC信号链的一个关键参数。但是,不同应用有不同的采样速率要求。本文章介绍一种新型片内采样速率转换技术,其用在核心ADC的输出上,允许信号链设计人员以应用所需的采样速率处理ADC数字输出数据。

ADC的作用是对模拟输入信号进行采样,并将其转换为等效的数字格式。应用对数字数据做进一步处理所需的采样速率不一定与ADC对模拟信号进行采样的速率相同。每个应用都有独特的数字输出采样速率要求。采样速率转换器将ADC数据的输入采样速率映射为所需的输出采样速率。本文首先概述各种应用的采样速率要求,证明ADC需要支持广泛的输出采样速率。然后,本文快速回顾已知ADC架构中的传统采样速率转换技术及其缺点。接下来,本文介绍新颖的异步采样速率转换(ASRC),它能与任何ADC架构配对,以获得任何所需的输出采样速率,并用外部数字主机简化数字接口设计。

ASRC与CTSD ADC搭配可谓两全其美,不仅能简化ADC模拟输入端的信号链设计,也能简化数字输出端的信号链设计。

采样速率要求

驱动数字数据采样速率选择ADC的主要性能参数之一是ADC的预期精度。数字数据中的样本数量越多,对模拟输入的表示就越准确。但不利的一面是需要处理大量数据,外部数字主机接口设计的复杂度和功耗会提高。因此,每个应用根据所需的精度、功耗预算和设计复杂度以及计划的算法处理,决定了数字数据的采样速率。所需的大多数一般采样速率可以分类如下:

奈奎斯特采样速率

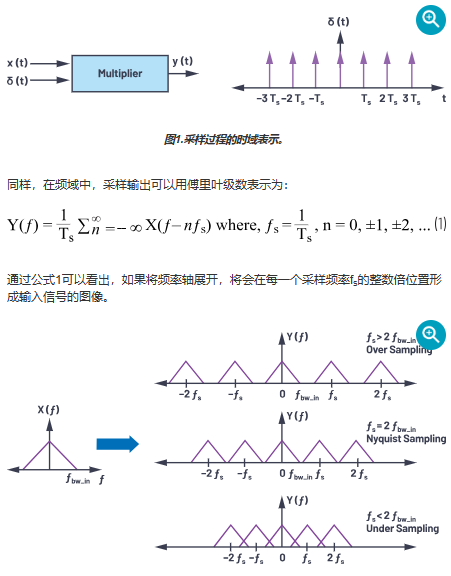

众所周知的奈奎斯特采样1准则指出:为了提供模拟输入的忠实数字表示,采样速率至少应为输入带宽的两倍。因此,奈奎斯特采样速率应用的数字采样速率为目标输入带宽的两倍。这种采样速率的一个众所周知的例子是CD上的数字音频数据存储,其速率为44.1 kSPS,而目标输入音频带宽最高为20 kHz,即人类听力的频率上限。

过采样速率

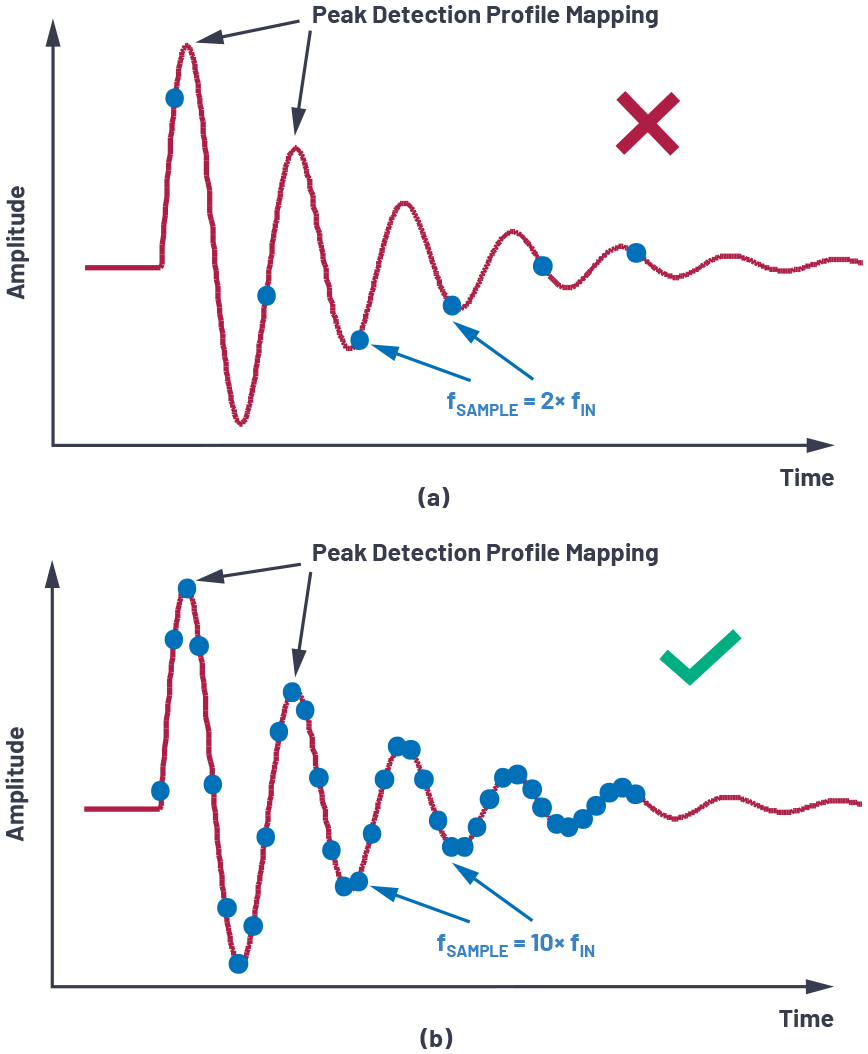

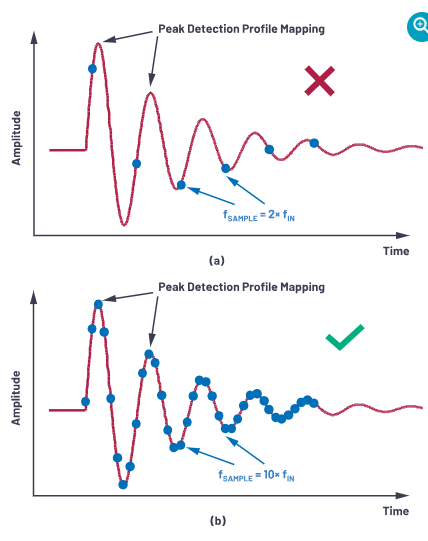

有少数一些应用,例如频率谐波分析或时域分析,其需要的采样速率比输入带宽高出好多倍。过采样速率的一个例子是冲击检测环境中瞬态信号的时域分析,如图1所示。如果这种信号的采样速率是奈奎斯特采样速率,我们将无法了解信号的全貌。拥有更多的采样点可以更忠实地重建和分析信号。

图1.瞬态信号的时域分析:(a) 奈奎斯特采样速率,(b) 过采样速率

可变采样速率

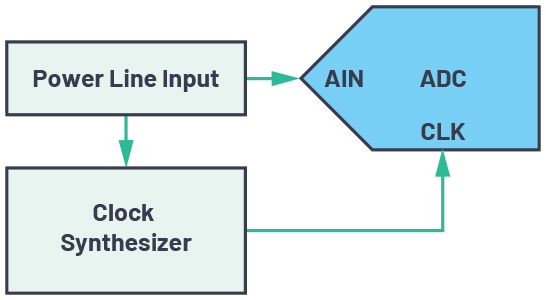

某些应用(例如相干采样)要求以良好的分辨率根据模拟输入频率调整输出采样速率。电力线监测就是这种应用的一个例子,需要相干采样来满足IEC 61000-4-30规定的A类电能质量计量要求。这些标准的精度要求决定了采样速率需要跟踪输入线路频率漂移。在这些应用中,电力线上的时钟频率合成器电路产生ADC的输出数字数据采样时钟,如图2所示。

图2.可变采样速率:电力线质量监测

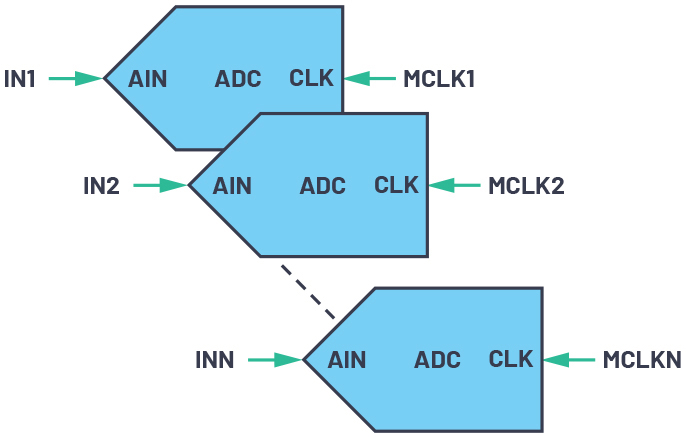

多采样速率

在检测和分析宽范围且不同类型的模拟输入的多通道应用中,例如示波器或数据采集应用,每个通道的采样速率可能不同。在这种情况下,平台中使用的ADC应该能够灵活地支持多采样速率。

图3.多采样速率应用

因此,数字数据采样速率要求因应用而异,并不存在一种万能的采样速率。所以,面向广阔市场的ADC需要支持宽范围的可编程数字数据采样速率。

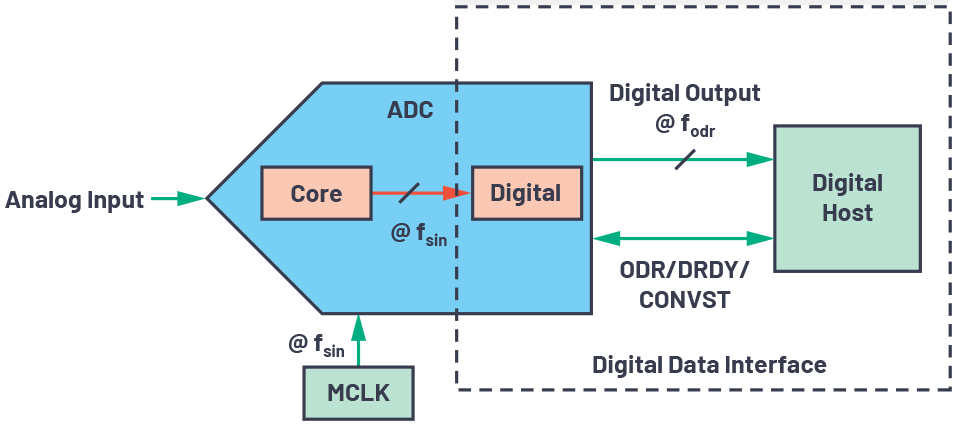

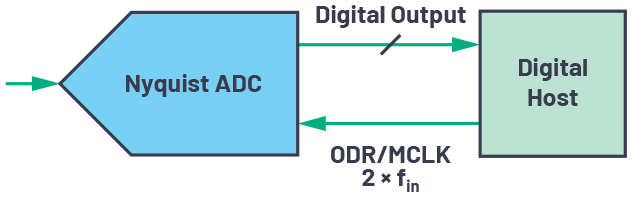

图4展示了一个具有外部数字主机的广义ADC数字数据接口。需要注意的是,本文中讨论的数字数据接口不包括器件配置控制接口,如SPI或I2C。

图4.广义ADC数字数据接口

核心ADC利用速率为fsin的采样时钟对模拟输入采样,如图4所示。在大多数数据手册中,输入采样时钟本身一般表示为MCLK。最终数字输出数据的采样速率为fodr。通常,这些引脚在数据手册中标记为ODR、DRDY或CONVST时钟。本文使用ODR时钟这个总称来表示数字输出数据时钟。

ADC核心的采样速率fsin取决于ADC架构。数字输出数据速率fodr取决于外部数字主机的数据接口要求。在大多数ADC信号链应用中,fsin和fodr可以具有不同的值并且不相关。因此需要进行采样速率转换,将ADC核心的fsin数据映射为fodr的数字输出数据。以下部分将讨论众所周知的ADC架构(如奈奎斯特ADC和过采样ADC)中使用的传统采样速率转换技术。此外,我们将深入了解其他相关的数字数据接口要求。

奈奎斯特速率ADC中的采样速率转换

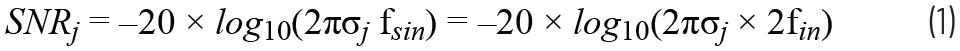

在奈奎斯特速率转换器中,ADC核心的采样频率是模拟输入带宽fin的两倍。此类别下最常见的例子是奈奎斯特速率SAR ADC,其输入和输出采样速率相同。因此,数字输出数据速率时钟ODR可以复用为ADC核心采样时钟MCLK。在SAR ADC数据手册中,数字输出数据时钟表示为CONVST或DRDY。但如前所述,本文将所有这些时钟统称为ODR时钟。ODR和MCLK组合可简化数字数据接口,如图5所示,仅需一条时钟布线。由于时钟由外部时钟源或外部数字主机提供并控制,因此ADC由外部提供时钟。这意味着ADC是在外部托管模式下运行。

图5.托管模式中奈奎斯特速率转换器的简化数字数据接口

根据应用要求和模拟输入带宽,很容易调整采样速率fodr。通过调整fodr,我们还能调整ADC核心的采样时钟速率fsin。另一个优点是,当调整fodr时,整个ADC的功耗也会线性地调整。这种简化的数字数据接口还有许多其他延伸的好处,其中一个是多通道应用中易于同步。

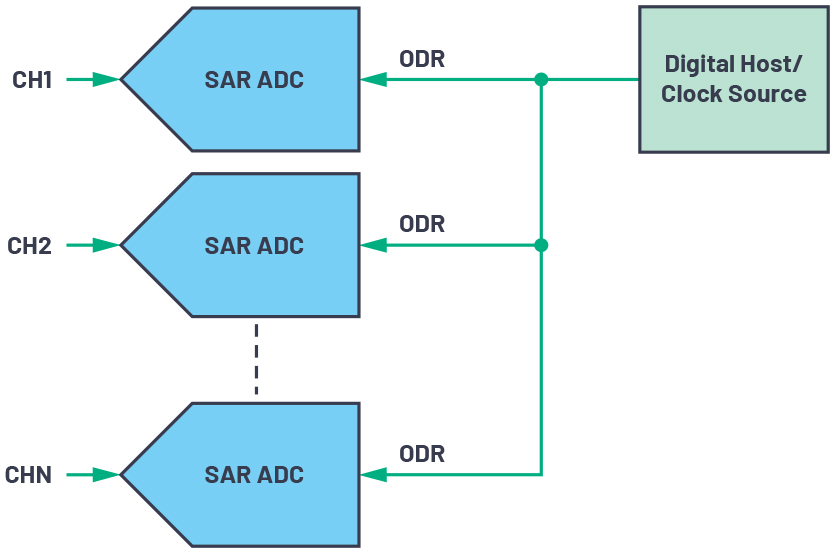

易于同步

在单通道ADC应用中,提供给ADC的本地时钟会固有地将数字数据与给定时钟同步。在多通道ADC应用中,挑战是要保证多个模拟输入的同步采样,以及数字数据与ODR时钟边沿同步以进行进一步数字处理。多通道同步应用有很多广为人知的例子,例如音频应用,其中左右通道具有特定的同步要求。另一个典型例子是监测电网中的各种电力线。在每条电力线内部,电压、电流和功率输入测量需要同步。利用奈奎斯特速率ADC,如图6所示,通过共享ODR时钟并对其路由进行良好规划,可以轻松实现多通道同步。规划良好的路由可以确保ODR时钟以相同延迟传播到每个ADC,并提供尽可能好的通道同步。

图6.简化奈奎斯特速率采样速率转换器中的同步

简化的数字数据接口是奈奎斯特速率转换器的一个重要优势。下面讨论其无法胜任的一些数字数据接口挑战。

奈奎斯特速率控制的局限性

噪声调整

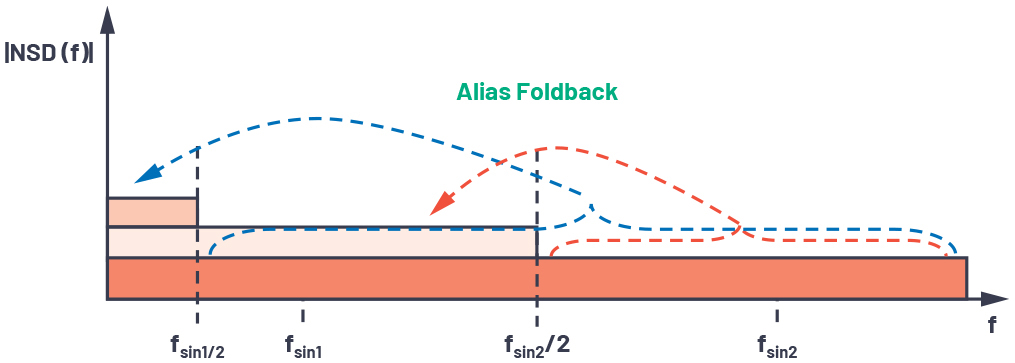

在基于应用的模拟输入带宽的奈奎斯特速率转换器中,可以轻松调整数字数据时钟。时钟调整可带来功耗上的优势,但由于所谓混叠折返现象,ADC噪声会增加。奈奎斯特采样准则的延伸是,任何超出奈奎斯特频率的信息都会折返或混叠回到目标频带。ADC的模拟输入会有大量来自信号源和输入模拟电路的干扰信息或噪声,其延伸到非常高的频率。ADC采样导致任何超过fsin/2的输入噪声折返,使得目标输入带宽中的噪声增加。如图7所示,随着采样速率降低,会有更多这样的外部噪声折返,从而增加ADC输出中的噪声。

图7.输入噪声折返与采样频率的关系

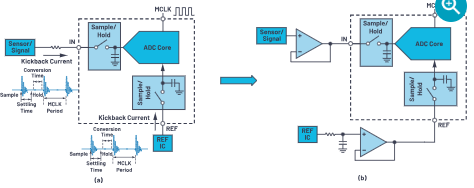

时钟时序约束

对于SAR ADC,模拟输入采样时钟需要两个阶段,如图9a所示。一个是采样阶段,其中ADC的输入采样电容对模拟输入充电;另一个是转换阶段,其中该采样数据被数字化。为了获得尽可能好的ADC性能,ADC的采样电路一般存在最短采样时间要求。因此,生成此时钟的外部数字主机或时钟源需要遵守这些时序约束。

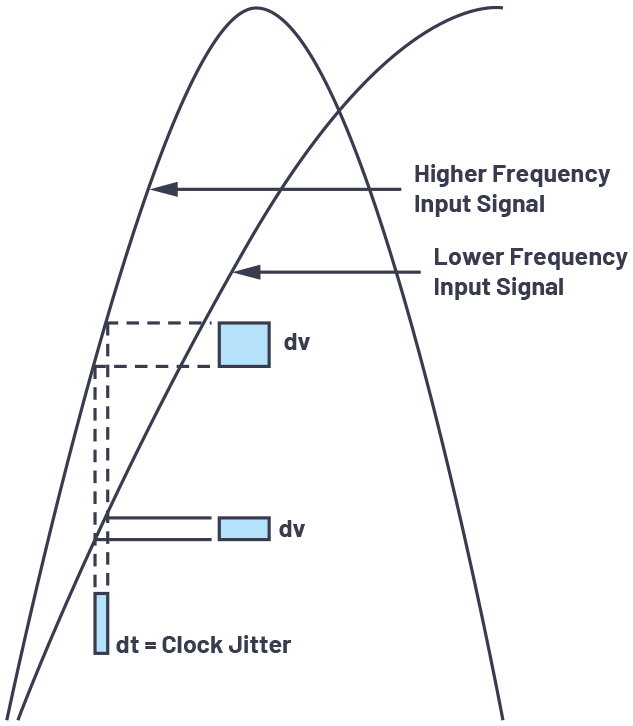

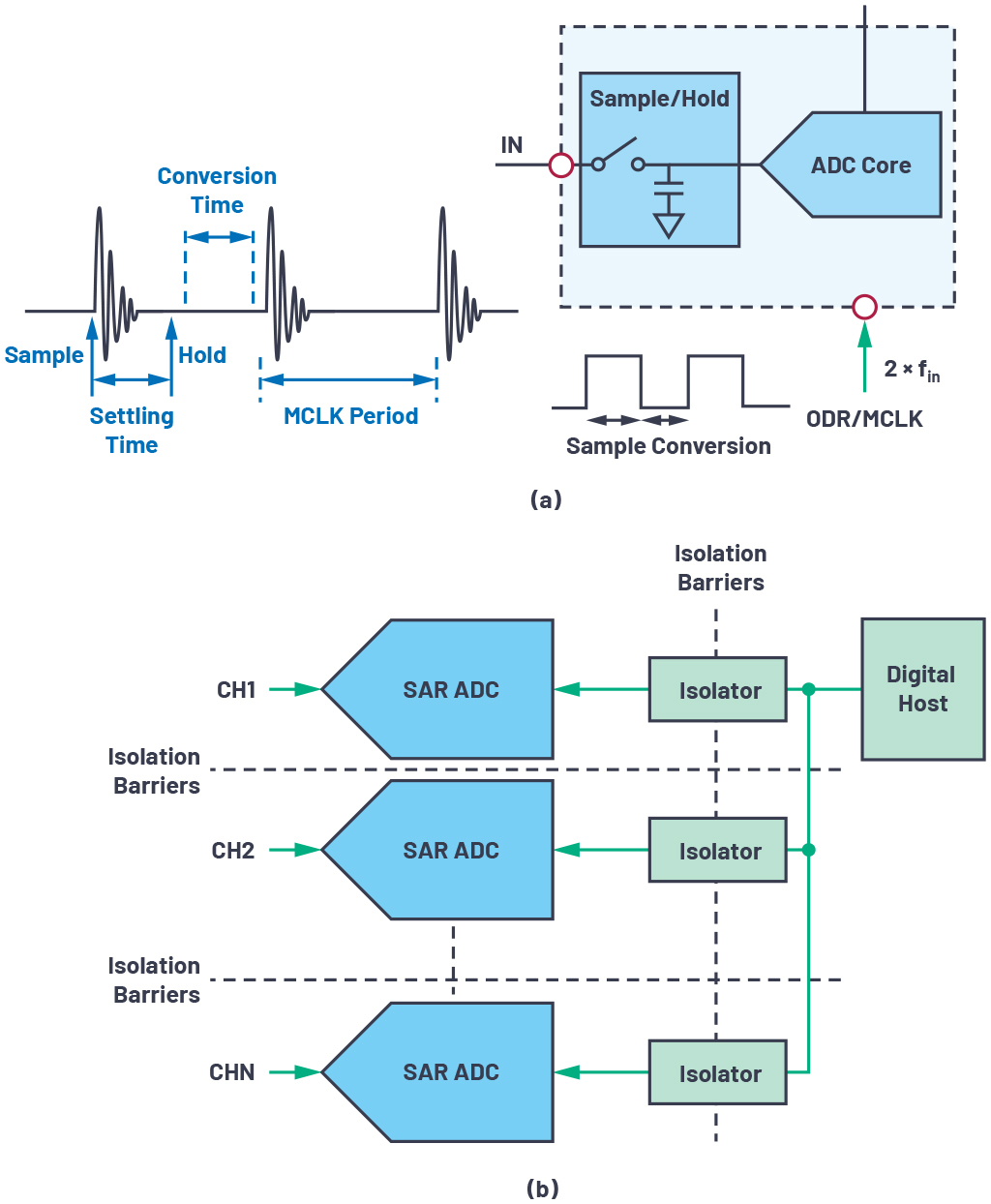

时钟抖动

应用电路板上的时钟路由对时钟源的电源噪声或与电路板上的其他信号耦合敏感,因为该噪声会增加时钟边沿的不确定性。时钟边沿的不确定性被称为抖动,采样时钟上有多种类型的时钟抖动会影响ADC的性能。最常见的是周期间均方根抖动,其增加了模拟信号采样点的可变性,导致性能下降,如图8所示。有关均方根时钟抖动对ADC性能的影响的更多详细信息,请参阅相关文章2。

图8.时钟抖动引起模拟输入采样点的不确定性

总结一下,时钟抖动导致ADC数据的误差增加可以量化为信噪比(SNR)的降低:

其中σj为均方根抖动。

当数字主机或时钟源的噪声很高时,式1意味着要达到所需的SNRj,我们要么限制输入带宽,要么采用额外的技术来滤除时钟噪声。

时钟抖动是多通道应用的一个更严重挑战,平衡同步和长时钟布线引起的抖动增加需要良好的时钟架构规划3。在这种情况下,需要采取适当的隔离和缓冲措施以确保ADC具有低噪声时钟。隔离可利用常见的数字隔离器实现,但需要增加设计复杂度和功耗方面的预算。

图9.奈奎斯特速率转换器数据接口的局限性:(a) 时钟时间约束(b) 多通道应用中的隔离要求

了解奈奎斯特速率ADC中的采样速率控制之后,我们看一下过采样ADC中使用的采样速率控制技术。

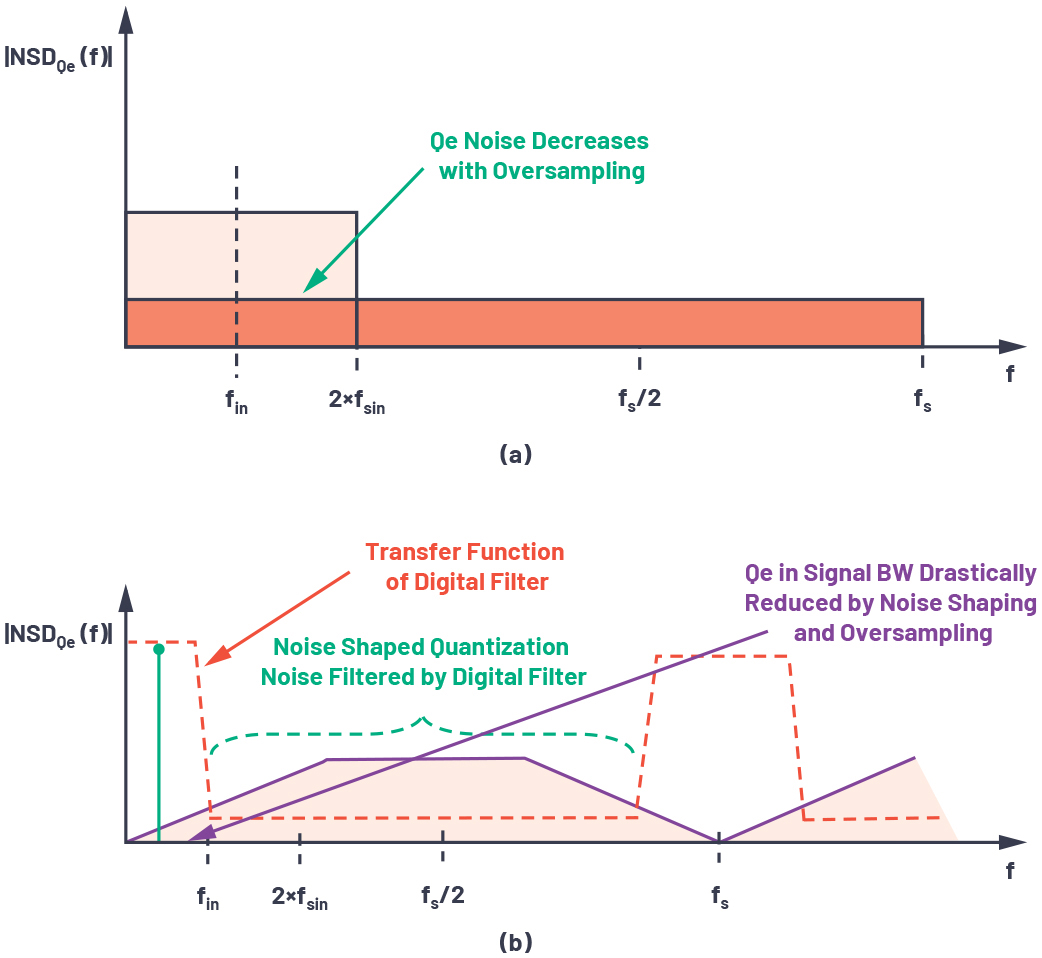

过采样ADC中的采样速率转换

如本系列之前的文章所述,对连续时间信号进行采样和数字化会有信息损失,并且会在采样输出中引入量化噪声。有一类ADC遵循这样的原则,即样本数越大,精度越高,量化噪声误差越小。因此,其模拟输入采样速率高于奈奎斯特采样速率,这被称为过采样。一些新型精密SAR ADC使用这种过采样技术,被称为过采样SAR ADC。图10a显示了过采样SAR ADC的噪声优势。另一类使用过采样概念的ADC是Σ-Δ型ADC4,其量化噪声Qe被进一步整形并向外推出,以提高目标输入带宽中的性能。图10b显示了Σ-Δ型调制器的量化噪声的噪声整形特性。在数学上,采样频率为OSR × fodr/2,其中OSR为过采样率。

图10.(a) 过采样SAR ADC的频谱,(b) Σ-Δ型ADC的频谱

如果直接将核心ADC的过采样数据与外部数字主机接口,那么后者将要接受许多冗余信息,导致过载。此外,在某些情况下,主机可能不支持这种高数字数据速率传输所需的严格时序约束,而且还会导致高功耗。因此,最优方式是仅提供目标输入带宽中的性能优化数据。这意味着,输出数字数据速率应降低或抽取到奈奎斯特速率(2 × fin),或奈奎斯特速率的几倍,具体取决于应用需要。因此,需要一种采样速率转换器来将ADC核心数据的高采样速率fsin映射为所需的fodr。

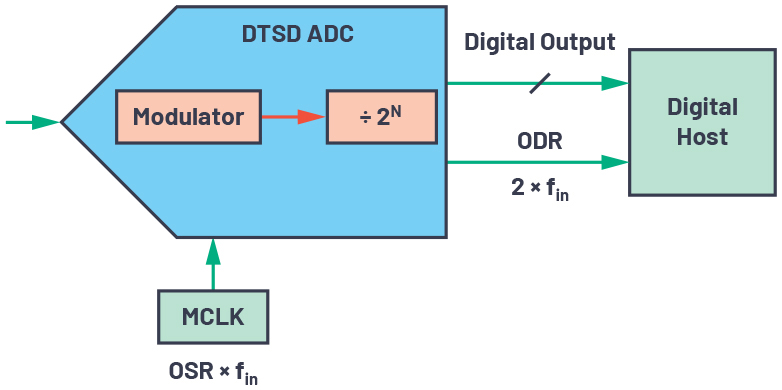

有一种称为抽取的传统数字采样速率转换技术,它能以2N的倍数滤波和抽取核心ADC数据,如图11所示。向ADC提供称为MCLK的输入采样时钟。所需的数字输出数据采样速率(ODR/DRDY)时钟——其为MCLK的分频版本——作为输出提供。基于所需的抽取率,通过设置N来实现分频比。对于fodr编程,为了获得更精细的分辨率,MCLK也可以根据应用的输入带宽要求进行调整。观察过采样ADC的数字数据接口,ODR时钟由ADC给出和控制。这意味着ADC提供该时钟,在主机模式下其名称为ADC。

图11.离散时间Σ-Δ(DTSD) ADC的数字数据接口

因此,将抽取用作采样速率转换技术时,ADC能以较低输出数据速率提供高性能数字数据。但是,这种技术也有自己的局限性。

使用抽取控制采样速率的局限性

非线性噪声、功耗调整

在可变速率应用中,抽取率和MCLK两者或其中之一可以调整。当仅提高抽取率时,fodr降低,噪声随着数字滤波器滤除更多量化噪声而降低。只有数字滤波器的功耗线性降低。如果像在SAR ADC中讨论的那样降低MCLK,则整个ADC的功耗会线性降低,但噪声会因为混叠折返而增加。

许多系统同时调整ADC的MCLK和抽取率来实现宽范围的ODR,但这种方法可能导致测量噪声性能或系统功耗性能发生不希望的阶跃变化。

时钟抖动

由于输入采样时钟频率fsin更高,因此过采样ADC对时钟抖动的敏感性比奈奎斯特速率SAR ADC更高,如式1所示。所以,时钟源和MCLK的时钟路由应基于应用容许的抖动噪声来规划。无论单通道还是多通道应用信号链,应用电路板上都会有许多切换信号在运行。来自这种高噪声信号的耦合会提高MCLK上的时钟抖动。因此,为了获得最优ADC性能,需要利用数字隔离器来满足MCLK的隔离需求。这种额外的设计规划会带来面积和功耗方面的成本。如前所述,为了让fodr编程具有更精细的分辨率,MCLK也会调整。然而,具有所需fsin值和抖动性能的MCLK时钟源可能很有限。

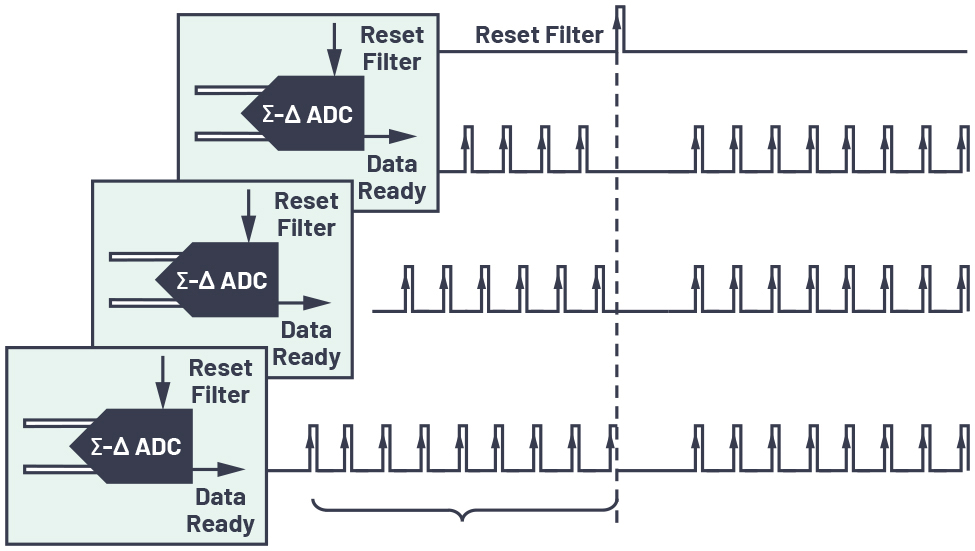

同步

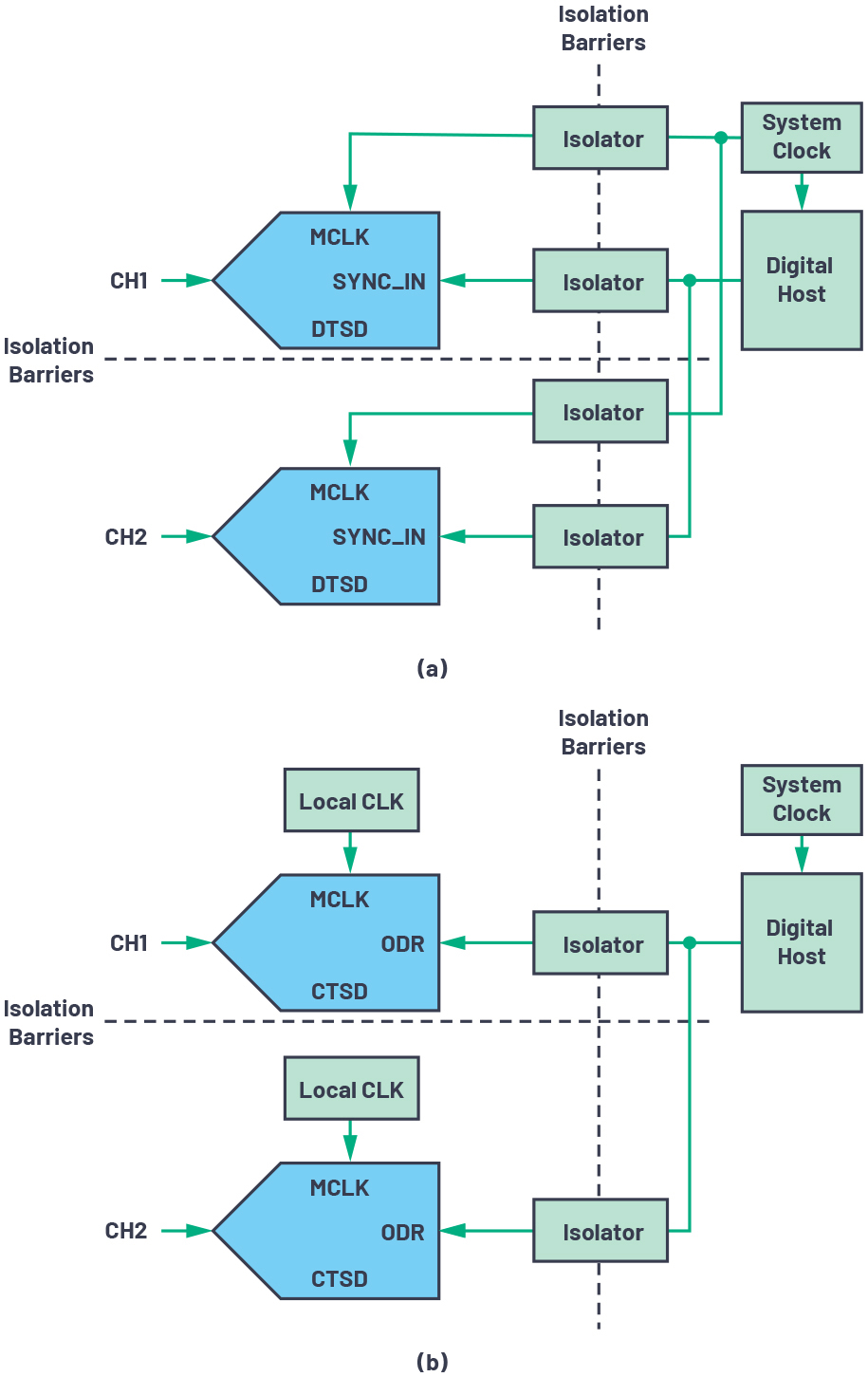

实现同步是过采样ADC的另一个挑战。通常,Σ-Δ型ADC中提供一个称为SYNC_IN的额外引脚用于同步。SYNC_IN引脚的触发会启动对模拟输入的同步采样以及抽取滤波器的复位。经过数字滤波器建立时间之后,数字输出数据是同步的。数字滤波器建立期间的数字输出数据是中断的,如图12所示。它还假设,所有ADC的MCLK和SYNC_IN命令是同步的。在高采样速率时钟上实现这种同步,特别是在有隔离器或频率合成器的情况下,会是一个巨大挑战。一种致力于解决数据中断和同步挑战的系统解决方案是时钟频率合成器电路,例如PLL,它会为所有通道生成同步的MCLK。

图12.发生数据中断的DTSD ADC中的同步

快速总结一下,当触发SYNC_IN引脚时,PLL环路启动与参考时钟的时钟同步。在PLL建立期间,MCLK速率会调整,使得在建立结束时,输入ADC采样边沿和ODR时钟边沿同步。有关该解决方案的原理和细节,请参阅“同步关键分布式系统时,最新Σ-Δ ADC架构可避免数据流中断”5。

图13.基于PLL的DTSD ADC同步解决方案

要点是,与SAR ADC相比,Σ-Δ型ADC或过采样SAR ADC的同步多出了板载电路、PLL或时钟频率合成器要求,这会增加设计复杂性和功耗。ADI公司探索了另一种新颖的技术,称为同步采样速率转换,它能在一定程度上帮助化解同步挑战。

同步采样速率转换(SRC)

对于已讨论的简单抽取的若干挑战,一种解决方案是使用同步采样速率转换6。SRC的优点是抽取率可以是fsin的任何整数或小数倍,从而可以更精细地控制fodr。ADI探索了该技术,并将其与AD7770中的精密DTSD转换器配对使用。有关SRC的更多细节,请参阅AD7770的数据手册或参考资料。

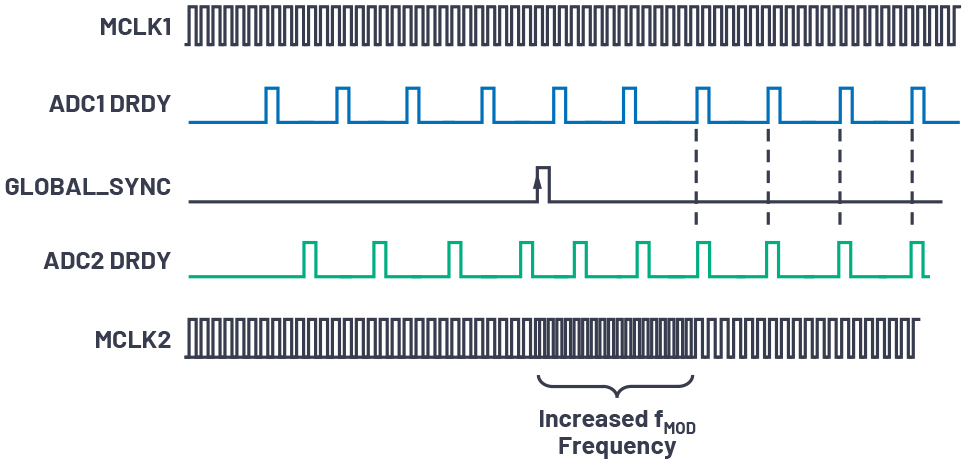

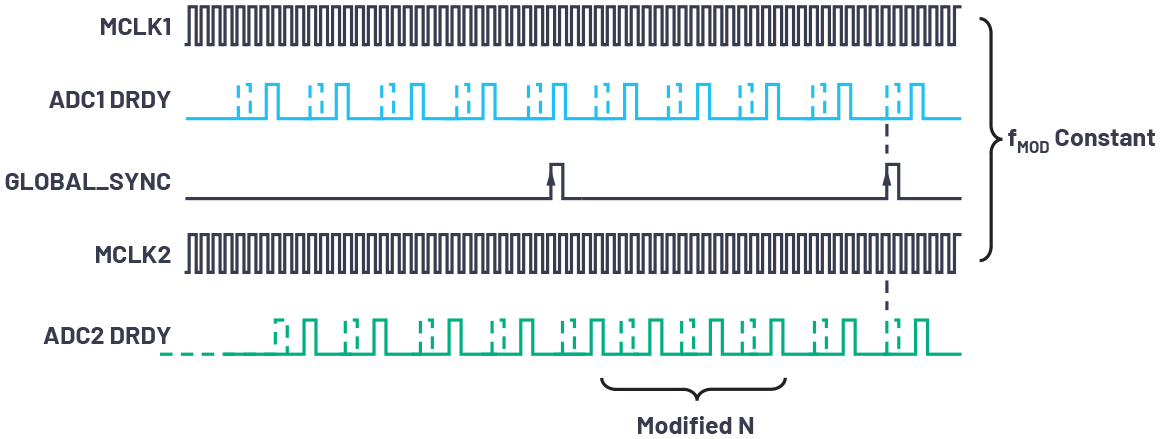

重点是,SRC中能以精细分辨率对fodr进行编程,因此同步变得更容易。例如,抽取率能以非常精细的步进变化,而无需调整外部MCLK。因此,当触发SYNC_IN时,通道将会同步,如图14所示。

图14.使用SRC实现多通道同步

在不调整MCLK的情况下实现更精细的fodr,可以克服简单抽取技术的大多数局限性。SRC也有自己的局限性和挑战需要克服。

SRC的局限性

SRC并未解决让所有通道具有相同MCLK的同步挑战。

时钟抖动/同步

在MCLK抖动方面,SRC具有与简单抽取采样速率控制相同的局限性。ADC性能对高fsin引起的时钟抖动的敏感性,需要通过MCLK的隔离栅或噪声滤波电路来解决。在多通道应用中,由于MCLK要路由到多个ADC通道,因此这一挑战的难度进一步加大。为了实现同步,MCLK和SYNC_IN引脚信号需要同步,如图16a所示。挑战在于,所有时钟同时到达ADC,与时钟到PCB的距离和隔离栅可能造成的延迟相关。需要建立包括隔离栅和路由架构在内的精心设计的时钟方案,以确保所有ADC通道经历同样的延迟,包括路径中的隔离器。

接口模式

到目前为止,所讨论的数字数据接口是主机模式和托管模式,其与ADC核心架构相关。例如,奈奎斯特速率ADC的数字数据时钟由外部时钟源或数字主机控制并提供。因此,它们只能被设置为托管模式。过采样ADC提供并控制外部数字主机的数字时钟。因此,它们只能被设置为主机模式。由此可见,上面讨论的所有采样速率控制技术存在一个普遍的局限性,那就是不能独立地规划数据接口。

对于大多数数字数据接口挑战,一种解决方案是将MCLK时钟域和ODR时钟域解耦。因此,ADI公司重新引入了新颖的异步采样速率转换技术,使得ODR时钟和数据接口时钟相互独立,从而打破了ADC核心架构长久以来的障碍,ODR时钟的选择和控制不再受限。

异步采样速率转换

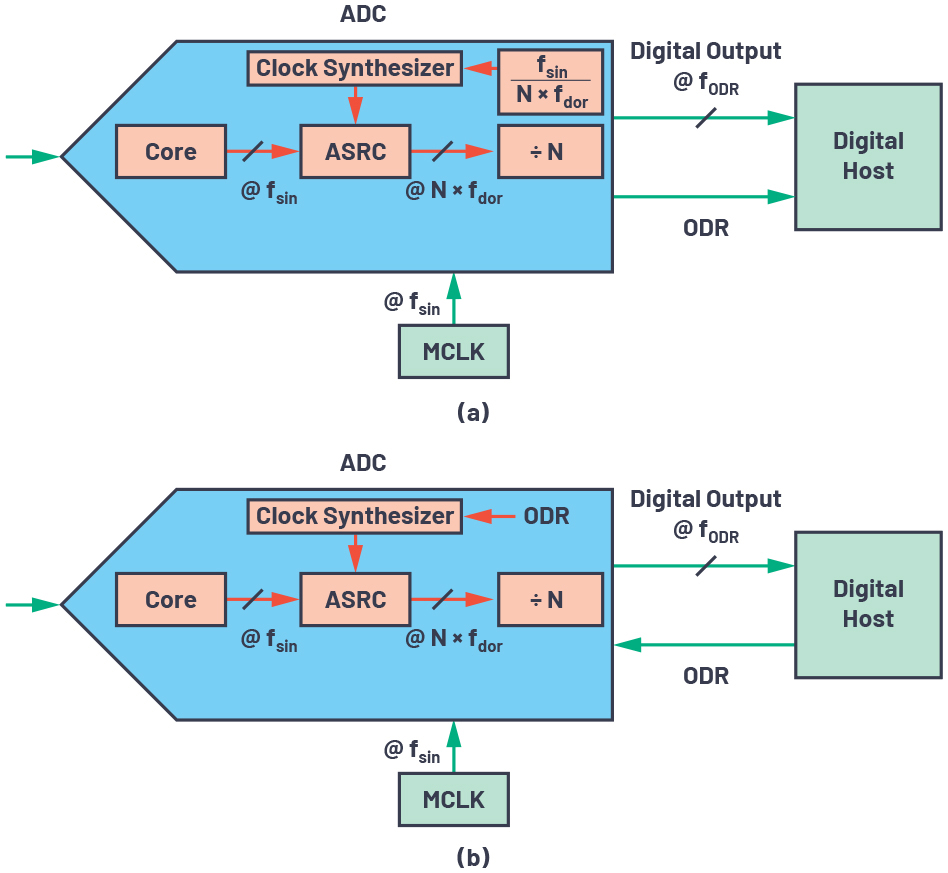

ASRC在数字域中以fsin对核心ADC数据重新采样,并将其映射到任何所需的输出数据速率。ASRC可以被认为是能够实现任何非整数抽取的数字滤波器。然而,为了实现优化的性能、面积和功耗,应由ASRC处理小数抽取,然后由一个简单的抽取滤波器来处理整数抽取,如图15所示。ASRC对ADC核心数据重新采样,并以fsin/N × fodr抽取数据。ASRC的输出数据速率为N × fodr。同时,抽取滤波器得到所需的÷N抽取。

在某种形式的ASRC实现中,系数fsin/N × fodr可以由信号链设计人员根据ADC的fsin、所需fodr和从ADC上实现的抽取滤波器获知的N来设置。这类似于设置SRC中的抽取率,不同点是抽取比率可以是无理数比率,并且支持非常精细的分辨率。在这种情况下,如同在SRC中,ODR时钟与MCLK同步,并且是在片内通过MCLK分频而产生的输出。

另一种形式的ASRC实现是,ODR时钟由外部时钟源或类似于奈奎斯特速率转换器的数字主体提供。在这种情况下,ASRC具有内部时钟频率合成器,它会计算fsin/N × fodr比率,并为ASRC和抽取滤波器产生所需的时钟。ODR无需与MCLK同步,可以独立设置为任何采样速率。

图15.ASRC实现:(a) 设置比率,(b) 片内计算比率

因此,无论何种形式,ASRC技术都支持信号链设计人员以细粒度设置fodr,并打破长久以来的限制,即fodr以输入采样速率的整数或小数比为限。结果是,ODR时钟的采样速率和时序要求现在纯粹属于数字接口的功能范围,并且完全与ADC的输入采样频率无关。这两种实现形式的任何一种都展现了ASRC的优势,信号链设计人员因而得以简化数字数据接口设计。

ASRC的价值主张

MCLK和ODR时钟解耦

在任何一种实现形式中,由于能以更精细的分辨率设置/调整fodr(调整幅度可以是几分之一赫兹),因此ASRC允许独立选择MCLK和ODR时钟速率。MCLK速率fsin可以根据ADC性能和时钟抖动要求来选择,而ODR时钟fodr可以根据数字数据接口要求来实现。

时钟抖动

在奈奎斯特速率转换器和过采样ADC中,我们都看到MCLK和ODR相关,需要调整MCLK以实现更精细分辨率的fodr。然而,能够匹配任何fsin速率的MCLK之时钟抖动要求的时钟源是有限的。因此,需要权衡MCLK抖动引起的ADC性能降低和fodr的可能分辨率。就ASRC而言,可以选择MCLK源以提供最佳的时钟抖动,因为fsin的值可以独立选择,与ODR无关。

接口模式

ASRC让MCLK和ODR的时钟速率不再相关,因此接口模式的选择有一定的自由度。任何具有ASRC后端的ADC都可以独立配置为主机或托管外设,而不用考虑ADC核心架构。

同步

在先前讨论的多通道同步技术中,MCLK时钟路由有严格的要求。需要规划隔离栅和时钟架构以满足时钟抖动和同步要求。现在,每个通道的MCLK源可以是独立的,如图16b所示。在主机工作模式下,抽取率可以独立设置以实现同步。在托管模式下,如图16b所示,ODR可以共享和同步。由于ODR时钟的速率较低且只是一个数字数据选通时钟,因此它没有像MCLK那么严格的抖动要求,故而可以放松对隔离栅或时钟路由的严格要求。

图16.(a) 使用SRC的Clock和SYNC_IN分配(b) 利用ASRC简化时钟和同步

总之,ASRC开辟了创新和简化与外部数字主机接口的探索之道。此外,MCLK可以是独立的,因而它非常适合与CTSD ADC配对使用。

ASRC与CTSD ADC配对

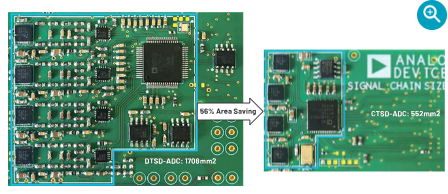

CTSD ADC核心对过采样和噪声整形的Σ-Δ概念也有效,同时提供电阻输入、参考驱动和固有混叠抑制等架构优势。这些特性大大简化了模拟输入前端设计。如第2部分所讨论,由于核心ADC环路是一个连续时间系统,因此将环路系数调整为数据手册中指定的固定输入采样速率。

CTSD ADC的局限性是MCLK不能像在DTSD或SAR ADC中那样调整。如果CTSD ADC与SRC配对,则ODR将是该固定采样时钟的函数。这会限制CTSD ADC的使用范围。应用需要的ODR可以是该固定fsin的无理数比。此外,CTSD ADC要求该MCLK精确且具有低抖动,以实现优化ADC性能。例如,精度要求可以是±100ppm左右,均方根抖动为10 ps。因此,MCLK将需要一个规划良好的时钟架构,以保证多通道应用中的抖动噪声较低。MCLK是高频时钟,因而挑战难度加大。

ASRC能让MCLK和ODR解耦,非常适合应对CTSD ADC架构的局限性。MCLK时钟源可以在本地且靠近ADC,避免长时钟布线及耦合到其他信号,导致抖动噪声增加。因此,ASRC与CTSD ADC的组合带来一类新的ADC,其既有CTSD ADC的架构优势,又能克服固定、低抖动MCLK的局限性。

结论

ASRC让信号链设计人员可以独立地以粒度选择所需的输出数据速率。另一个优点是,由于输入采样时钟和ODR时钟解耦,多通道应用中可以有效地规划数字隔离。自由地配置数据接口而不用考虑核心ADC架构,是对信号链的另一种简化。本文有助于了解相比于传统采样速率转换,ASRC给数字数据接口带来的各种优点和简化。一般而言,ASRC可以与任何ADC核心架构配对,但与CTSD ADC配对可以简化模拟输入端及数字数据端的完整信号链设计。明确ASRC的需求和价值主张之后,请留意后续文章,我们将深入阐述ASRC的概念及其构建模块。这些细节有助于信号链设计人员了解与ASRC相关的性能指标,并在应用中发挥其优势。

参考资料

1Walt Kester。“MT-002教程:奈奎斯特准则对数据采样系统设计有何意义。”ADI公司,2009年。

2Derek Redmayne、Eric Trelewicz和Alison Smith。“设计笔记1013:了解时钟抖动对高速ADC的影响。”凌力尔特,2006年。

3Pawel Czapor。“Σ-Δ ADC时钟——不只是抖动。”模拟对话,第53卷第2期,2019年4月。

4Michael Clifford。“Σ-Δ型ADC拓扑结构基本原理:第1部分。”ADI公司,2016年1月。

5Lluis Beltran Gil。“同步关键分布式系统时,最新Σ-ΔADC架构可避免数据流中断。”《模拟对话》,第53卷第3期,2019年9月。

6Anthony O’Shaughnessy和Petre Minciunescu。“AN-1388:使用AD7779 24位同步采样Σ-Δ型ADC实现电能质量测量的相干采样。”ADI公司,2016年2月。

AD1893数据手册。ADI公司。

-

adc

+关注

关注

100文章

7950浏览量

556942 -

数据接口

+关注

关注

1文章

95浏览量

19456 -

多速率转换

+关注

关注

0文章

2浏览量

5803

发布评论请先 登录

CTSD ADC:如何改进精密ADC信号链设计

FPGA与ADC数字数据输出的接口

利用异步采样速率转换简化数字数据接口

CTSD精密ADC:利用异步采样速率转换(ASRC)简化数字数据接口

CTSD精密ADC:轻松驱动ADC输入和基准电压源,简化信号链设计

CTSD精密ADC—利用异步采样速率转换(ASRC)简化数字数据接口

CTSD精密ADC—利用异步采样速率转换(ASRC)简化数字数据接口

评论