按正常的思维逻辑来说,高速信号的走线层一般都是0.5oz或者1oz,如果让你亲眼见到一个高速信号走到厚铜上,你会不会很惊(jing)喜(ya)!

高速信号为什么一般都会走在0.5oz的信号层上呢?抛开性能的要求不说,从加工的角度来看,0.5oz的层对于走线蚀刻,PP的流胶都会相对比较稳定,而且对于设计来说,走线和走线之间的距离要求也不会过于严格,这样的话一般来说加工出来的阻抗就会比较稳定,偏差也不会太大。但是如果由于各种原因,走线走在了厚铜层上面,会发生什么事情呢?今天我们就给大家分享这样一个“百里挑一”的案例。

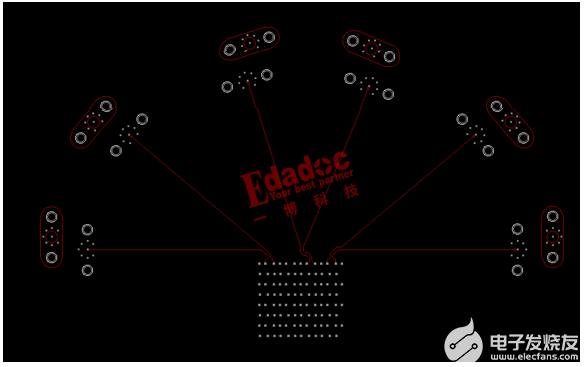

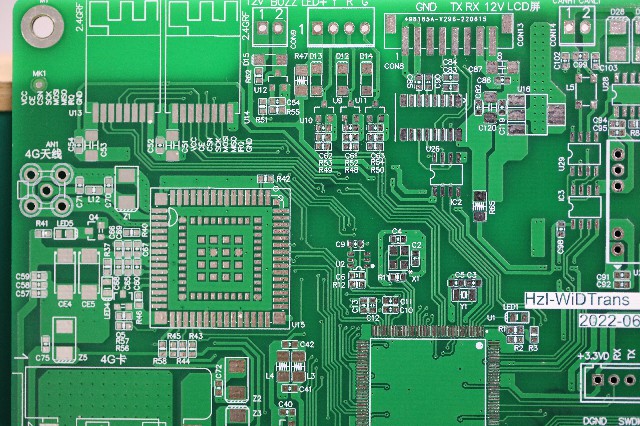

这是客户设计的一块高速连接器的测试夹具板,顾名思义,就是用来进行高速连接器的测试的。客户的这款自研连接器的目标速率是25Gbps,因此对于夹具的性能也要求能支持到至少20GHz的水平。其实这个项目的设计加工压接都是客户那边自己完成的,本来我们高速先生是看不到这个案例的,只不过这款夹具的性能很有问题,客户才来求助我们高速先生,希望能帮忙定位问题。下面是客户设计的测试夹具板,我们看到其中有一半的信号走线是在表层,通过SMA连接器连接到高速连接器。

原理和设计其实都很简单,但是问题在客户回板测试后就立马出现了。那就是表层线的阻抗居然过低!!!客户进行了阻抗测试,发现表层的单端线走线普遍都偏低,甚至有的只有42欧姆左右!

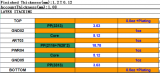

这让客户大为不解,按理说,链路比较简单,相邻很远的位置也没有走线的串扰,而且走线的线宽也没有很细,6mil的线宽很好去加工。这个案例交到高速先生这里后,我们也同样进行了阻抗测试,发现表层线的阻抗的确像客户测试的那样低!这个时候我们根据客户的设计叠层和走线进行了阻抗的计算,发现按照该叠层和线宽进行设计,阻抗的确能算到50欧姆。

那到底是走线的哪个因素出了问题呢?从肉眼上去看肯定是不能看出来的了。还好我司自己有板厂,因此我们能想到的方法就是让板厂进行切片,我们通过显微镜去看走线的实际结构!

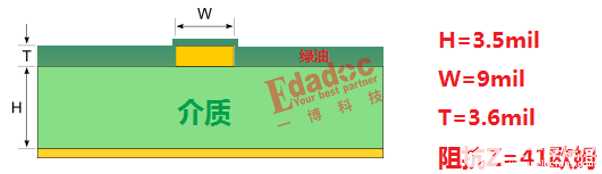

经过一番辗转之后,我们终于完成了对这块测试板的切片,果不其然,在这里我们找到了答案。我们对这些表层走线进行了横切面的测量,发现该表层走线的铜厚居然远远超出了我们的想象,它居然做到了3.6mil!!!

我们在表层线是使用0.5oz的基铜进行电镀,也就是我们经常说的0.5oz+plating,一般来说完成电镀后铜厚会在1.6mil左右。但是这个板子客户的板厂居然活生生的做成了3.6mil,高速先生要不是亲眼看到测试的结果,实在是难以置信!

而且还不仅如此,线宽也从设计的6.5mil做成了9mil,要不是板材和介质厚度还是对的,我们都觉得板厂是把这个项目当成了另外一个项目来做了。

然后我们根据切片测量到的数据再次进行阻抗的计算,计算出来的结果就和实际测试的阻抗结果很接近了。

这个案例其实很难理解客户找的板厂是怎么去加工的,我们通过铜厚的巨大差异来初步判断是板厂用了2oz的基铜进行电镀得到的3.6mil铜厚,另外也能看到走线也是被蚀刻得很不均匀。Anyway,这个案例再一次验证了微带线的加工的确存在很多不确定性的因素,它的阻抗控制肯定是比带状线更有难度的,所以我们如果要使用微带线去设计一些高速率,高精度的项目时一定要特别的注意哈!

-

连接器

+关注

关注

102文章

15922浏览量

145421 -

信号

+关注

关注

11文章

2902浏览量

79674 -

高速

+关注

关注

0文章

125浏览量

23867

发布评论请先 登录

揭秘PCB设计生死线:走线宽度、铜厚与温升如何决定电流承载力?

超厚PCB制造中常见的挑战

“局部厚铜”-电气新时代的动力基石

华秋DFM软件丨操作教程——工具菜单-阻抗计算篇

铜厚、绝缘层、结构……哪些因素影响铜基板价格?

高速PCB铺铜到底怎么铺

PCB叠层设计避坑指南

全面了解高速铜缆内部线和外部线

如何在超厚铜的信号层走高速线?

如何在超厚铜的信号层走高速线?

评论