在Vitis里面创建了一个LwIP工程,调试的时候发现,在BRAM里面运行正常,但如果改到DDR3内存里面运行,启动时就会卡死在sleep函数上。

于是建立了一个Hello World工程来检查,代码如下:

#include

#include

#include "platform.h"

int main()

{

int i = 0;

init_platform();

xil_printf("Hello World\r\n");

xil_printf("Successfully ran Hello World application\r\n");

while (1)

{

xil_printf("i=%d\r\n", i);

i++;

sleep(1);

}

cleanup_platform();

return 0;

}

用xil_prinf串口打印函数,编译后.text的大小为4944。将xil_printf全部替换为printf(替换后所有的\r可以省去),编译后.text的大小为70964。

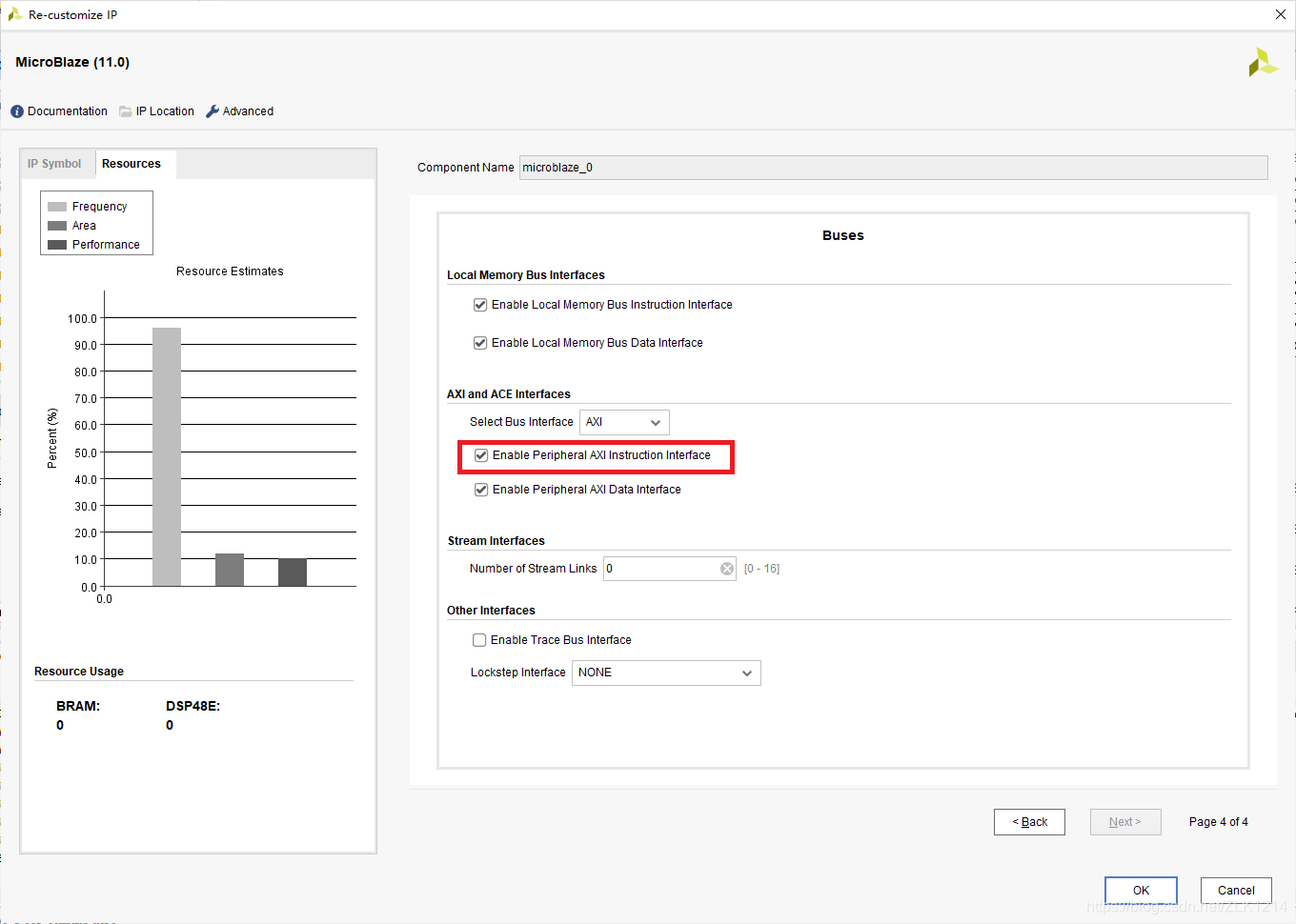

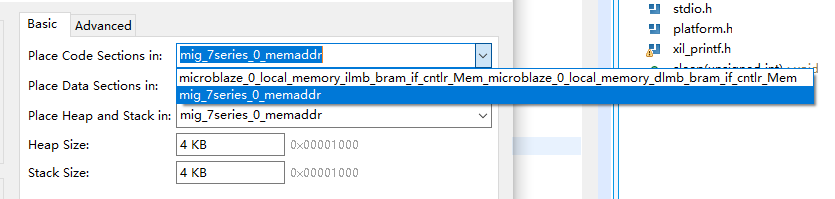

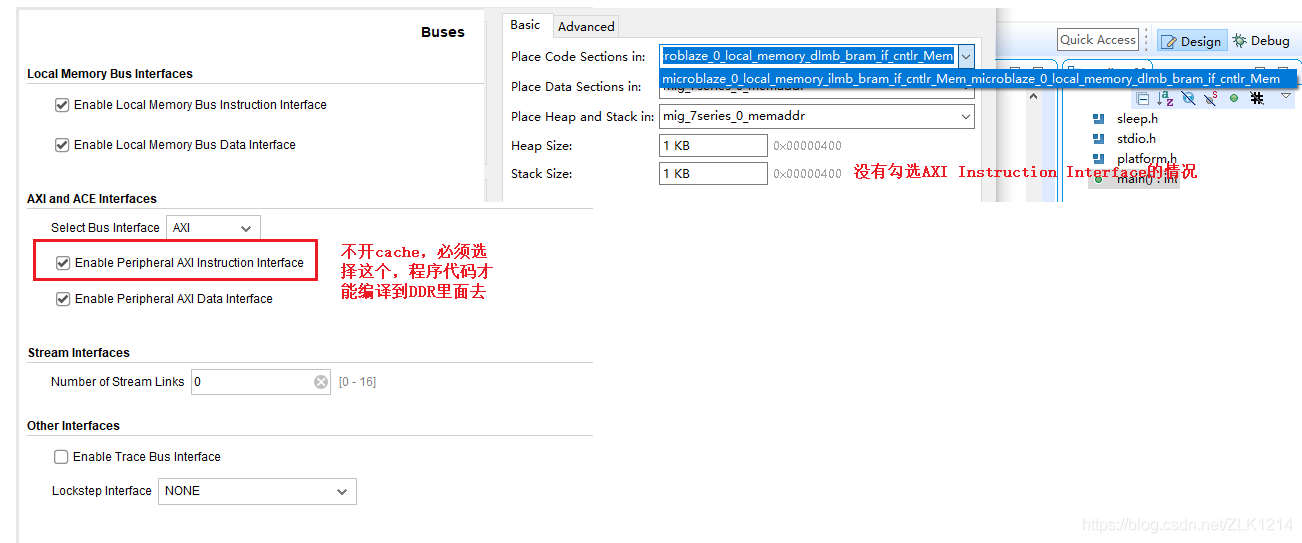

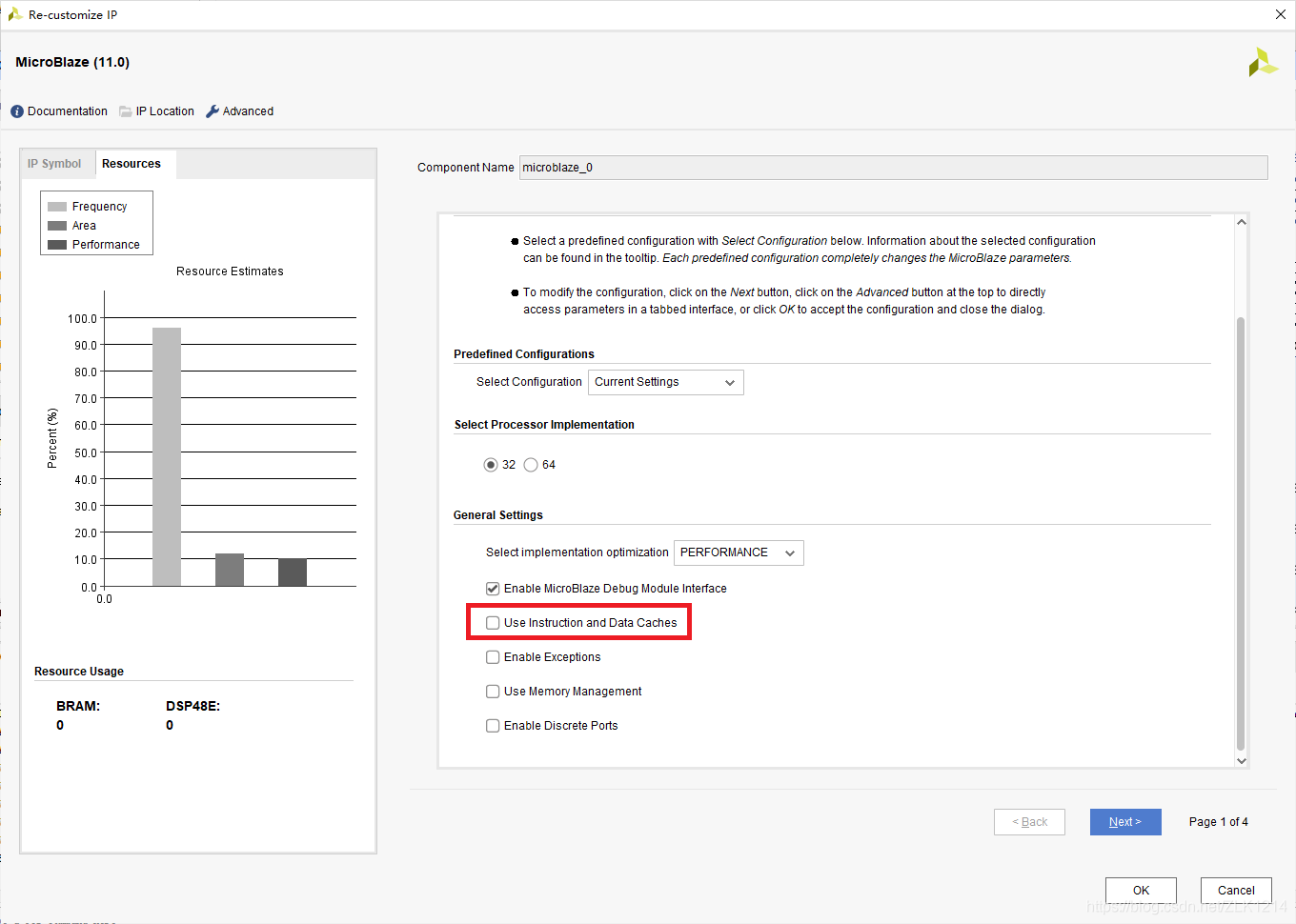

没有使能Instruction and Data Cache时,需要在MicroBlaze里面勾选Enable Peripheral AXI Instruction Interface,才能将程序放入DDR3内存中执行:

Code Sections就是程序代码的放置位置。

如果使能了Cache(勾选了Use Instruction and Data Caches),就可以不用勾选Enable Peripheral AXI Instruction Interface(勾不勾选,对sleep函数没有影响)。

测试后发现:

程序运行在DDR3中,开了cache,用printf:sleep无法使用

程序运行在DDR3中,开了cache,用xil_printf:sleep可以使用

程序运行在DDR3中,不开cache,用printf:sleep无法使用

程序运行在DDR3中,不开cache,用xil_printf:sleep无法使用

但是如果仔细看的话,会发现有些情况下sleep并不是完全卡死,而是过了好几分钟才返回,串口打印出下一个i的值。这说明sleep并不是无法使用,而是执行起来非常慢。

sleep函数内部是用汇编语句实现的,可能是放到DDR3里面执行的话,取指有一定的问题。放到BRAM里面则可以正常运行。

所以,如果程序很大,非要放到DDR3里面运行的话,那就最好不要使用sleep函数。可以自己修改sleep函数的代码,或者干脆自己重定义另外一个延时函数。

审核编辑:符乾江

-

Xilinx

+关注

关注

73文章

2192浏览量

129881 -

MicroBlaze

+关注

关注

3文章

68浏览量

22221

发布评论请先 登录

同系列性能更强!面向高性能 AI 应用,AXU2CGB-I 有何亮点?

AMD Vitis AI 5.1测试版发布

E203软核提高CPU时钟频率方法

在移植的时候发现卡死,为什么?

线程中调用rt_thread_mdelay()函数卡死的原因?怎么解决?

MicroBlaze处理器嵌入式设计用户指南

使用AMD Vitis Unified IDE创建HLS组件

STM32G473进行双bank升级的时候,进行FLASH的批量擦除回卡死是怎么回事?

STM32G473 flash擦除时程序卡死,为什么?

STM32G473 flash擦除时程序卡死的原因?

在Ubuntu16.04上从版本2020.1 OpenVINO™升级到2021.4.2之后不兼容怎么解决?

使用DLP3010LC GUI里面的Light Control里的Internal Patterns功能投影条纹图片,遇到的几个疑问求解

LDC1000里面配套的PCB线圈的电感值是多少?

使用AMD Vitis进行嵌入式设计开发用户指南

Xilinx Vitis 2020.1里面MicroBlaze软核的sleep函数卡死的问题

Xilinx Vitis 2020.1里面MicroBlaze软核的sleep函数卡死的问题

评论